目录

众所周知,一块电路需要正常工作,合适的外部供电系统肯定是必不可少的。对于TC264也是如此,如果我们需要我们的最小系统可以安全,稳定的工作,需要对我们外部的稳压电路进行合理配置。

PMU单元

简介

AURIX单片机电源控制系统叫做PMU(Power Supply and Control)单元,它负责对外部输入的电源进行控制调整,使得其能够达到片上所需的电压要求。下面是TC264D用户手册里对该单元组成的简单介绍:

PMU单元简介 在TC26x B-Step中实现了片上线性和开关模式电压调节器,从而使单电源供电成为可能。外部标称系统(EVR-external nominal system)电源可以是5v或3.3 V。有两个独立的并联嵌入式稳压器(EVR33和EVR13)从外部电源产生3.3 V和1.3 V的电源电压。当外部电源为5v或3.3 V时,EVR13稳压器可选择线性稳压(LDO)或开关电源稳压(SMPS)模式。EVR33稳压器是作为LDO稳压器实现的,仅在外部电源为5v的情况下才需要。

当然,根据选择的EVR模式,系统的实际功耗、电磁干扰要求和热约束;可能需要额外的外部组件,如mosfet、电感器和电容器。也可以在外部提供3.3 V和1.3 V的电源电压,从而确保符合传统电源的概念。

所有的电源和产生的电压都受到内部监控,以防止超调和基于可编程阈值的限电。如果违反了这些阈值,则会触发复位冷电源或向SMU提供警报。

在单个5v外部电源的情况下,端口将主要具有5v逻辑电平。然而,它可以运行部分端口域,即Flexport (P11.x),在3.3 V的逻辑级别,即使设备是由5v供电的。Flexport可以直接由5v外部电源提供,也可以由内部产生的3.3 V EVR电源提供。在这两种情况下,Flexport域的供应(VFLEX= 5v或3.3 V)的路由都是在外部完成的。而单个3.3 V外部电源(VEXT = VDDP3 = VFLEX = VDDM = 3.3 V)时,整个端口和模拟域的逻辑电平为3.3 V。

除模拟域(VAREFx和VDDM)外,所有内部电源均可由EVRs提供。模拟电源域与主EVR电源域分离,可以由单独的外部调节器或跟踪器提供。可以使用一个5VADC域的混合电源方案(VDDM / VAREFx = 5 V),其余系统运行在3.3 V电源上(VEXT = VDDP3 = 3.3 V)。

看完上面所述对PMU单元应该就有了一个基本了解。PMU单元最重要的就是EVR33和EVR13两个稳压器,它们负责把输入的单电源配置成单片机不同区域所需要的电压。

这里有一点需要注意:TC264D支持一组Flexport,即P11端口。这个端口的引脚可以区别于单片机其它引脚,在5V单电源输入时可以配置成单独的3.3V端口,但3.3V单电源时就只能和其它端口的电压类型保持一致了。

EVRx

EVRx简介 EVRx是对EVR33和EVR13的统称。EVR13可以将供电电压转换为内部模块需要的1.3V电压;而EVR33则可以将电压转换为3.3V。EVR13主要是为内核供电,包括片内RAM等;EVR33可以为FLASH模块、LVDS接口驱动、时钟电路、JTAG接口等供电。

此外,EVR33还能够驱动有限数量的非感性3.3 V外部负载,并可在配置为3.3 V端口的情况下提供Flexport。每个EVR构成一个数字调节器、一个pass 装置控制单元和一个电压反馈回路。通过电容器适当地缓冲器件输出,以处理负载瞬态,从而不违反工作电压限制。每个EVR可以通过HWCFG引脚单独禁用。每个EVR也可以通过受保护的寄存器来进入省电模式。EVR13和EVR33可以通过EVR13CON.EVR13OFF和EVR33CON.EVR33OFF位分别禁用。

EVRx可以设置为两种模式:SMPS(开关电源模式)和LDO(线性稳压)模式。其中EVR13用在外部电源5V或3.3V的情况下,可以配置为SMPS和LDO两种模式;EVR33则只工作在外部供电5V的情况下,而且只有一种LDO模式。

EVRx的供电模式一般取决于外部电源配置引脚,这些引脚如何配置及其之间的关系我们在之前的表格里已经给出,这里不再赘述。下面列出这些方案的电路拓扑:

LDO模式

先介绍一下LDO的原理,如图所示是一个简单的LDO内部拓扑示意图:

当使能信号给出之后,误差比较器开始工作。刚开始时Q1这个PMOS未导通,误差比较器的反向端无电压,误差存在比较器输出信号导通Q1管。随后Vout电压逐步上升,直到反向输入端得到的分压和Vref相等时,比较器切断Q1管。然后输出电压又下降,管子再次导通,然后再关闭,然后再导通……如此周而复始,管子实际上是在一定周期内维持了一个固定的导通角。因为外部存在着Cout电容进行缓冲,所以最终输出会稳定在Vref。

下面的电路就是芯片内部EVRx构成LDO模式情况的连线图,c,b,g,f 四种方式为内部EVR工作在LDO模式下。c表示的是5V单电源配合外置pass器件构成LDO;b表示的是5V单电源配合内置pass器件构成LDO;g表示的是3.3V单电源配合外置pass器件构成LDO;f表示的是3.3V单电源配合内置pass器件构成LDO。

上面LDO拓扑虚线框里的电路实际上就是在EVRx的主要电路。所以如b,f所示,EVR13(EVR33)外部不接mos只需接电容就可以直接构成稳压输出。但是这样输出的电流实际上很小,只能满足芯片基本的需求。为了让我们的芯片能够工作在更加稳定的状态,我们一般还是使用c,g这样的外置mos,这种情况下,内外相当于两个mos分别被控制并联输出,提高驱动能力。

SMPS模式

这种模式只有EVR13可以配置,在这种模式下,需要在外部配置相应的开关管,以及LC电路,如图所示。采用开关电源的降压型step-down拓扑结构,这种结构也称为BUCK电路。外部输入电压为5V或3.3V,经过降压产生1.3V的电压输出,输出电压到VDD引脚给内核供电。

BUCK型电路的原理很简单。开关管打开的时候,负载直接由电源供电,同时大电感进行储能;开关管关闭的时候,大电感释放能量,通过二极管续流通道继续给负载供电。这样平均周期里负载上的电压就会下降,而下降的幅度是靠开关管在单个周期内的导通时间决定的,也就是我们所称的占空比。

而我们使用的SMPS模式下配置的一组mos管实际上与上图基本完全一致,上臂的P-mos实际上等同于BUCK电路的开关管,而下臂的N-mos实际上等同于BUCK电路的二极管。实际上,这二者的驱动信号应该是接在一起的,即配置在SMPS模式时,VGATE两个脚输出的波形是一致的。当P-mos导通时,N-mos关断,电源供电;当P-mos关断时,N-mos导通,电感续流。

a,e表示的分别是5V单电源使用SMPS模式和3.3V单电源使用SMPS模式,可以发现他们的EVR13处接线都是一样的,所去别的仅仅是EVR33是否使用了LDO。

这里值得一提的是,SMPS情况下也不是一定需要EVR控制器来控制开关mos。还可以如图中所示,利用内置PID控制器进行降压调节。这种同步外部降压调节器的开关频率比内部调节器低得多,同时,其提供了一个缩放的同步时钟输出,并将其路由到外部引脚(P33.13引脚- DCDCSYNC输出)。

外部直接输入模式

这种方式是最简单的。d表示的是5V和1.3V直接外部输入;h表示的是5V,3.3V和1.3V均为外部输入。

供电方案选择

引脚总览

在之前对硬件配置引脚和基础配置引脚的介绍中,我们都提到了电源配置引脚有关的知识。在这里我们再说明一下:TC264所需连接的电源引脚如图所示,共有八组,它们分别如表格中所示:

| 电源引脚 | 接地引脚 | 范围 | 主要功能 |

| 5 V±10%或3.3V±10%灵活电源电压 | |||

| VEXT | VSS 或 E-pad | 2.97~5.50 | 芯片内EVR13和EVR33稳压器的源电压。决定I/O电平的主要的I/O电源。通用待机电源引脚 |

| VFLEX | VSS 或 E-pad | 2.97~5.50 | Flexport专用电源。3.3V或5V电源给VFLEX 供电,决定Flexport的I/O电压。 |

| VDDM | VSSM | 2.97~5.50 | ADC主电源。 |

| VAREF1 | VAGND1 | 2.97~5.50 | 全部器件的ADC参考电源。 |

| 3.3V±10%电源电压 | |||

| VDDP3 | VSS 或 E-pad | 2.97~3.63 | Flash,JTAG和P21电源 |

| VDDFL3 | VSS 或 E-pad | 2.97~3.63 | Flash传感放大器电源。 |

| 1.3V±10%电源电压 | |||

| VDD | VSS 或 E-pad | 1.17~1.43 | 主内核电源。 |

| VDDSB | VSS 或 E-pad | 1.17~1.43 | 仿真器件EMEM(仿真存储器)电源。仅在ED器件中具备。 |

硬件配置选择

经过之前的分析,我们决定选择外置pass器件的3.3V输入LDO模式,即如前图g所示。这种设计相对来说兼顾了系统复杂性和设备稳定性,是一种最小系统板比较实用的电源模式。所以我们需要将外部的电阻HWCFG【0:2】配置为101B,即只需将P14.5下拉即可。

最终,结合前面所说的其它硬件引脚的配置,我们的HWCFG如下配置(注:opt下标表示不贴该电阻):

器件选型

官方针对不同类型的电路有推荐的器件组合,这里一并贴出。(至于能不能买得到就看你的财力了=-=)

| 序号 | 情况/使用实例 | MOSFET(封装) | 电感/电容(封装)→元件参考 |

|---|---|---|---|

| EVR13 SMPS/DC-DC稳压器 | |||

| 1. | IDD <400 mA fDC = 1.5 MHz |

互补型MOSFET BSL215C (TSOP-6)=> Q_1 | 1.电感 LTF3020T-3R3N-H/D1) => L_1 2.输出电容 CGA6M3X7R1C106K (1210)=> C_1 3.输入电容 CGA5L1X7R1C685K (1206)=> C_2 |

| 2. | IDD <400 mA fDC = 1 MHz |

互补型MOSFET BSL215C (TSOP-6)=> Q_1 | 1.电感 LTF3020T-4R7N-H/D => L_1 2.输出电容 CGA6M3X7R1C106K (1210)=> C_1 3.输入电容 CGA5L1X7R1C685K (1206)=> C_2 |

| 3. | IDD <1 A fDC = 1.5 MHz |

互补型MOSFET BSZ15DC02KD (S3O8)=> Q_1 | 1.电感 LTF5022T-3R3N2R5-H/D1) => L_1 2.输出电容 CGA6P1X7R1C226M (1210)=> C_1 3.输入电容 CGA6M3X7R1C106K (1210)=> C_2 |

| 4. | IDD <1 A fDC = 1 MHz |

互补型MOSFET BSZ15DC02KD (S3O8)=> Q_1 | 1.电感 LTF5022T-4R7N2R0-H/D => L_1 3.输入电容 CGA6M3X7R1C106K (1210)=> C_2 |

| 把外部P通道MOSFET作为pass device的EVR13 LDO | |||

| 5. | IDD < 300 mA | P沟道 MOSFET SPD04P10PL (TO-252) | 输出电容 C3216X7R1C475K (1206) |

| 采用内部pass device的EVRx3 LDO – 缓冲电容 | |||

| 6. | IDDX < 100 mA | - | C3216X7R1C105K (1206) => C_2 |

| 7. | IDDX < 200 mA | - | C3216X7R1C225K (1206) => C_2 |

| 8. | IDDX < 300 mA | - | C3216X7R1C475K (1206) => C_2 |

3.3V稳压电路

因为我们放弃了内部的3.3V稳压,所以我们需要外部的3.3V稳压处理,这里也是一个集成LDO的电路。输入端由一个PTC子回复保险丝和ESD二极管构成保护,防止浪涌或反接造成的电路破坏。同时前后各有一组Π型RC滤波器进行滤波。

与此同时,按照上面所述,将3.3V输入直接引入VDDP3_1和VDDP3_2

1.3V稳压电路

内部的1.3V稳压直接按照标准方式进行配置。这里的LDO的mos选型最好VGS要在2V左右,这样3.3V直接降下来mos管的调整范围相对来说是最大的,也最稳定。这里我选的是BSP171,这个mos实际上已经有点大了,官方推荐的bss83实际上应该是我们最小系统最合适的mos,电流输出和栅源电压都满足。那你肯定问我既然好干嘛不选,道理也很简单,因为嘉立创没货了……

其它引脚输入

主要的引脚配置完,剩下的这些引脚按照所需电压接入即可:

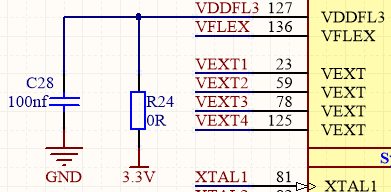

VDDFL3接入3.3V:

VFLEX和VEXTx接入VEXT(3.3V):

VDD接入1.3V:

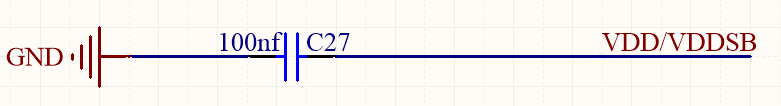

VDDSB(理论上这个应该接到1.3V的,不过因为也没使用ED器件,所以这样不影响):

顺带提一下,上述电源的去耦电容在pcb布置时需要仅靠引脚,而且需要保证每个引脚附近都有去耦电容,具体的布置规范官方资料里也有提示,这是在pcb布置中需要注意的:

如有疑问或错误,欢迎和我私信交流指正。

W.By ChenYX,未经授权,请勿转载!

over~