一、指令周期

-

CPU 从主存中

取出并执行一条指令的时间称为指令周期。指令周期常用若干机器周期来表示,一个机器周期又包含若干时钟周期(节拍或 T 周期,是 CPU 操作的最基本单位)。

-

指令周期、机器周期、节拍和时钟周期的关系如上。

-

对于无条件转移指令

JMP X,在执行时无需访存,只含取指阶段和执行阶段,因此其指令周期仅包含取指周期和执行周期。 -

对于间接寻址指令,其过程:访存取操作数有效地址,然后再次访存取出操作数,所以还需包括

间址周期(介于取指周期和执行周期之间)。 -

当 CPU 采用中断方式实现主机和 I/O 设备的信息交换时,CPU 在每条指令执行结束前,都要发出中断查询信号,若有中断请求,则 CPU 进入中断响应阶段,又称

中断周期。

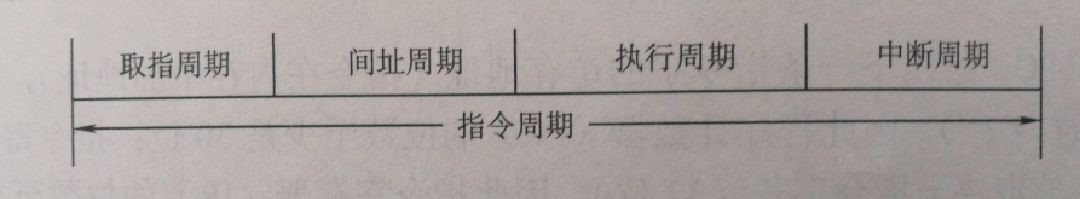

所以一个完整的指令周期包括:取指、间址、执行和中断四个周期,如下图:

-

为了区别不同的工作周期,在 CPU 内设置 4 个触发器

FE、IND、EX 和 INT分别对应取指、间址、执行和中断周期,以“1”状态表示有效,分别由1⟶FE、1⟶IND、1⟶EX,和 1⟶INT这 4 个信号控制。 -

注意:

中断周期中的进栈操作是将 SP 减 1,这和传统意义上的进栈操作相反,原因是计算机的堆栈中都是向低地址增加,所以进栈操作是减 1 而不是加 1.

二、指令周期的数据流

数据流是根据指令要求依次访问的数据序列。在指令执行的不同阶段,要求依次访问的数据序列是不同的;不同的指令其数据流往往不一样。

1、取指周期

- 此周期的任务是

根据 PC 中的内容从主存中取出指令代码并存放在 IR 中,取指后 PC 加 1.如下图:

- 图中涉及的数据流有如下几条:

1)PC⟶MAR⟶地址总线⟶主存

2)CU 发出控制信号⟶控制总线⟶主存

3)主存⟶数据总线⟶MDR⟶IR

4)CU 发出读指令⟶PC 内容加 1.

2、间址周期

- 此时期的任务是

取操作数有效地址,对应的相关数据流如下图:

- 具体数据流就是:

1)Ad(IR) 或 MDR ⟶MAR⟶地址总线⟶主存

2)CU 发出读命令⟶控制总线⟶主存

3)主存⟶数据总线⟶MDR Ad(IR)表示取出 IR 中存放的指令字的地址字段。

3、执行周期

此时期的任务是根据 IR 中的指令字的操作码和操作数通过 ALU 操作产生执行结果,由于不同指令的执行周期不同,所以执行周期没有统一的数据流向。

4、中断周期

- 此时期的任务是

处理中断请求,数据流向如下图:

- 具体数据流如下几种:

1)CU 控制将 SP 减 1,SP⟶MAR⟶地址总线⟶主存

2)CU 发出读命令⟶控制总线⟶主存

3)PC⟶MDR⟶数据总线⟶主存(程序断点存入主存)

4)CU(中断服务程序的入口地址)⟶PC

三、指令执行方案

- 一个指令周期通常要包括几个执行步骤,每个步骤完成指令的部分功能;通常有以下几种方案来安排指令的执行步骤:

1、单指令周期

- 对

所有指令都选用相同的执行时间来完成,指令之间串行执行,指令周期取决于执行时间最长的指令的执行时间。

2、多指令周期

- 对

不同类型的指令选用不同的执行步骤来完成,指令之间仍然是串行,但可选用不同的时钟周期来完成不同指令的执行过程,指令需要几个周期就为其分配几个周期,而不要求所用指令的执行时间都一样。

3、流水线方案

- 指令之间可以

并行执行的方案,其追求的目标是力争在每个时钟周期完成一条指令的执行过程(理想情况),此方案通过在每个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中。

扫描二维码关注公众号,回复:

10372034 查看本文章