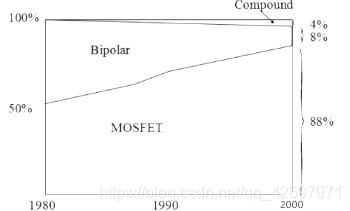

CMOS,咱半导体人第一个知道的一定是NMOS,因为大家培训都是用NMOS,但是你知道吗?世界上第一个MOS却是PMOS,发明于1960年,用于简单的数字逻辑器件(digital logic),但是速度太慢一直没有市场。直到1970年世界上第一颗NMOS出现且速度比PMOS快了2~3倍(因为电子的迁移率/mobility是空穴的2.5倍),并很快取代了PMOS之后,MOS晶体管才逐渐有了市场。但早期主要应用于手表和计算器。直到1980年,人类发明了Well(阱),注解: 因为NMOS要在P-Si里面,而PMOS要在N-Si里面,所以一个单一掺杂的硅片(wafer)上无法同时做NMOS和PMOS。才有了CMOS (Complementary MOS: NMOS+PMOS),此后开始进入摩尔时代 (摩尔定律/moore’s law发表于1975年IEEE)。

MOS的结构如下图,“Well(阱)”/或者Substrate用来装这个MOS的,NMOS必须是P-Well或者P-Substrate,除了well还有“源极(Source)” 和“漏极(drain)”,源极顾名思义类似三极管的发射极,他是载流子(carrier)的源头,那漏极就类似三极管的集电极,用来吸收源极过来的载流子了。还有一个就是“栅极(Gate)”,在台湾的教材叫做闸极。顾名思义Gate就是门或者闸门(知道为啥逻辑电路很多叫做门电路了吧~?)。所以MOS是个四端器件。

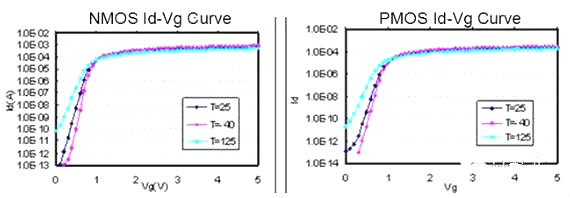

从MOS四个端子的命名就知道了,当初人们就是把它等效为一个水龙头或者连通器,Gate就是开关,只要打开开关水流从源端到漏端逐渐增大,当开关开到最大水流自然也就饱和了,所以MOS的电流电压特性曲线(Id-Vg)如下图。那么在半导体器件里面,理论上他是怎么开启的呢?从结构上我们知道,NMOS的衬底是P-Si,而Source和Drain都是N-Si,所以中间的沟道和两边的Source/Drain形成了两个PN节让Source/Drain彼此隔离,而中间的沟道上面与Gate之间有一层薄薄的Oxide (gate oxide,栅氧),当栅极加正电压(Vg),由于Gate oxide(GOX)不导电,所以这个电压只能停留在gate上靠电场感应使得P-Si里面的少数载流子在电场作用下吸附到表面逐渐耗尽(depletion)表面的P-type,当沟道表面的少数载流子电子积累到一定程度后就会逐渐反型(Reversion)成N-Si,使得Source和Drain连起来,达到开启沟道的目的。PMOS原理类似把所有的掺杂type和电压反过来就行。

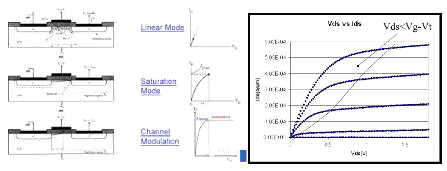

喜欢思考的人一定会问另外一个问题,连通器的水流大小除了由连通器的开关决定外,应该还有一个因素就是连通器两端水压的高度。那MOS管电流除了Gate电压Vg外,应该还有一个Drain端电压?You’re definitely right。当Gate开启后,如果Drain没有电压,则没有压差所以不会产生从源到漏的电子流(电流方向从漏到源),随着drain电压升高,电流自然逐渐升高,此时是成线性增长的,我们称这个期间工作在线性区(liner region, Idlin=μCoxW/L*[(Vg-Vt)Vds-1/2Vd^2])。当Drain电压继续升高,连通器的管路只有那么粗,所以水压再高也过不来了,此时就到了饱和区(satuation region, Idsat=1/2μCoxW/L*(Vg-Vt)^2)。当然在半导体理论里,饱和区的原因是因为载流子在电场加速下的速度饱和(因为载流子加速会碰撞,自然就抑制电流增大)。所以就有了另外一组Id-Vd Curve。

上面右图的Id-Vd curve中,Id在饱和区时不是绝对的不变,而是略微上翘,原因是一个名词叫做沟道长度调制效应(Channel Length Modulation)。从上面的Isat公式可以看出Isat与W/L称正比,所以L变小自然电流变大。因为gate开启时,Drain电压逐渐增大,Source接地,所以靠近Drain端会产生一个夹断点(pinch-off),此时到达饱和。如果Drain电压继续升高,pinch-off向source端扩展,所以Leff(有效沟道长度)减小,所以Isat会略微升高。

学术上,线性区的条件是Vd<Vg-Vt, 反之饱和区的条件就是Vd>=Vg-Vt。

讲完了结构,再来讲什么叫MOS?MOS也叫MOSFET,全名叫做Metal-Oxide-Semiconductor Field-Effect-Transistor,他的Gate是由金属和氧化层(GOX)组成,你们现在看到的Gate的电极是Poly,但是1970年代的Gate是Al,所以叫做Metal-Oxide,那个年代是先做Source/Drain,再做Gate,所以Gate和Metal1一起做的。 但是这样的主要问题是Gate和Source/Drain的Overlay太大了,所以后来先做Gate再做Source/Drain,这样的问题是Source/Drain要高温激活掺杂,而Gate的Al就无法承受了,所以发展到各位现在看到的Poly gate。但是poly毕竟是半导体,在栅极电压下,掺杂原子会发生再分布,所以靠近GOX的掺杂原子会被拉到上面,这就是传说中的多晶耗尽(poly depletion),而这个耗尽的poly因为不导电就充当了GOX的dielectric。在45nm以下机会又无法使用poly gate了,所以又回到了老祖宗的Metal Gate。所以经常看到28nm HKMG (Hi-K Metal gate,顺便讲下Hi-K,因为GOX对Vt的值很重要很重要,学术上叫做跨导/Gm,GOX越薄,跨导特性越好,Vt越低,可是薄了容易漏电,所以必须要有高介电常数的GOX, High-K)。

最后再啰嗦一下CMOS和BJT的区别吧,BJT是两种载流子同时工作的器件,而MOS是单一载流子。BJT是PN节的节型晶体管,而MOS是场效应晶体管。BJT的线性和噪声特性不如MOS。

静电放电(ESD - ElectroStatic Discharge)会给电子器件带来破坏性的后果,是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能。

如何使全芯片有效面积尽可能小、高抗ESD性能且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为因ESD而遭到损害,保证在任意两芯片引脚之间发生的ESD都有低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD所产生的电流,还要箝位工作电路的电压,防止工作电路由于电压过载而受损。在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不被损坏。抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

CMOS电路ESD保护结构的设计

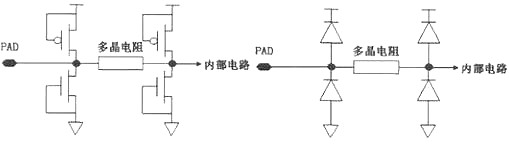

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁或I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地箝位保护电路电压。而在这两部分正常工作时,不影响电路的正常工作。常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。由于MOS管与CMOS工艺兼容性好,因此常采用MOS管构造保护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管开启时能吸收大量的电流。利用这一现象可在较小面积内设计出较高ESD耐压值的保护电路,其中最典型的器件结构就是栅极接地NMOS(GGNMOS,GateGroundedNMOS)。

在正常工作情况下,NMOS横向晶体管不会导通。当ESD发生时,漏极和衬底的耗尽区将发生雪崩,电子空穴对也同时产生。一部分产生的空穴被源极吸收,其余的流过衬底。由于衬底电阻Rsub的存在,使衬底电压提高。当衬底和源之间的PN结正偏时,电子就从源发射进入衬底。这些电子在源漏之间电场的作用下,被加速,产生电子和空穴的碰撞电离,形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,最终使NMOS晶体管发生二次击穿,此时的击穿不再可逆,最终导致NMOS管损坏。

为了进一步降低输出驱动上NMOS在ESD时两端的电压,可在ESD保护器件与GGNMOS之间加一个电阻。这个电阻不能影响工作信号,因此不能太大。画版图时通常采用多晶硅(poly)电阻。

只采用一级ESD保护,在大ESD电流时,电路内部的管子还是有可能被击穿。GGNMOS导通,由于ESD电流很大,衬底和金属连线上的电阻都不能忽略,此时GGNMOS并不能箝位住输入到接收端栅的电压,因为让输入接收端栅氧化硅层的电压达到击穿电压的是GGNMOS与输入接收端衬底间的IR压降。为避免这种情况,可在输入接收端附近加一个小尺寸GGNMOS进行二级ESD保护,用它来箝位输入接收端栅电压,如下图所示。

常见ESD的保护结构和等效电路

在画版图时,必须注意将二级ESD保护电路紧靠输入接收端,以减小输入接收端与二级ESD保护电路之间的衬底及其连线的电阻。为了在较小的面积内画出大尺寸的NMOS管子,在版图中常把它画成手指型,画版图时应严格遵循I/O ESD的设计规则。

如果PAD仅作为输出,保护电阻和端短接地的NMOS就不需要了,其输出级大尺寸的PMOS和NMOS器件本身便可充当ESD防护器件来用,一般输出级都有双保护环,这样可以防止发生闩锁。

在全芯片的ESD结构设计时,注意遵循以下原则:

(1) 外围VDD、VSS走线尽可能宽,减小走线上的电阻;

(2) 设计一种VDD-VSS之间的电压箝位结构,且在发生ESD时能提供VDD-VSS直接低阻抗电流泄放通道。对于面积较大的电路,最好在芯片的四周各放置一个这样的结构,若有可能,在芯片外围放置多个VDD、VSS的PAD,也可以增强整体电路的抗ESD能力;

(3) 外围保护结构的电源及地的走线尽量与内部走线分开,外围ESD保护结构尽量做到均匀设计,避免版图设计上出现ESD薄弱环节;

(4) ESD保护结构的设计要在电路的ESD性能、芯片面积、保护结构对电路特性的影响如输入信号完整性、电路速度、输出驱动能力等之间进行平衡考虑,还需要考虑工艺的容差,使电路设计达到最优化;

(5) 在实际设计的一些电路中,有时没有直接的VDD-VSS电压箝位保护结构,此时,VDD-VSS之间的电压箝位及ESD电流泄放主要利用全芯片整个电路的阱与衬底的接触空间。所以在外围电路要尽可能多地增加阱与衬底的接触,且N+P+的间距一致。若有空间,则最好在VDD、VSS的PAD旁边及四周增加VDD-VSS电压箝位保护结构,这样不仅增强了VDD-VSS模式下的抗ESD能力,也增强了I/O-I/O模式下的抗ESD能力。

一般只要有了上述的大致原则,在与芯片面积折中的考虑下,一般亚微米CMOS电路的抗ESD电压可达到2500V以上,已经可以满足商用电路设计的抗ESD要求。

对于深亚微米超大规模CMOSIC的设计都不用常规的ESD保护內部结构的,大多深亚微米工艺的Foundry生产线都有自己外围标准的ESD结构提供,有严格标准的ESD结构设计规则等,设计师只需调用其结构就可以了,这可使芯片设计师把更多精力放在电路本身的功能、性能等方面的设计上。

结束语

ESD保护设计随着CMOS工艺水平的提高而越来越困难,ESD保护已经不单是输入脚或输出脚的ESD保护设计问题,而是全芯片的静电防护问题。芯片里每一个I/O电路中都需要建立相应的ESD保护电路,此外还要从整个芯片全盘考虑,采用整片(whole-chip)防护结构是一个好的选择,也能节省I/OPAD上ESD元件的面积。