序文

多くの INTEL (ALTERA) IP には、LVDS SERDES IP など、生成時に独自のルーチンが付属します。「生成」メニューで公式ルーチンを生成することを選択できます。

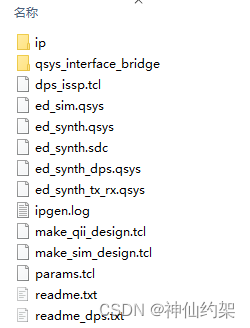

その後、IP が配置されているディレクトリに [lvds_0_example_design] フォルダーが作成されますが、このフォルダーには FPGA プロジェクトがありません。

ルーチンはどこにありますか?

readme.txt を表示します。

これは、Altera

LVDS SERDES IP のサンプル デザイン ファイル セットの readme.txt ファイルです。このディレクトリ内のファイルを使用すると、

次のことが可能になります。

1) LVDSインターフェイス (生成時に指定したものと同じコンフィギュレーション)をインスタンス化する Quartus Prime プロジェクトを作成します 。

オプションで、ターゲット・デバイスとピン位置の

割り当てを指定し、Quartus Prime ソフトウェアを使用してフル・コンパイルを実行し、

タイミング・クロージャを検証し、

Quartus Prime アセンブラによって生成されたプログラミング・ファイルを使用してボード上のインターフェースをテストすることができます。

2) サポートされているさまざまなシミュレーターのシミュレーション プロジェクトを作成します。シミュレーション

プロジェクトは、LVDS インターフェイス (

MegaWizard で指定したものと同じ構成)

と、インターフェイスを実行するサンプル テスト ベンチをインスタンス化します。 プロジェクトが生成されるので、シミュレーションを実行し、その結果を LVDS インターフェイス IP の動作を理解する方法として

使用できます 。このフローは機能シミュレーションのみをサポートします。タイミング シミュレーションはサポートされていないため、 TimeQuest ソフトウェアが提供する静的タイミング解析を使用してタイミング クロージャを検証する必要があります。注: 外部 PLL モードでは、外部 PLL のサンプルが スタンドアロン QSYS ファイル (lvds_external_pll.qsys) で提供されます。 これは変更して、外部 PLL モードのユーザーのデザインで使用できます 。 合成サンプル デザインには、トップレベル SDC ファイルを含む LVDS IP に外部 PLL を接続する 方法の例が含まれています 。 qsys_interface_bridge ディレクトリーにあるファイル: qsys_interface_bridge_hw.tcl は 、LVDS を QSYS の PLL に接続する のに役立つカスタム コンポーネントを定義します。 これは単に、一致しない QSYS インターフェイス間の接続 (つまり、クロックとコンジット) を許可するだけです。 合成またはシミュレーション QSYS システムを変更する 場合は、これらのファイルがプロジェクト ディレクトリに追加されていることを確認してください 。 提供された PLL を RTL インスタンス化として使用し、 QSYS システムではなく RTL でコンポーネントを手動で接続する 場合、qsys_interface_bridge は必要ありません。

################################################ #############################

Quartus Prime サンプルデザインの生成

############### ################################################ ##############

サポートされている引数については、

quartus_sh -t make_qii_design.tcl -help を実行してください

。 Quartus Prime サンプル デザインを生成するには、

quartus_sh -t make_qii_design.tcl を

実行してください。使用するデバイスを指定して実行します。

quartus_sh -t make_qii_design.tcl -device [device_name]

生成されたサンプル デザインは、「qii」サブディレクトリに保存されます。

デザインを再生成するには、デザインを削除して上記のコマンドを再実行します。

DPS (ダイナミック フェーズ シフト)、

TX/RX の組み合わせなどのデフォルト以外のサンプル デザインを生成するには、

quartus_sh -t make_qii_design.tcl -device [device_name] -system [system_name] を実行します。注: [system_name] は、指定されたサンプル デザインの QSYS システムの名前です。

デフォルトの「ed_synth.qsys」のシステム名は「ed_synth」です。生成されたサンプル デザインは、「qii_<system_name>」サブディレクトリに保存されます。

################################################ #############################

シミュレーション サンプル デザインの生成

################ ################################################ #############

Verilog または混合言語

シミュレーターのシミュレーション サンプル デザインを生成するには、次のコマンドを実行します。quartus_sh -t make_sim_design.tcl VERILOG

VHDL 専用シミュレーターのシミュレーション サンプル デザインを生成するには、次のコマンドを実行します。quartus_sh -t make_sim_design.tcl VHDL

さまざまなシミュレータ用に生成されたサンプル デザインは、「sim」

サブディレクトリに保存されます。たとえば、Synopsys の VCS を使用してシミュレーションを実行するには、次を実行します。cd sim/synopsys/vcs

./vcs_setup.sh

言及した

Quartus Prime サンプル デザインを生成するには、

quartus_sh -t make_qii_design.tcl を実行します。

つまり、この TCL 文を実行するとルーチンを生成できます。

TCLを実行する

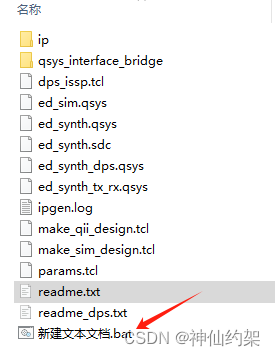

1. 現在のフォルダーに新しいテキスト ファイルを作成し、サフィックスを Bat に変更します。

2. 「quartus_sh -t make_qii_design.tcl」をテキストファイルにコピーします。

3. ダブルクリックしてバットファイルを実行すると、cmd ウィンドウが表示されます。しばらく待ちます。

4. カレントディレクトリに、ルーチンの FPGA プロジェクトとなるフォルダー [qii] が生成されます。

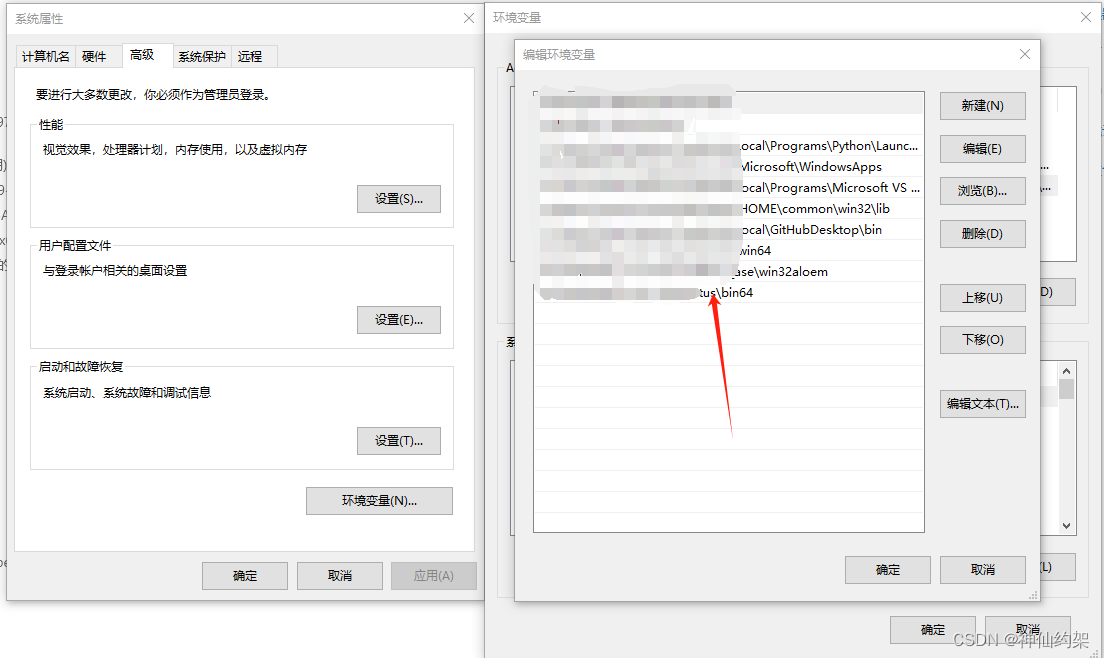

TCL が実行できない場合の対処方法

システム環境変数が正しく設定されていない可能性が高くなります。環境変数にQuartus IIを追加する必要があります。

システム プロパティ --- 環境変数 --- ユーザー変数 --- パス、追加

*\4th\bin64

参考文献: