コンピュータの算術演算

サブワード対訳(ざっと立ち読み)pdf 約170ページ

浮動小数点加算は結合的ではありません。

整数データ型に適用される並列実行戦略は、上記の理由により浮動小数点データ型には適用されません↑

プロセッサー

組み立てライン

パイプライン処理は、複数の命令を重複して実行できるようにする実装テクノロジです。

パイプライン処理は、個々の命令の実行時間を短縮するのではなく、命令のスループットを向上させることでパフォーマンスを向上させます。

前進またはバイパス

命令間の並列処理

パイプライン技術は、命令レベルの並列処理と呼ばれる、命令間の潜在的な並列処理を利用します。

命令レベルの並列処理を改善するには、主に 2 つの方法があります。

パイプラインのステージ数を増やす

パイプライン内の機能コンポーネントの数を増やして、サイクルごとに複数の命令を発行できるようにする手法は、マルチ発行と呼ばれます。

マルチイシュープロセッサを実装するには、主に 2 つの方法があります。

命令を発行するかどうかの判定はコンパイル時に完了することを静的多重発行といいます。

命令を発行するかどうかの判断が動的実行中にハードウェアによって完了する場合、動的マルチ発行と呼ばれます。

レジスタ名の変更レジスタ名の変更の目的は、データの依存関係に加えて、他のデータ、命令間の依存関係を排除することです。たとえば、ld x30,0(x20)、add x31、x31,x21、sd x31, 8(x20) は、すべて x31 を使用することを除き、これらの命令は実際には互いに独立しています。この状況は逆相関、または名前相関と呼ばれます。

反相関:名前相関とも呼ばれ、強制的な名前の再利用によって引き起こされる順序付け。これは命令間の真のデータ相関ではありません。

動的複数発行プロセッサ

スーパースカラプロセッサとも呼ばれる動的複数エミッタ

動的スケジューリング パイプライン:ハードウェアは後続の実行用の命令を選択し、パイプラインのストールを回避するために命令を再配置します。このようなプロセッサでは、パイプラインは、命令フェッチ、発行ユニット、多機能ユニット、コミット ユニットの 3 つの主要な部分に分割されます。

高速化: 命令レベルの並列処理と行列乗算

階層ストレージ

時間的局所性 データ項目にアクセスすると、近い将来再びアクセスされる可能性が高い

空間的局所性: データ項目がアクセスされると、そのアドレスに隣接するデータ項目にもすぐにアクセスされる可能性があります。

プロセッサに最も近い層のデータは、遠い層のデータのサブセットであり、すべてのデータは最も遠い層に格納されます。

隣接する 2 つの層間で交換される情報の最小単位は、ブロック または 行と呼ばれます。

書き込み操作を処理する

ライトスルーまたはライトスルー:書き込み戦略。書き込み操作では常にキャッシュと次のレベルのストレージを同時に更新し、両者間のデータの一貫性を確保します。

書き込みリターン:書き込み戦略。書き込み操作を処理する場合、キャッシュ内の対応するデータ ブロックの値のみが更新されます。データ ブロックが置き換えられると、更新されたデータ ブロックがストレージの次のレベルに書き込まれます。

キャッシュの性能評価と改善

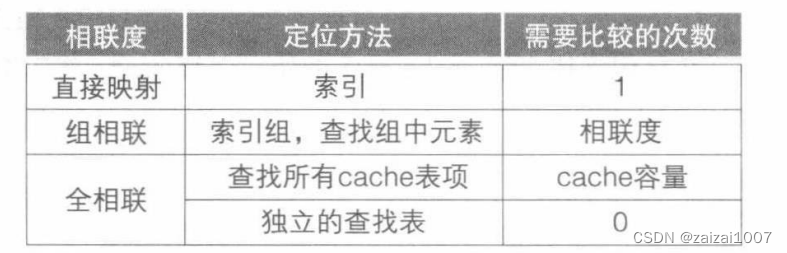

ダイレクト マッピング:データ ブロックには、キャッシュ内に対応する場所が 1 つだけあります。

フル アソシアティブ:データ ブロックはキャッシュ内のどこにでも保存できます。フル アソシアティブ キャッシュで特定のデータ ブロックを見つけるには、すべてのエントリを比較する必要があります。

セットアソシアティブ キャッシュ:キャッシュ内で各データ ブロックが格納される場所の数は固定値 (少なくとも 2) であり、データ ブロックごとに n 個の場所を持つセット アソシアティブ キャッシュは、n ウェイ セット アソシアティブ キャッシュと呼ばれます。n ウェイ セット アソシアティブ キャッシュにはいくつかのグループがあり、各グループには n 個のデータ ブロックが含まれます。

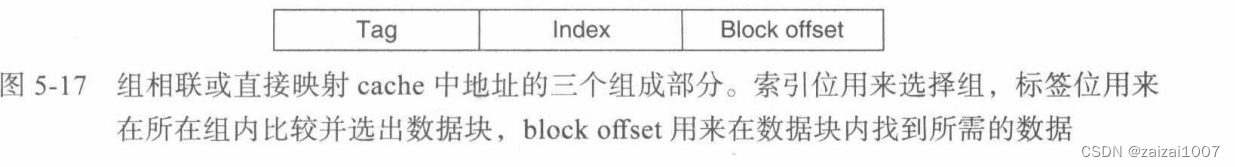

キャッシュ内のデータ ブロックを検索する

信頼性の高いメモリ階層

信頼性を高める最善の方法は冗長性です

失敗の定義:

MTTF を改善する 3 つの方法:

1ビットエラーの訂正と2ビットエラーの検出 ハミング符号化

仮想マシン

仮想マシンをサポートするソフトウェアは仮想マシン モニターまたはハイパーバイザーと呼ばれ、その基盤となるハードウェア プラットフォームはホストと呼ばれ、そのリソースはクライアントの仮想マシンによって共有されます。

ハイパーバイザーはクライアント ソフトウェアへのソフトウェア インターフェイスを提供し、各クライアントの状態を分離し、クライアント オペレーティング システムを含むクライアント ソフトウェアからハイパーバイザー自体を保護する必要があります。

定性的ニーズ:

- パフォーマンスに関連する動作や、複数の VM 間での共有による固定リソースの制限を除き、クライアント ソフトウェアは、ローカル ハードウェア上であるかのように仮想マシン上で実行される必要があります。

- クライアント ソフトウェアは実際のシステム リソースの割り当てを直接変更することはできません

プロセッサを「仮想化」するには、VMM は特権アクセス、I/O、例外、割り込みなど、ほとんどすべてを無効にする必要があります。

仮想ストレージ

メイン メモリは、通常はディスクによって実装される補助記憶装置のキャッシュとして機能することができ、このテクノロジは仮想記憶装置と呼ばれます。

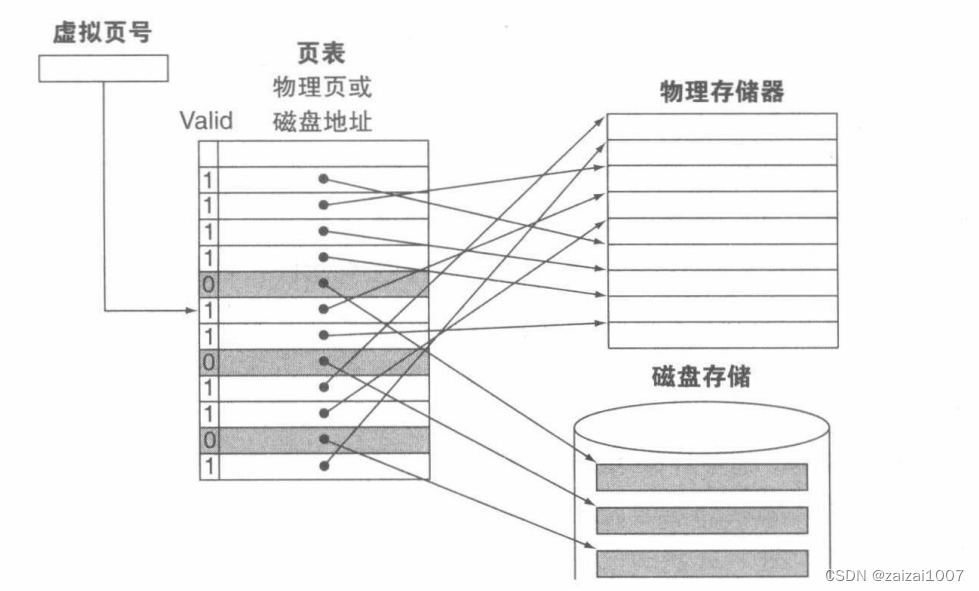

仮想ストレージでは、アドレスは仮想ページ番号とページ内オフセットに分割されます。

メモリ内のページがいつ置き換えられるかを事前に知ることはできないため、オペレーティング システムは通常、プロセスの作成時にすべてのページ用のスペースをフラッシュ メモリまたはディスク上に作成します。この領域はスワップ領域(プロセスの仮想アドレス空間全体のために確保されるディスク領域)と呼ばれ、その際、各仮想ページがディスク上のどこに格納されるかを記録するデータ構造も作成します。

アドレス変換の高速化:TLB

ブロック テーブル (TLB、最近使用されたアドレスのマッピング情報を記録するために使用されるキャッシュ。これにより、毎回ページ テーブルにアクセスする必要がなくなります)

仮想ストレージの保護

仮想ストレージの最も重要な機能は、複数のプロセスがメイン メモリを共有できるようにしながら、これらのプロセスとオペレーティング システムにメモリを保護することです。保護メカニズムは明確である必要があります。複数のプロセスが同じメイン メモリを共有しますが、意図的か非意図的かにかかわらず、悪意のあるプロセスは別のユーザー プロセスやオペレーティング システムのアドレス空間に書き込むことはできません。

コンテキストスイッチ:別のプロセスがプロセッサを使用できるようにするには、プロセッサ内の状態を変更し、現在のプロセスが戻るときに必要な状態を保存します。

TLB エラーとページ フォールトの処理

TLB 障害は、次の 2 つの可能性のいずれかを示します。

- ページはメモリ内にあります。不足している TLB エントリのみを作成する必要があります。

- ページはメモリ内にないため、ページ フォールトを処理するには制御をオペレーティング システムに転送する必要があります。

TLB またはページ フォールトを処理するには、例外メカニズムを使用してアクティブなプロセスを終了し、制御をオペレーティング システムに移し、中断されたプロセスの実行を再開する必要があります。

オペレーティング システムは、ページ フォールトの原因となった仮想アドレスを認識したら、次の 3 つの手順を完了する必要があります。

要約する

仮想ストレージは、メイン メモリとセカンダリ ストレージ間のデータ キャッシュ管理のための第 1 レベルのストレージ階層です。仮想ストレージを使用すると、単一のプログラムがメイン メモリの制限を超えてアドレス空間を拡張できます。仮想ストレージは、保護された方法で同時にアクティブな複数のプロセス間でのメモリの共有をサポートします。

ストレージ階層の一般的なフレームワーク

ブロックを置ける場所

ブロックの見つけ方

ストレージ階層では、ダイレクト マッピング、セット アソシアティブ マッピング、またはフル アソシアティブ マッピングのいずれを選択するかは、障害のコストと、時間や追加のハードウェア オーバーヘッドを含むアソシエイティブ実装のコストとの間のトレードオフによって決まります。

キャッシュ障害が発生した場合にどのブロックを置き換えるか

- ランダム: ハードウェア支援の実装を使用して、候補ブロックをランダムに選択します。

- 最も最近使用されていないブロック (LRU): 置き換えられるブロックは、最も長い間使用されていないブロックです。

書き込み操作の実装方法:

- ライトスルー: 情報はキャッシュ内のブロックと、ストレージ階層の下位のブロック (キャッシュのメイン メモリ) に書き込まれます。

- 書き込みリターン: 情報はキャッシュ内のブロックにのみ書き込まれます。変更されたブロックは、置換された場合にのみ階層の下位レベルに書き込まれます。

リターンを書く利点:

- プロセッサは、メモリではなくキャッシュが受信できる速度で個々のワードを書き込むことができます。

- ブロック内で複数の書き込みを行う場合、ストレージ階層の下位レベルへの書き込みは 1 回だけ必要になります。

- ブロックを書き戻す場合、システムはブロック全体を書き込むことで高帯域幅の伝送を効果的に利用できます。

ライトスルーの利点:

3C: ストレージ階層を理解するための直感的なモデル

有限状態オートマトンを使用して単純なキャッシュを制御する

有限状態オートマトン:一連の入力/出力、状態遷移関数 (現在の状態と入力を新しい状態にマッピング)、および出力関数 (現在の状態と入力を述語出力にマッピング) を含む順序論理関数

次状態関数:入力と現在の状態を指定して、有限状態オートマトンの次の状態を導出できる組み合わせ関数

並列処理とストレージ階層: キャッシュの一貫性

一貫性を実現するための基本的な考え方