MOS 管駆動電流の推定と MOS 駆動のいくつかの特殊なアプリケーションの分析

この記事では、MOS 管の駆動電流の推定、つまり次のパラメータに焦点を当てます。

次のように計算できます。

ターンオン電流

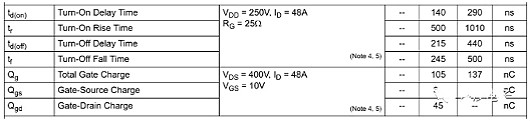

Ion=Qg/Ton=Qg/Td(on)+tr、Ion=105nc/(140+500)ns=164mAを得るデータを取り込みます。

シャットダウン電流

Ioff=Qg/Toff= Qg/Td(off)+tf、データを取り込んで Ioff=105nc/(215+245)ns=228mA を取得します。

したがって、駆動電流は 300mA 程度で十分であると結論付けられます。この計算についてはよく考えてください。ここで、RG=25Ωという条件の詳細に注意する必要があります。したがって、この指標は無意味です。

どのように計算すればよいのでしょうか? 実際にはこのようになるはずで、製品のスイッチング速度に応じてスイッチング電流が決まります。I=Q/t により、具体的な MOS トランジスタ Qg データと回路の電流能力が得られ、Ton=Qg/I が得られます。たとえば、45N50、Vgs=10V、VDS=400V、Id=48A、Qg=105nCの場合。1Aの駆動能力で駆動した場合、105nSという高速なスイッチング速度が得られます。

もちろん、これは駆動電流の値を推定することしかできず、MOS 管のオーバーシュート波形のさらなるテストが必要です。駆動回路を設計する際には、MOS管の前に10Ω程度の抵抗を接続するのが一般的です(テスト波形に合わせてパラメータを調整してください)。

ここで、Qg はゲート容量ではなく、ターンオン速度とターンオフ速度を計算するために使用されることに注意してください。

MOS 管の駆動電流の推定については説明しましたが、MOS 管のターンオン プロセスについては以下で説明します。

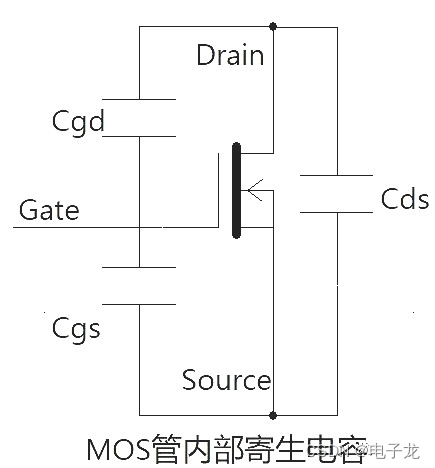

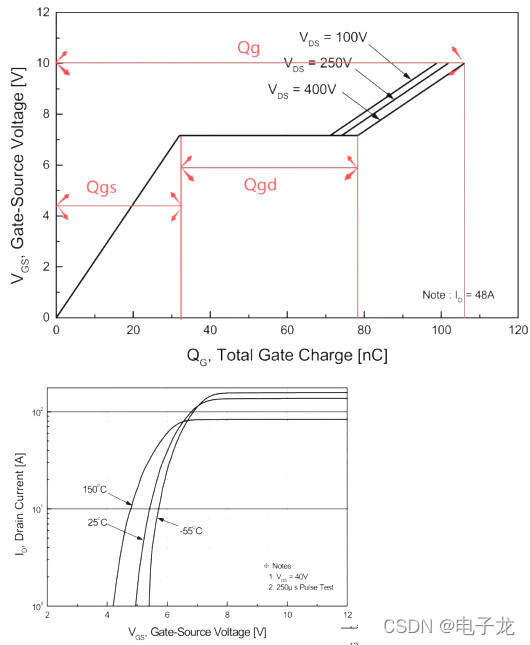

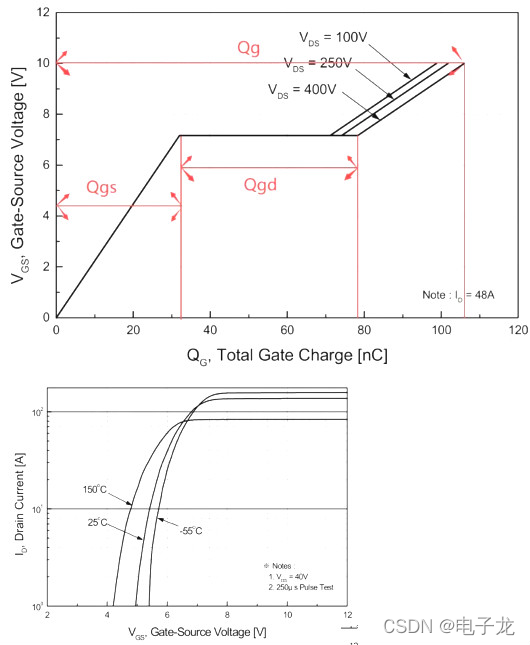

MOS管Cgsの充電を開始し、電圧が5Vまで上昇するとIdに一定の電流が流れます。充電を続けると、ID はどんどん大きくなっていきますが、完全にはオンになっていません。Idが電流に対して上昇すると、Idは変化しなくなり、Cgsも変化しなくなります。

このとき、入力電圧は Cgs を充電せず、Cgd ミラーコンデンサを充電し、MOS 管は完全にオンになります。

MOS 管が完全にオンになると、入力電圧はミラー コンデンサを通過しなくなり、Vgs が入力電圧 10V に等しくなるまで Cgs を充電し続けます。

図では、Vgs 入力電圧は変化しません。つまり、Qgd ステージでは、入力電圧は Cgs を充電せず、Cgd ミラー コンデンサを充電します。これはMOS管本来の伝達特性です。この期間の一定の電圧はプラトー電圧とも呼ばれます。

このとき、MOS管の電流と抵抗は、P=I・I・Rより、このとき管が消費する電力、発熱が激しいので、プラットフォーム電圧の動作時間をできるだけ短くするようにしてください。可能。

一般に、耐圧レベルが高くなるほどMOS管の入力容量が大きくなり、逆方向伝達容量Crssが小さくなり、ミラー効果が小さくなります。

MOS ドライバーのいくつかの特別なアプリケーション

1. 低電圧アプリケーション

5V電源を使用する場合、この時に従来のトーテムポール構造を使用すると、三極管の電圧降下が約0.7Vあるため、実際の最終ゲート電圧は4.3Vしかかかりません。現時点で、公称ゲート電圧が 4.5V の MOS 管を選択することには一定のリスクがあります。3V などの低電圧電源を使用する場合にも同じ問題が発生します。

2. 幅広い電圧対応

入力電圧は固定値ではなく、時間やその他の要因によって変化します。この変化により、PWM 回路によって MOS チューブに供給される駆動電圧が不安定になります。

高いゲート電圧下でも MOS チューブを安全にするために、多くの MOS チューブにはゲート電圧の振幅を強制的に制限する電圧調整チューブが組み込まれています。この場合、供給される駆動電圧がツェナー管の電圧を超えると、静的消費電力が大きくなってしまいます。

同時に、抵抗分圧の原理により単純にゲート電圧を下げると、入力電圧が比較的高い場合にはMOS管は良好に動作しますが、入力電圧が低下するとゲート電圧が不足し、MOS管の動作が不十分になります。導通して消費電力が増加します。

3. デュアル電圧印加

一部の制御回路では、ロジック部では一般的な 5V または 3.3V のデジタル電圧が使用され、パワー部では 12V 以上の電圧が使用されます。2 つの電圧は共通の方法で接続されます。このため、低圧側が高圧側のMOS管を効果的に制御できる回路が必要となり、高圧側のMOS管も1.で述べた問題に直面することになります。と2。これら 3 つのケースでは、トーテムポール構造では出力要件を満たすことができず、多くの既製 MOS ドライバー IC にはゲート電圧制限構造が含まれていないようです。