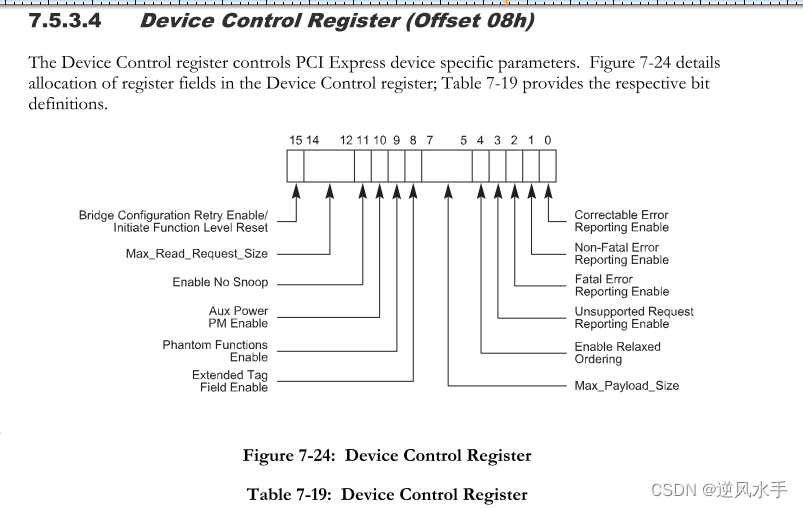

Maximum Payload Size

"Maximum Payload Size"

(maximum transfer payload size) is a bit field in the PCI Express device control register, which is used to set the maximum transfer payload size supported by the device.

PCI Express uses data packets (Packet) to transmit data, and data packets are composed of a header and a payload (Payload). The payload is the actual portion of data to be transmitted. Maximum Transfer Payload Size defines the maximum payload size a device can support.

In the "Maximum Payload Size Supported" (MPSS) bit field, [2:0] represents 3 bits, which are used to encode the value of the maximum transmission payload size supported. Typically, possible values include:

000: 128 bytes

001: 256 bytes

010: 512 bytes

011: 1024 bytes

100: 2048 bytes

101: 4096 bytes

These values indicate the maximum payload size supported by the device. The choice of payload size affects the transfer performance and efficiency of the PCI Express bus. Larger payload sizes improve bandwidth utilization and transfer efficiency, but also increase latency. Therefore, when configuring the device, it is necessary to select an appropriate maximum transmission load size according to specific application requirements and system performance requirements.

Please note that each device has a limit to the maximum transmission payload size, and the maximum transmission payload size of all devices in the system should be consistent to ensure normal data transmission and compatibility

Controls the maximum data length that a TLP can transmit. As a receiver, it must be able to process TLP data packets with the same size as the MPS setting. As a transmitter, it is not allowed to create TLP data packets exceeding the MPS setting.

The PCIe protocol allows a maximum payload of 4K, but stipulates that all devices on the entire transmission path must use the same MPS setting, and at the same time cannot exceed the MPS capability value of a device on the path. In other words, devices with high MPS capability must accommodate devices with low MPS capability. Taking PCIe SSD as an example, it is useless to insert it into an old motherboard (MPS is only 128 Byte), no matter how large your Payload size is.

The MPS value setting of the system is completed in the device enumeration configuration stage after power-on. Taking the PCIe RC and PCIe SSD on the motherboard as an example, they all declare in the Device Capability Register that they can support various MPS and OS PCIe The driver detects their respective capability values, and then sets the lower one to the Device Control register of both.

The MPS capability of PCIe SSD itself is set during the initialization phase of its PCIe core.

Maximum Read Request Size

"Maximum Read Request Size" is a bit field in the PCI Express device control register, which is used to set the maximum read request size supported by the device.

On the PCI Express bus, the system host can send read requests to devices to obtain data. The maximum read request size defines the maximum amount of data a device can support for a read request.

In the "Maximum Read Request Size" (MRRS) bit field, [2:0] represents 3 bits, which are used to encode the value of the maximum read request size supported. Typically, possible values include:

000: 128 bytes

001: 256 bytes

010: 512 bytes

011: 1024 bytes

100: 2048 bytes

101: 4096 bytes

These values indicate the maximum amount of read request data supported by the device. Larger read request sizes can improve data transfer efficiency and bandwidth utilization because more data can be transferred in one request. However, a large amount of read request data will also increase the delay of bus transmission.

In the configuration phase, the PCIe driver of the OS will also configure another parameter, the maximum read request size, which is used to control the maximum size of a Memory read, with a maximum of 4K (in units of 128 Byte). The Read request size can be larger than MPS, for example, for

a A PCIe SSD with MPS=128 Byte sends a 512 Byte read request, and the PCIe SSD can respond to this request by returning four 128 Byte Cplds or eight 64 Byte Cplds. At the OS level, you can balance the throughput between multiple PCIe SSDs by controlling the maximum read request size parameter of the PCIe SSD, so as to prevent the system bandwidth (a total of 40 lanes) from being occupied by certain SSDs.

At the same time, the read request size also has an impact on the performance of the PCIe SSD. If the size is too small, it means that more requests need to be sent to obtain the same data, and the TLP of the read request does not carry any data payload.

For example, to transmit 64K data, if read request=128 byte, 512 read TLPs are needed, and the waste of 512 TLPs is not small.

In order to improve the transmission efficiency especially for large Block Size data, it is good to set the read request size as large as possible and transmit more data with fewer times.