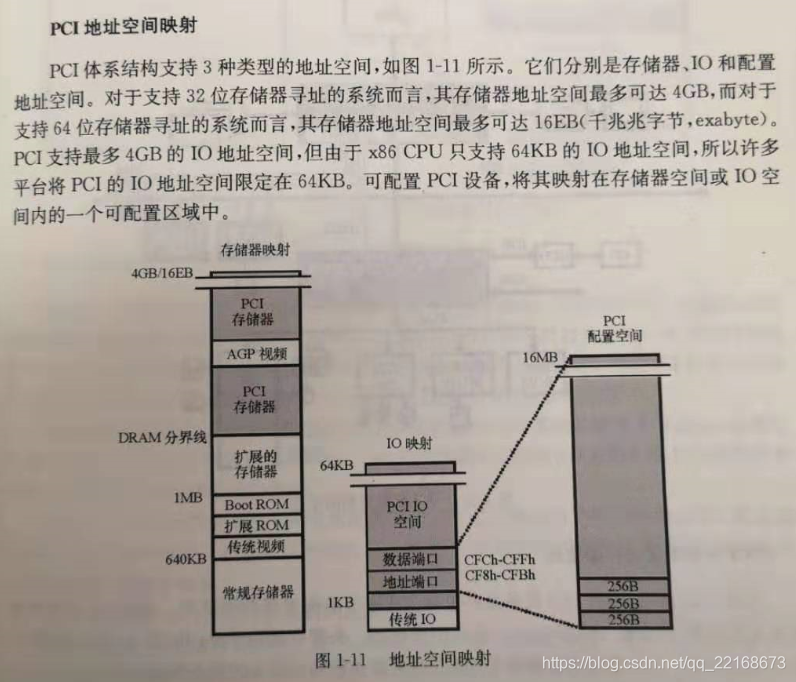

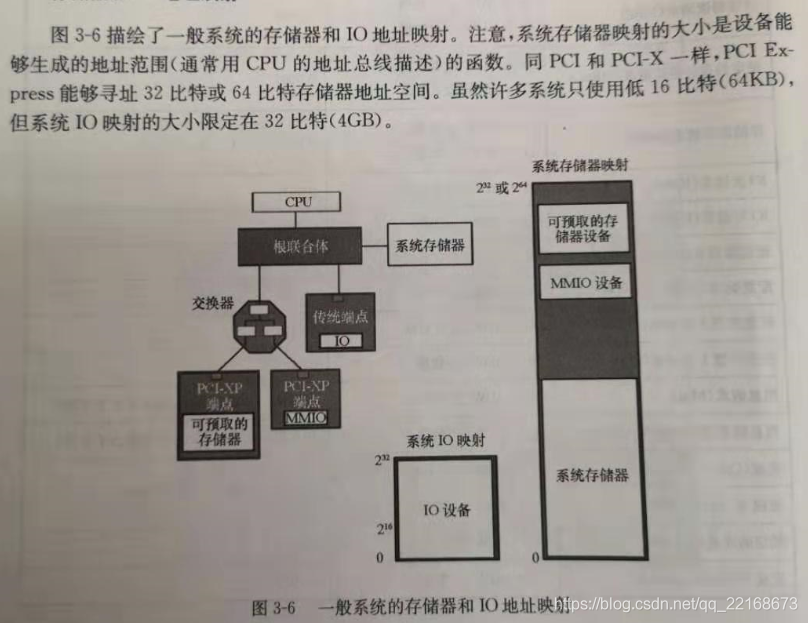

1, and the memory address mapping IO

2, BAR Overview

2.1 PC card read and write access

If the board sends packets to the TLP PC, for example MWr package, it is well understood, the address information is the physical address of the PC (note here that the physical address); if it is MRd package, after it received a reply a complete PC package, completion board from the data analysis to obtain data MRd read address.

2.2 PC card read and write access

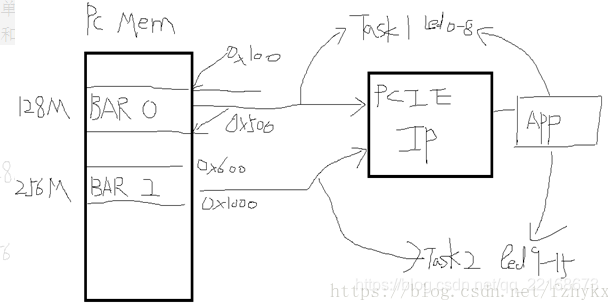

Then how to read and write PC data card it? The simplest explanation, PC startup Shi, BIOS detect all peripherals. Of PCIe (PCI) device is, the BIOS detects the number of BAR board space, how much of each space, and assign an address to the corresponding BAR these spaces. For PC devices, which can "see" only PCIe board space BAR space, it can only access the BAR space. That is, the board can send legitimate PCIe TLP packet, and the corresponding PC side; but the PC card access is limited BAR space.

In short, PC machine memory PCIE want to operate the device can only be operated via the space bar. The PC can only see the bar space (ignoring the starting address and start), PCIE core by detecting different addresses judged to be task1 or task2.

BAR hard-coded bits include a request type, request size, and whether the target device is considered to be prefetched.

Type0 Header data bit in register BAR is 32-bit D register high is configurable, then the configuration may indicate the start address of the device ; some data bit intermediate register value is inoperable for the requested address representing size range ; several type of operation is the low information bits.

In the PCIE IP Core configuration process, there will be BAR address configuration. BAR can set the size of the value corresponding to the number of the FIG Type0 Header BAR32 bit register inoperable position.

BAR is not part of the low bit software is operated, which only the high bits of software can be operated. These low bit inoperable determines the size and type of operation may apply to the current address space supported by a BAR.

3, BAR configuration

- BAR 1 to write the whole address cfg write request.

- By cfg read request to read BAR.

- BAR according to the value read request size is determined as follows BAR, the request types, and configuration software write (type 0) to the program start address, i.e., start address register BAR high programming device is.

4, BAR address range TLP packet address correspondence

TLP address field and the relationship between space BAR address:

TLP can be routed to the address to the corresponding device space BAR. For example, there is now a mem read request, if the routing address (the address information contained in the TLP) is 0x71000000, and the apparatus has a spatial extent mem func0 is 0x70000000 ~ 0x80000000, then this will be the TLP process func. Reads the corresponding data from the corresponding address 0x71000000 of func0.

The relationship between memory address and TLP address field:

references

| Author | Hirofumi |

| 1, ABCA | PCIe practice road: BAR space and TLP |

| 2、 | PCI Express system architecture standards textbooks |

| 3、Felix | PCIe literacy - base address register (BAR) Detailed |

| 4、fzhykx | xlinx_pcie_ip use notes |