table of Contents

1. Comparison of operating modes

1. Comparison of operating modes

1. Cortex-M operating mode

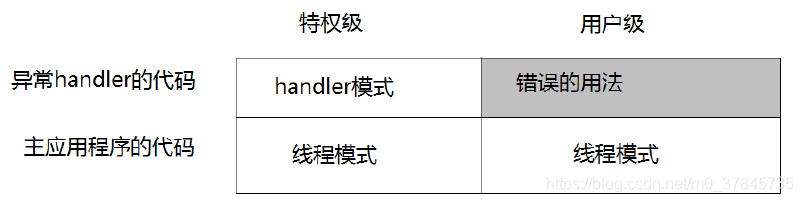

STM32 has only two operating modes, hander mode and thread mode . According to different operating rights, it is divided into privilege level and user level . In order to provide a protection mechanism for memory access, so that ordinary user program code cannot accidentally or even maliciously perform critical operations, the processor supports two privilege levels (privileged hander mode, privileged thread mode)

Conversion under different levels and operating modes:

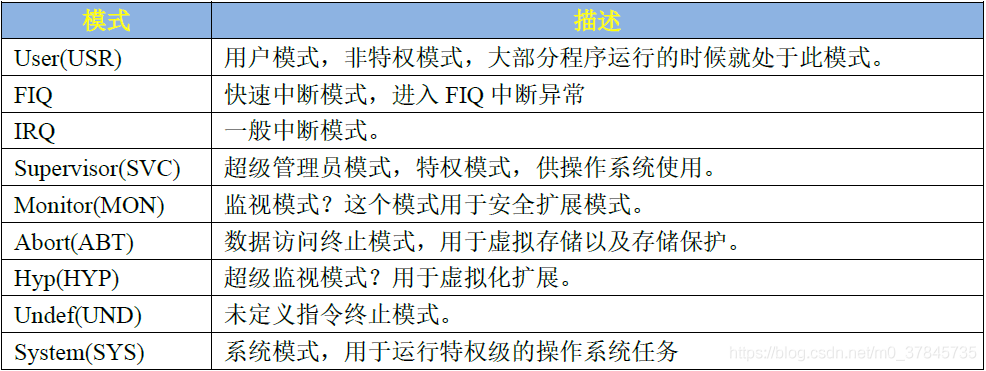

2. Cortex-A operating mode

Cortex-A has 9 operating modes

Except for User (USR) user mode, the other 8 operating modes are all privileged modes. These operating modes can be switched arbitrarily through software, and can also be switched through interrupts or exceptions . Restricted resources must perform mode switching. However, the user mode cannot be switched directly. In the user mode, an exception is needed to complete the mode switch. When the mode is to be switched, the application can generate an exception, and the processor mode switch is completed during the exception processing .

Two, register group

1. Cortex-M register group

R0-R12 : General-purpose registers, all 32-bit general-purpose registers, used for data manipulation. But note: most 16-bit Thumb instructions can only access R0-R7, while 32-bit Thumb-2 instructions can access all registers

R13 : Two stack pointers, so only one of them can be used at any one time

- Main stack pointer (MSP): The stack pointer used by default after reset, used in the operating system kernel and exception handling routines (including interrupt service routines)

- Process Stack Pointer (PSP): Used by the user's application code.

R14 : connection register, when a subroutine is called, the return address is stored by R14

R15 : Program counter register, pointing to the current program address. If you modify its value, you can change the execution flow of the program

Special function registers : Cortex-M3 is also equipped with several special function registers at the core level, including program status word register set (PSRs), interrupt mask register set (PRIMASK, FAULTMASK, BASEPRI), control register (CONTROL)

2. Cortex-A register bank

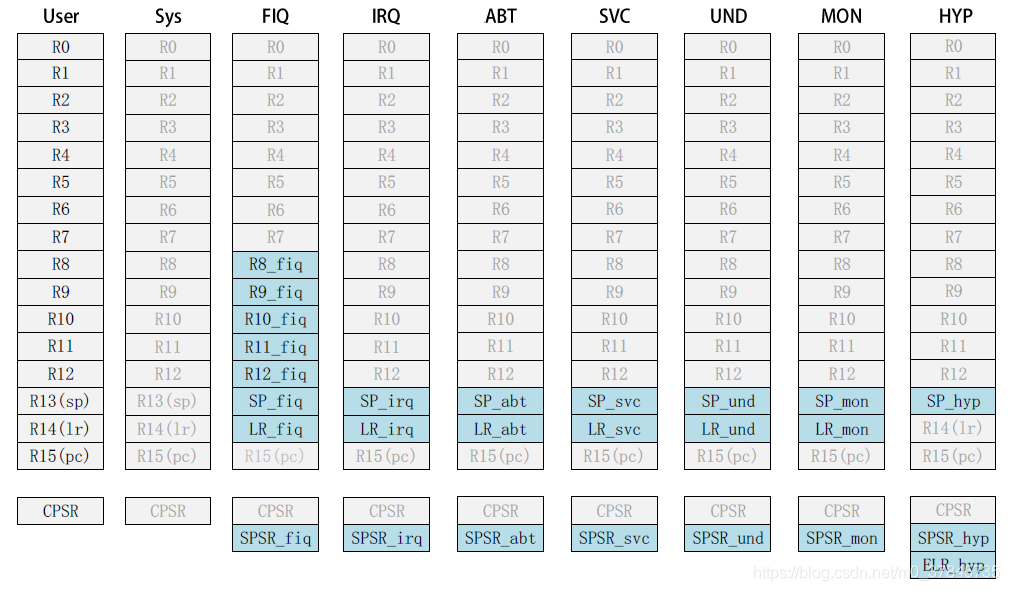

The Cortex-A architecture provides 16 32-bit general-purpose registers (R0~R15) for software use. The first 15 (R0~R14) can be used as general data storage. R15 is the program counter PC, which is used to store what will be executed. instruction. ARM also provides a current program status register CPSR and a backup program status register SPSR. The SPSR register is the backup of the CPSR register.

Cortex-A7 has 9 operating modes, and each operating mode has a set of corresponding register sets. The visible registers of each mode include 15 general registers (R0~R14), one or two program status registers, and a program counter PC. Among these registers, some are the same physical register shared by all modes, and some are independently owned by each mode. The light-colored fonts are the registers shared with the User mode, and the blue-green backgrounds are the unique registers of each mode.

R0-R7 : Registers are not backed up. In all processor modes, these 8 registers are the same physical register. In different modes, the data in these 8 registers will be destroyed. So there is no special purpose

R8-R12 : Backup registers, in the fast interrupt mode (FIQ) they correspond to Rx_irq (x=8~12) physical registers, in other modes, they correspond to Rx(8~12) physical registers.

R13 : Stack pointer, there are a total of 8 physical registers, one of which is shared by user mode (User) and system mode (Sys), and the remaining 7 correspond to 7 different modes.

R14 : Connection register, when a subroutine is called, the return address is stored by R14. There are a total of 7 physical registers, one of which is shared by user mode (User), system mode (Sys) and super monitor mode (Hyp), and the remaining 6 correspond to 6 different modes.

R15 : Program counter register, pointing to the current program address. If you modify its value, you can change the execution flow of the program

CPSR : Current program status register. This register contains some status bits such as condition flags, interrupt disable bits, current processor mode flags, and some control bits

To sum up, the Cortex-A core registers are composed as follows:

①, 34 general registers, including R15 program counter (PC), these registers are all 32 bits.

②, 8 status registers, including CPSR and SPSR.

③ There is a unique ELR_Hyp register in Hyp mode.

Reference materials:

"Cortex M3 Definitive Guide (Chinese)"

"[Punctual Atom] i.MX6U Embedded Linux Driver Development Guide V1.3"