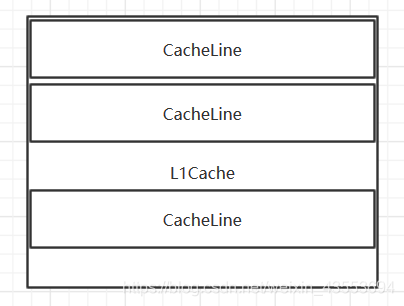

CacheLine

总所周知,计算机将数据从主存读入Cache时,是把要读取数据附近的一部分数据都读取进来

这样一次读取的一组数据就叫做CacheLine,每一级缓存中都能放很多的CacheLine

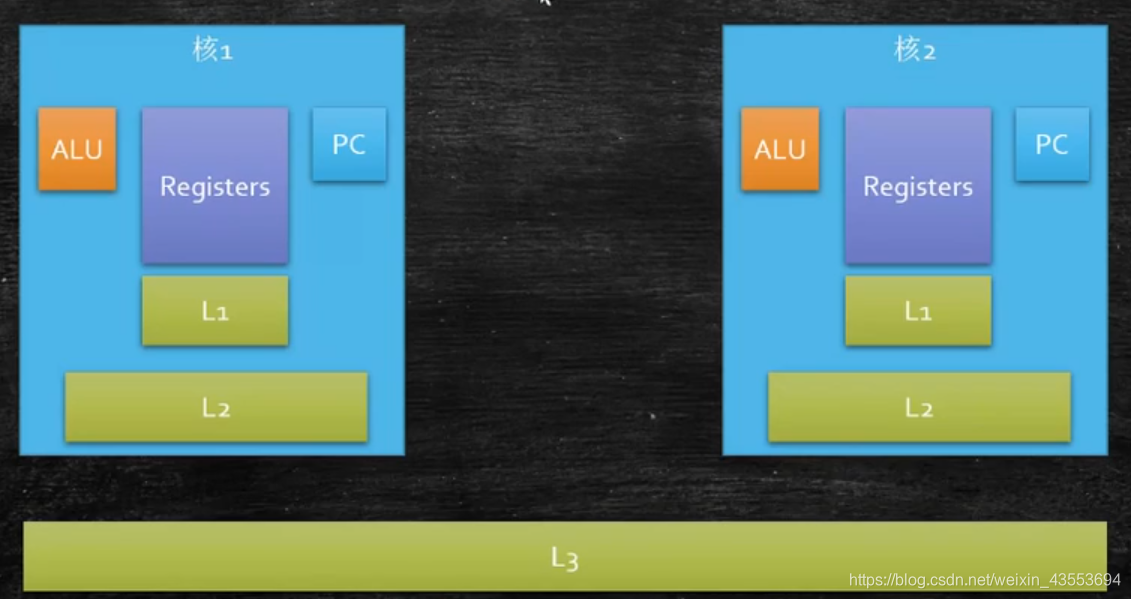

多核CUP

- L1、L2、L3指一级缓存,二级缓存,三级缓存

- CUP中的每个核均可单独处理一个线程

- 每个核公用L3

超线程

一个核中有多套PC和Register,他们公用一个ALU,这样一个核可以处理多个线程

如四核八线程就由此而来

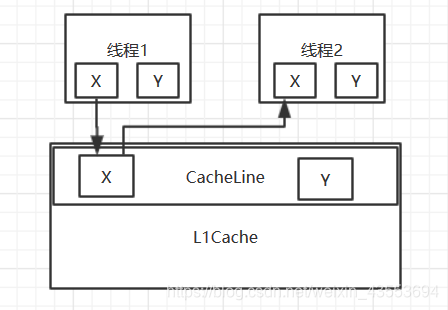

Volatile的可见性

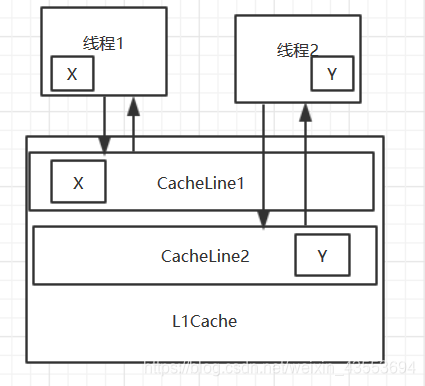

x被标记了volatile- 两个线程运算时是将缓存中要被运算数所在的整条CacheLine复制到线程自己的存储,并进行运算,运算之后写回缓存

- 假设

线程1修改了x并写回,但是线程2中的x还是未修改的x - 由于

x被标记了volatile,在线程1写回x缓存时,线程1会通知线程2重新读取缓存中的x

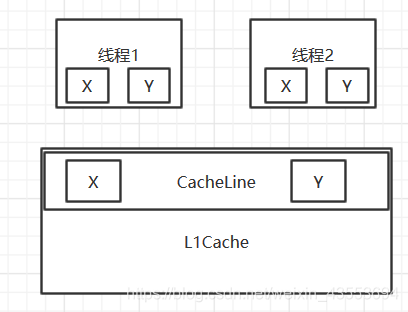

伪共享

线程1、2公共使用同一个CacheLinex、y在同一个CacheLinex、y都是volatile- 如果

线程1不断修改x,线程2不断修改y,那么修改的时候线程1就要不断通知线程2更新x、线程2就要不断通知线程1更新y - 这样的不断通知不断重新读取很浪费性能

- 这就叫伪共享

CacheLine对齐

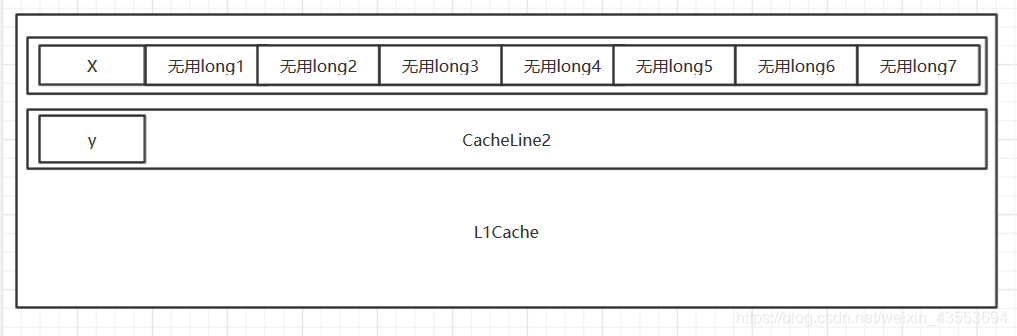

多线程会有上面的伪共享的问题,如果在缓存读取数据到CacheLine时,两个volatile的数被读取到不同的CacheLine中的话,就不需要一直通知另一个线程更新数据了,因为另一个线程根本没有这个数据

那么如何让两个数据一定在不同的CacheLine呢,方法就是Cache Line对齐

一般一个CacheLine是64位,也就是8个long,我们可以把x定义为long,并同时定义7个没有用的long变量,这样这8个数就在同一个CacheLine中

之后再定义y,y自然也就在下一个CacheLine中了

这就叫CacheLine对齐,这样两线程就不会出现伪共享的现象了

这就叫CacheLine对齐,这样两线程就不会出现伪共享的现象了