菜菜昨天在用quatus做FIFO模块和RAM模块时疯狂报错,加上完全不记得自己以前如何写的,问了很多同学才有了一点点印象,最后成功编译,且下载后现象也正确,那我们就赶紧先写下来吧,不然下次又忘了/(ㄒoㄒ)/~~

都是用lpm库来实现的

FIFO模块

先介绍一下FIFO

设计要求:

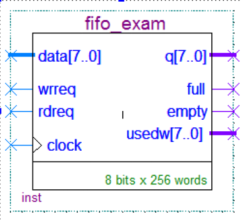

设计1个同步FIFO,8bits*256words

其最终图为:

- 创建项目(new project)----->命名为fifo_test

- 创建模块(选择文件模式)

- 点击空白两下,出现如下界面,点击红色方框

- 选择模块

首先在左边找到我们的FIFO,并选择(点击即可),再在右边路径中添加我们模块的名称

注意:不要和我们的工程名称相同 - 继续调整我们的模块

我们可以看到左边那个模块已经和我们期望的一致了,但是很多细节我们还是需要考虑一下的,比如右边的8和256代表输入位数及深度,可是我们下载到板子上输入一共只有8位拨码开关,故我们可以调整一下输入输出只有4位,然后256代表可以有256个字,由8位控制,我们也可以调整为一些小的方便控制

直接单击下一步

可选择勾选该同步清零,再点击下一步即可

直接下一步

勾选vhd文件,这样才会之后拥有,点击finish即可

点击OK,将其保存,注意文件名为工程文件名(也可任意),后缀为bdf

-

编译之前,先将输入输出调整好

编译没有错误之后将封装模块 -

File ----> Create/Update ------> Ceate Symbol File for current file

即可得到bsf文件

若是别的模块需要调用该模块,只需要将该文件夹里的bsf,bdf,vhd全部复制到我们的顶层文件夹即可,这样别的模块在封装的时候,可看到并且直接调用

FIFO模块的构建就完成啦

RAM模块

RAM模块与FIFO模块构建相似,主要是

我们要根据要求选择单端口或者其它的

同样也是选择位数和深度,一直next即可,直到finish

那我们的笔记就做完啦!