--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mux41_1 is

port (a,b,c,d,s1,s0:in std_logic;

y:out std_logic);

end mux41_1;

architecture Behavioral of mux41_1 is

signal n:std_logic_vector(1 downto 0);

begin

n<=s1&s0;

process(n)

begin

if n="00"then

y<=a;

elsif n="01"then

y<=b;

elsif n="10"then

y<=c;

elsif n="11"then

y<=d;

end if;

--注意elsif不需要end if

end process;

end Behavioral;

四选一,很简单。重点是elsif不用end if;

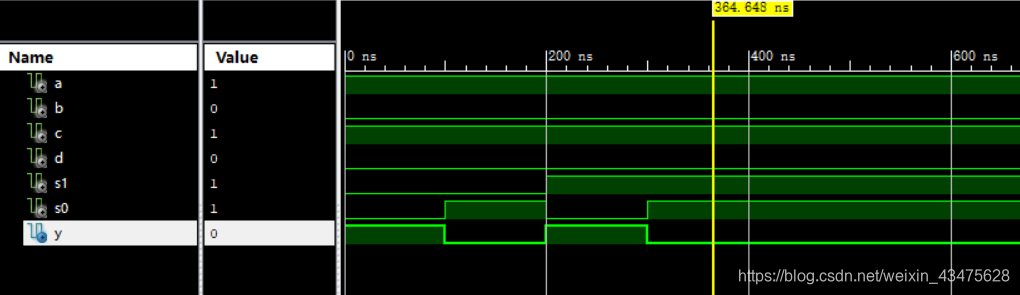

仿真:

用when_else

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mux41_1 is

port (a,b,c,d,s1,s0:in std_logic;

y:out std_logic);

end mux41_1;

architecture Behavioral of mux41_1 is

signal n:std_logic_vector(1 downto 0);

begin

n<=s1&s0;

y<=a when n="00" else

b when n="01"else

c when n="10"else

d when n="11"else

'0';

--a b c d这里没有;

end Behavioral;

注意点:when_else不能在process里面,a b c d这里没有;

用case写;

注意点:case n is when => y<=…;要写在process中!!

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mux41_1 is

port (a,b,c,d,s1,s0:in std_logic;

y:out std_logic);

end mux41_1;

architecture Behavioral of mux41_1 is

signal n:std_logic_vector(1 downto 0);

begin

process

begin

n<=s1&s0;

case n is

when "00" => y<=a;

when "01" => y<=b;

when "10" => y<=c;

when "11" => y<=d;

when others=>null;

end case;

end process;

end Behavioral;

仿真程序都一样:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY mux41_tb IS

END mux41_tb;

ARCHITECTURE behavior OF mux41_tb IS

COMPONENT mux41_1

PORT(

a : IN std_logic;

b : IN std_logic;

c : IN std_logic;

d : IN std_logic;

s1 : IN std_logic;

s0 : IN std_logic;

y : OUT std_logic

);

END COMPONENT;

signal a : std_logic := '0';

signal b : std_logic := '0';

signal c : std_logic := '0';

signal d : std_logic := '0';

signal s1 : std_logic := '0';

signal s0 : std_logic := '0';

signal y : std_logic;

BEGIN

uut: mux41_1 PORT MAP (

a => a,

b => b,

c => c,

d => d,

s1 => s1,

s0 => s0,

y => y

);

-- Stimulus process

stim_proc: process

begin

a<='1';b<='0';c<='1';d<='0';s1<='0';s0<='0';

wait for 100 ns;

a<='1';b<='0';c<='1';d<='0';s1<='0';s0<='1';

wait for 100 ns;

a<='1';b<='0';c<='1';d<='0';s1<='1';s0<='0';

wait for 100 ns;

a<='1';b<='0';c<='1';d<='0';s1<='1';s0<='1';

wait for 100 ns;

wait;

end process;

END;