以下-----废话

实验室要求学习FPGA,刚刚将VHDL的基本语法和一些基础时序组合器件看完,迫不及待上手进行操作。

上网查了很多实用ISE的工程建立,很多感觉不是很全面,书上讲的再多也不如自己实际操作一遍来的快,决定自己写一个记录,尽可能详细,防止自己以后忘了,发现查的再多也不如自己去查他的datasheet来的快(尽管他是英文的),而且他写的很详细,有很多种工作模式,有可能别的文章只会提一两种,所以还是自己踏实的刷几遍datasheet才好。自己也是初学者,欢迎大家交流。

本来是想写一个流水灯的,但是还没有弄明白板子上的3个时钟,还有怎么分频(emmm,其实是想要得到1s,要分66M分频,怎么建立这么大的常数,直接std_logic_vector(32 downto 0)?? 32这个数太大了是不是很占资源)欢迎大家交流。~注意:没有进行时序仿真的流程0.0

系统:WIN10, 开发平台:ISE 14.7(至于怎么改兼容,上网搜一下就好)

硬件平台:Virtex-6 FPGA ML605开发板

项目描述:利用板子上的8个拨码开关,分别控制8个LED的亮灭。程序很简单只有一行,就是为了熟练创建工程。

以下-----正文

1.创建工程

首先打开ISE14.7,File----New Project创建一个工程,就叫他LED_demo吧,然后直接Next。

然后嘞,选择板子型号,选择仿真器,综合器,VHDL。

直接点Next,然后Finish完成创建。

在这里,由于我是ML605系列的开发板,我就向下面这样选了。

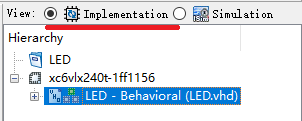

2.编写我们的VHDL文件。

首先创建一个新的VHDL module文件用来装我们的主要程序代码。点击1处创建新的文件,选择 VHDL module,名字还叫这个吧。

之后,会让你填一下你这个VHDL文件中需要用到哪些port,就是这个器件的所有I/O口,你可以不在这里写,直接在程序里打也可以,不过在这里比较方便。我们只用到前面8个KEY,用来设定拨码开关输入的,最后一个是举个例子,不是程序里的。

然后呢,我们就得到这张列表,使我们要创建的port,点击Finish。

这样我们就能很快的得到下面这样的程序框架,之后我们试着打程序,在Port里,接着添加out 的类型port,加上8个LED。

最后程序就是这个样子,保存就可以了。

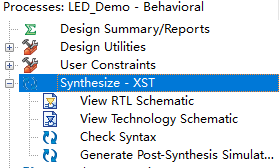

3.综合(Synthesize)

使用ISE自带的综合工具XST进行综合,综合工具可以让设计者从更加接近系统概念模型的角度来设计系统,而不用直接写很底层的门级别语言(0.0 咳NOT就是非门的原语,本身就是个例子,不要做那么复杂0.o),不多说直接上图。

这里可以直接双击Synthesize进行综合,这一下就把下面两项语法检查,生成模型都做了。

View RTL schematic(查看RTL原理图)

View Technology Schematic(查看技术原理图),可以看一下自己生成模块的样子。

Check Syntax(检查语法)

Generate Post-Synthesis Simulation Model(产生综合后仿真模型)

4.仿真(Simulation)

首先在Design栏选择Simulation,然后对着之前的LED_Demo文件右键,选择New Sourse。

选择 VHDL Test Bench 文件类型,创建一个测试文件。之后Next,Finish,创建完成。由于是个很简单的程序,而且没有时钟,所以就没有做时序仿真0.0_咳

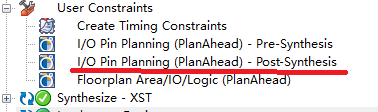

5.添加约束文件

也就是引脚的分配。好,Disign栏回到Implementation,然后在User Constraints 中 选择 I/OPinPlanning(PlanAhead)-Post-Synthesis。

出现一个对话框,点Yes,这样就会打开另一个软件 PlanAhead。然后在里面对里面LED和KEY管脚进行配置。

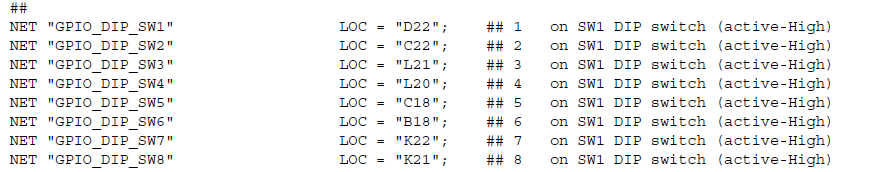

这里具体板子上哪个I/O口是干什么的,要去官网查具体的手册,ML605板子要查ML605 Hardware User Guide手册。这里是ML605板子的拨码开关引脚和LED的。

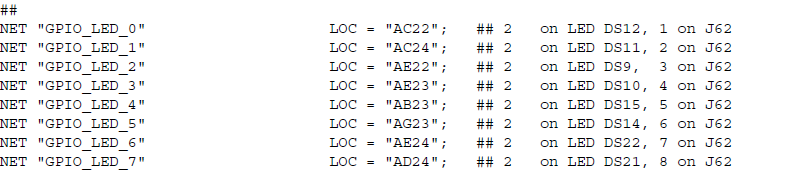

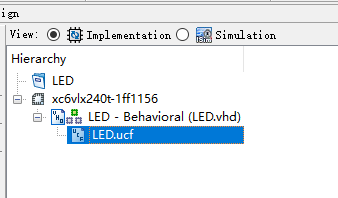

在PlanAhead软件上给所有引脚规定了以后,保存文件。就会在ISE中工程中自动生成一个.ucf文件。

6.实现(implementation)和生成bit下载烧录文件

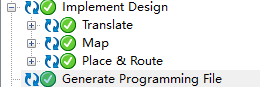

实现包括翻译,映射,布线布局,都是将编写的系统级程序翻译映射门级别电路图然后FPGA来实现,由程序自动完成,双击一下 Implement Design等都绿了就行了。

然后双击Generate Programming Files 生成bit流文件,用于一会下载。

7.下载验证(下面操作必须连上FPGA才可以)

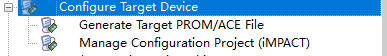

最后一部分了,双击Configure Target Device ,出现一个对话框点OK,就会打开iMPACT下载软件。

然后在下图中间右键,生成链表。

生成下图的链表以后,双击那个下面有FPGA型号的芯片,不要选那个xccace!然后找到生成的bit文件双击。之后询问你是否烧录到PROM里,点NO就行了。

最后点Program,下载程序,出现一个进度条,最后完成,大功告成!

到这里就已经算完成了,放张实物图吧。。

整个工程我放在了GitHub上,上面还有一些其他的FPGA小设计,欢迎大家交流.