1.AXI_GPIO应用场合

(1)AXI GPIO模块将PL端连接的GPIO信号通过AXI接口与PS模块连接,PS通过AXI接口的地址映射对PL端的GPIO信号进行读写等控制,与EMIO可以实现相同的功能,区别主要在于EMIO对于少数GPIO接口进行单独的控制,而AXI GPIO可以对多个GPIO接口合并成的总线进行整体读写控制;

(2)PS端可以借助AXI GPIO模块给PL逻辑生成一些通知信号;

(3)PL逻辑可以借助AXI GPIO模块给PS生成中断通知信号,但是必须使能AXI GPIO模块中断功能。

2.AXI_GPIO控制器框图

由下图可以知道AXI GPIO控制器有AXI Interface Module(AXI接口模块)、Interrupt Module(中断模块)、GPIO Core三大模块组成,从图中可以看出AXI GPIO控制器中断模块只针对输入信号(核心)。

(1)AXI Interface Module使用AXI_Lite接口和ZYNQ PS端的GP Master接口互联,PS用GP接口可以读写AXI GPIO控制器内部的寄存器,从而控制AXI GPIO控制器输入输出;

(2)Interrupt Module检测外部两个通道的输入信号(每个通道可以结合PL配置为32路三态门IO接口[输入、输出、高阻]),当检测到外部两个通道任何一个通道的任何一个输出发送上升沿或者下降沿时,都会由IP2INTC_Irpt端口生成一个中断给PS;

(3)GPIO Core为IPIC接口和AXI GPIO输入输出通道提供了一个转换接口,GPIO Core由读写寄存器和多路复用器组成,他还包括了必须的逻辑去生成一个中断事件,当一个输入状态改变时。下图为GPIO Core框图。

3.AXI_GPIO控制器所有寄存器描述及地址映射

(1)GPIO_DATA寄存器解释如下,当GPIO作为输入时,PS可以读其管教状态,写无效;当GPIO作为输出时,PS可以写其管教状态,读无效。

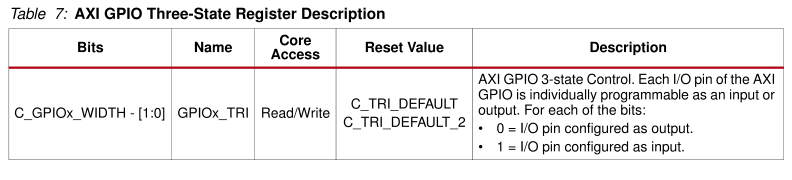

(2)GPIO_TRI(三态寄存器)寄存器解释如下,当为PS配置该位为0时,引脚作为输出,当为PS配置该位为1时,引脚作为输入。

(3)GIER寄存器(全局中断使能寄存器)解释如下,当为PS配置该位为0时,禁止AXI GPIO控制器产生中断,当为PS配置该位为1时,使能AXI GPIO控制器产生中断。也就是PS要想接收AXI GPIO中断,该位必须配置为1。

(4)IP IER寄存器(IP中断使能寄存器)解释如下,说白了就是可以单独控制哪一个通道中断打开与禁止。

(5)IP ISR寄存器(IP中断状态寄存器)解释如下,当发生中断时,PS可以查询这个寄存器来判断是通道1还是通道2发生的中断。

(7)寄存器地址映射如下

4.AXI_GPIO控制器配置及PS驱动

AXI_GPIO控制器详解(2)将结合本编文章详解AXI_GPIO控制器IP配置及PS中断配置及中断入口函数的编写及原理。