Xilinx Virtex-5 配置过程

作者:AirCity 2020.2.2

[email protected] 本文所有权归作者Aircity所有

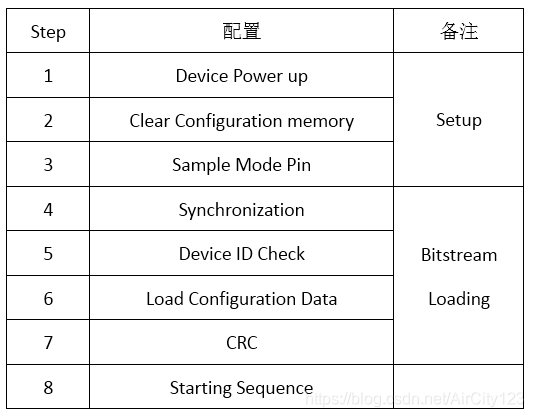

Xilinx FPGA的芯片是基于SRAM工艺制作,不具备非易失性。因此必须从外部非易失性存储器中获取配置文件后,才能正常工作。它的配置过程如下:

1. Device Power-up

保证相应的Bank都已经上电,如VCCINT,VCC0_X,VCCAUX.其中要求VCCINT≥1.0V;VCC0_2≥2.5V。在完成上电后,Done信号拉低,INIT信号被内部拉低。

解释:

VCCINT:核电压,由器件工艺决定,1V,1.5V,1.8V

VCC0_X:IO电压,存储逻辑单元电压

VCCAUX:辅助电压,为configuration logic模块供电

2. Clear Configuration Memory

清除FPGA内配置文件,清除RAM内容,清除完成后,INIT信号被内部拉高。

注意:INIT信号和PROG信号可以用来延长清空配置存储器的时长。

PROG:信号被外部拉低后,FPGA会被重新配置。

INIT:在RAM清除完成后,进入Step3之前,INIT是一个输入管脚,如果被外部拉低,配置过程将处于hold状态。在完成Step3之后,INIT会变为OD输出,指示是否有CRC错误(低电平)。

3. Sample Mode Pin

采样配置管脚M[2:0],FS[2:0],RCMD[7:0]的值。

4. Synchronization

位宽同步,位宽信息在bitstream里面,同步字载入FPGA Configruation Logic。

5. Device ID Check

检查FPGA内部的ID,不同型号的FPGA bitstream对应的ID不同

6. Load Configuration Data

开始加载配置数据

7. CRC

计算CRC,并且与bitstream里的CRC值比较,要求一致。如果不一样,会拉低INTI,进入fallback,resynchronized,从step2再开始。如果还不一样,则restart configuration,从step1开始。

8. Starting Sequence

Done信号拉高,否则数据加载肯定失败了。

配置过程中,器件所有状态都是三态。之后,全局三态信号GTS(V5寄存器)置低,IO会从三态切换到用户设定的状态。

全局复位信号GSR置低,所有触发器进入工作状态。

全局写允许信号GWE置低,所欲内部RAM有效。

启动过程需要8个时钟周期C0-C7,这些与配置时钟Clock同步。在Done信号拉高之前,GTS,GSR,GWE都保持高电平。如果用JTAG配置,所有操作与TCKtongue。

Xilinx常用配置电路:

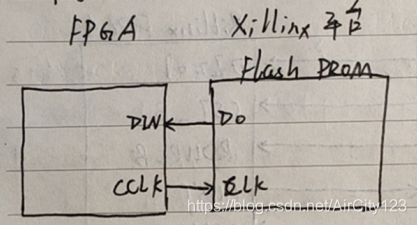

主串行:

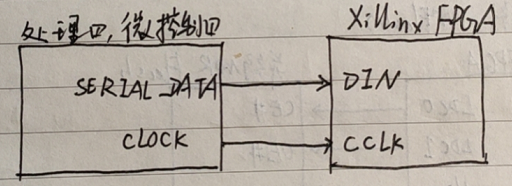

从串行:

主并行:

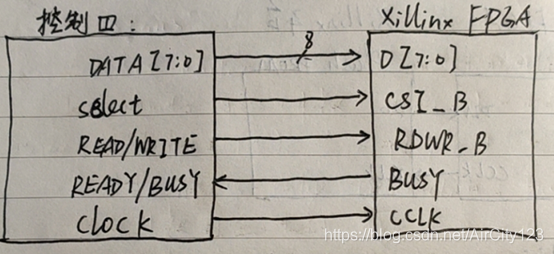

从并行:

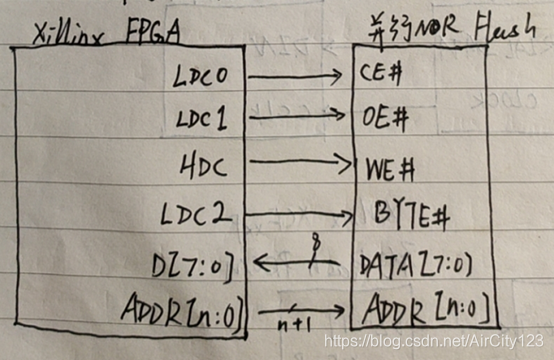

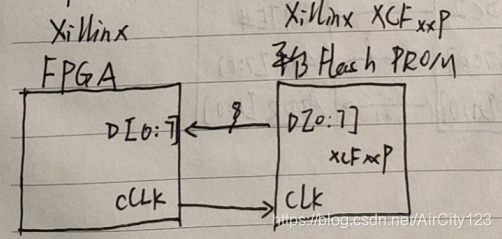

主BPI(并行Nor Flash)