1.HDMI是新一代的多媒体接口标准。

High-Definition Multimedia Interface:高清多媒体接口

能够同时传输视频和音频,简化了设备的接口和连线;

提供了更高的数据传输带宽,可以传输无压缩的数字音频及高分辨率视频信号;

下面是HDMI线公头和母头示意图:

2.HDMI向下兼容DVI

DVI(数字视频接口)只能用来传输视频,而不能同时传输音频;

DVI和HDMI接口协议在物理层均使用TMDS标准传输音视频数据。

下面是DVI和HDMI接口示意图:

3.TMDS: 最小化传输差分信号

Transition Minimized Differential Signaling

TMDS是Silicon Image公司开发的一项高速数据传输技术,在DVI和HDMI视频接口中使用差分信号传输高速串行数据。

TMDS差分传输技术使用两个引脚来传输一路信号,利用这两个引脚间的电压差的正负极性和大小来决定传输数据的数值(0或1)。

DVI或HDMI视频传输所使用的TMDS连接通过四个串行通道实现,

独立的TMDS时钟通道为接收端提供接收的参考频率,保证数据在接收端能够正确恢复。

TMDS连接从逻辑功能上可以划分成两个阶段:“编/解码” 和 “并/串转换” 。

在编码阶段,编码器将视频源中的像素数据、HDMI的音频/附加数据,以及行同步和场同步信号分别编码成10位的字符流。

在并串转换阶段将上述的10位字符流转换成串行数据流,并将其从三个差分输出通道发送出去。

这个10:1的并转串过程所生成的串行数据速率是实际像素时钟速率的10倍。

如下图所示:

4.TMDS编码算法

TMDS和LVDS、TTL相比有较好的电磁兼容性能:

这种算法可以减小传输信号过程的上冲和下冲;

而DC平衡使信号对传输线的电磁干扰减少;

可以用低成本的专用电缆实现长距离、高质量的数字信号传输。

5.HDMI模块框图

CEC: Consumer Electronics Control 用户电气控制

DDC:用来获取被接设备的信息EDID(

扩展显示标识数据

)

CEC线在HDMI插上的可以控制从设备的一些状态,比如开机

DDC是IIC接口,可以结合HDMI的19管脚(热拔插信号)来读取被接设备的一些有用信息,比如分辨率。FPGA检测到显示器后可以通过DDC读取显示器的分辨率,从而达到智能识别分辨率,FPGA设备可以根据分辨率调整输出(比如我们把笔记本的HDMI接到1080p的显示器和720p的显示器笔记本的输出会自己做调整适应不同的显示器)

6.HDMI引脚定义

7.程序设计

下面是程序框图

众所周知,HDMI既可以传输视频信号,也可以传输音频信号,FPGA产生的Video Source经过TMDS编码算法和CTRL编码算把三组RGB数据、HS、VS信号进行编码,编码过后的10bit数据需要并串转换模块Serializer把并行的10bit信号发送出去,这里Serializer用的FPGA的OSERDESE2原语,并要使能DDR功能(因为我们给的时钟是5倍时钟,所以要使能双倍数据速率)。这样HDMI接收端只会接收到源的视频信号,如果需要传输音频信号,则需要FPGA产生Audio data并且需要TERC4算法进行编码发送,这里我也没研究。Video Source是标准的VGA时序,只是多了一个VDE(Video Data Enable)信号,也就是VGA的数据使能信号。时钟信号是把标准的10'b11110_00000的数据通过OSERDESE2进行并串转换输出就是真实的时钟。

这样我们FPGA程序需要以下模块:

1.VGA生成模块

2.TMDS和CTRL编码模块(需要例化三对)

3.并串转换模块(需要例化四对)

4.单端转差分模块(需要例化四对)

5.顶层模块

1.VGA时序生成模块

module video_driver(

input pixel_clk,

input sys_rst_n,

//RGB接口

output video_hs, //行同步信号

output video_vs, //场同步信号

output video_de, //数据使能

output [23:0] video_rgb, //RGB888颜色数据

input [23:0] pixel_data, //像素点数据

output [10:0] pixel_xpos, //像素点横坐标

output [10:0] pixel_ypos //像素点纵坐标

);

//parameter define

//1280*720 分辨率时序参数

parameter H_SYNC = 11'd40; //行同步

parameter H_BACK = 11'd220; //行显示后沿

parameter H_DISP = 11'd1280; //行有效数据

parameter H_FRONT = 11'd110; //行显示前沿

parameter H_TOTAL = 11'd1650; //行扫描周期

parameter V_SYNC = 11'd5; //场同步

parameter V_BACK = 11'd20; //场显示后沿

parameter V_DISP = 11'd720; //场有效数据

parameter V_FRONT = 11'd5; //场显示前沿

parameter V_TOTAL = 11'd750; //场扫描周期

//reg define

reg [10:0] cnt_h;

reg [10:0] cnt_v;

//wire define

wire video_en;

wire data_req;

//*****************************************************

//** main code

//*****************************************************

assign video_de = video_en;

assign video_hs = ( cnt_h < H_SYNC ) ? 1'b0 : 1'b1; //行同步信号赋值

assign video_vs = ( cnt_v < V_SYNC ) ? 1'b0 : 1'b1; //场同步信号赋值

//使能RGB数据输出

assign video_en = (((cnt_h >= H_SYNC+H_BACK) && (cnt_h < H_SYNC+H_BACK+H_DISP))

&&((cnt_v >= V_SYNC+V_BACK) && (cnt_v < V_SYNC+V_BACK+V_DISP)))

? 1'b1 : 1'b0;

//RGB888数据输出

assign video_rgb = video_en ? pixel_data : 24'd0;

//请求像素点颜色数据输入

assign data_req = (((cnt_h >= H_SYNC+H_BACK-1'b1) &&

(cnt_h < H_SYNC+H_BACK+H_DISP-1'b1))

&& ((cnt_v >= V_SYNC+V_BACK) && (cnt_v < V_SYNC+V_BACK+V_DISP)))

? 1'b1 : 1'b0;

//像素点坐标

assign pixel_xpos = data_req ? (cnt_h - (H_SYNC + H_BACK - 1'b1)) : 11'd0;

assign pixel_ypos = data_req ? (cnt_v - (V_SYNC + V_BACK - 1'b1)) : 11'd0;

//行计数器对像素时钟计数

always @(posedge pixel_clk ) begin

if (!sys_rst_n)

cnt_h <= 11'd0;

else begin

if(cnt_h < H_TOTAL - 1'b1)

cnt_h <= cnt_h + 1'b1;

else

cnt_h <= 11'd0;

end

end

//场计数器对行计数

always @(posedge pixel_clk ) begin

if (!sys_rst_n)

cnt_v <= 11'd0;

else if(cnt_h == H_TOTAL - 1'b1) begin

if(cnt_v < V_TOTAL - 1'b1)

cnt_v <= cnt_v + 1'b1;

else

cnt_v <= 11'd0;

end

end

endmodule2.TMDS和CTRL编码模块(需要例化三对)

dvi_encoder encoder_b (

.clkin (pclk),

.rstin (reset),

.din (video_din[7:0]),

.c0 (video_hsync),

.c1 (video_vsync),

.de (video_de),

.dout (blue_10bit)

) ;

dvi_encoder encoder_g (

.clkin (pclk),

.rstin (reset),

.din (video_din[15:8]),

.c0 (1'b0),

.c1 (1'b0),

.de (video_de),

.dout (green_10bit)

) ;

dvi_encoder encoder_r (

.clkin (pclk),

.rstin (reset),

.din (video_din[23:16]),

.c0 (1'b0),

.c1 (1'b0),

.de (video_de),

.dout (red_10bit)

) ;3.并串转换模块(需要例化四对)

//对编码后的数据进行并串转换

serializer_10_to_1 serializer_b(

.reset (reset), // 复位,高有效

.paralell_clk (pclk), // 输入并行数据时钟

.serial_clk_5x (pclk_x5), // 输入串行数据时钟

.paralell_data (blue_10bit), // 输入并行数据

.serial_data_out (tmds_data_serial[0]) // 输出串行数据

);

serializer_10_to_1 serializer_g(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (green_10bit),

.serial_data_out (tmds_data_serial[1])

);

serializer_10_to_1 serializer_r(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (red_10bit),

.serial_data_out (tmds_data_serial[2])

);

serializer_10_to_1 serializer_clk(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (clk_10bit),

.serial_data_out (tmds_clk_serial)

);4.单端转差分模块(需要例化四对)

//转换差分信号

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS0 (

.I (tmds_data_serial[0]),

.O (tmds_data_p[0]),

.OB (tmds_data_n[0])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS1 (

.I (tmds_data_serial[1]),

.O (tmds_data_p[1]),

.OB (tmds_data_n[1])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS2 (

.I (tmds_data_serial[2]),

.O (tmds_data_p[2]),

.OB (tmds_data_n[2])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS3 (

.I (tmds_clk_serial),

.O (tmds_clk_p),

.OB (tmds_clk_n)

);

5.顶层模块

module hdmi_colorbar_top(

input sys_clk,

input sys_rst_n,

output tmds_clk_p, // TMDS 时钟通道

output tmds_clk_n,

output [2:0] tmds_data_p, // TMDS 数据通道

output [2:0] tmds_data_n,

output tmds_oen // TMDS 输出使能,0:表示是HDMI输入 1:表示是HDMI输出

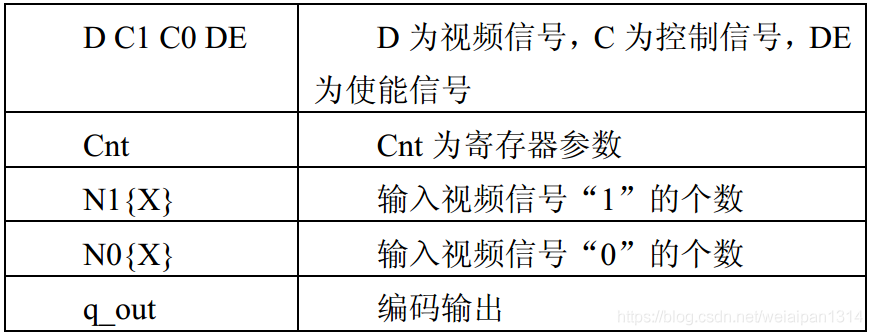

);附录(TMDS编码算法):

此算法可以自己研究。

module dvi_encoder (

input clkin, // pixel clock input

input rstin, // async. reset input (active high)

input [7:0] din, // data inputs: expect registered

input c0, // c0 input

input c1, // c1 input

input de, // de input

output reg [9:0] dout // data outputs

);

////////////////////////////////////////////////////////////

// Counting number of 1s and 0s for each incoming pixel

// component. Pipe line the result.

// Register Data Input so it matches the pipe lined adder

// output

////////////////////////////////////////////////////////////

reg [3:0] n1d; //number of 1s in din

reg [7:0] din_q;

//计算像素数据中“1”的个数

always @ (posedge clkin) begin

n1d <=#1 din[0] + din[1] + din[2] + din[3] + din[4] + din[5] + din[6] + din[7];

din_q <=#1 din;

end

///////////////////////////////////////////////////////

// Stage 1: 8 bit -> 9 bit

// Refer to DVI 1.0 Specification, page 29, Figure 3-5

///////////////////////////////////////////////////////

wire decision1;

assign decision1 = (n1d > 4'h4) | ((n1d == 4'h4) & (din_q[0] == 1'b0));

wire [8:0] q_m;

assign q_m[0] = din_q[0];

assign q_m[1] = (decision1) ? (q_m[0] ^~ din_q[1]) : (q_m[0] ^ din_q[1]);

assign q_m[2] = (decision1) ? (q_m[1] ^~ din_q[2]) : (q_m[1] ^ din_q[2]);

assign q_m[3] = (decision1) ? (q_m[2] ^~ din_q[3]) : (q_m[2] ^ din_q[3]);

assign q_m[4] = (decision1) ? (q_m[3] ^~ din_q[4]) : (q_m[3] ^ din_q[4]);

assign q_m[5] = (decision1) ? (q_m[4] ^~ din_q[5]) : (q_m[4] ^ din_q[5]);

assign q_m[6] = (decision1) ? (q_m[5] ^~ din_q[6]) : (q_m[5] ^ din_q[6]);

assign q_m[7] = (decision1) ? (q_m[6] ^~ din_q[7]) : (q_m[6] ^ din_q[7]);

assign q_m[8] = (decision1) ? 1'b0 : 1'b1;

/////////////////////////////////////////////////////////

// Stage 2: 9 bit -> 10 bit

// Refer to DVI 1.0 Specification, page 29, Figure 3-5

/////////////////////////////////////////////////////////

reg [3:0] n1q_m, n0q_m; // number of 1s and 0s for q_m

always @ (posedge clkin) begin

n1q_m <=#1 q_m[0] + q_m[1] + q_m[2] + q_m[3] + q_m[4] + q_m[5] + q_m[6] + q_m[7];

n0q_m <=#1 4'h8 - (q_m[0] + q_m[1] + q_m[2] + q_m[3] + q_m[4] + q_m[5] + q_m[6] + q_m[7]);

end

parameter CTRLTOKEN0 = 10'b1101010100;

parameter CTRLTOKEN1 = 10'b0010101011;

parameter CTRLTOKEN2 = 10'b0101010100;

parameter CTRLTOKEN3 = 10'b1010101011;

reg [4:0] cnt; //disparity counter, MSB is the sign bit

wire decision2, decision3;

assign decision2 = (cnt == 5'h0) | (n1q_m == n0q_m);

/////////////////////////////////////////////////////////////////////////

// [(cnt > 0) and (N1q_m > N0q_m)] or [(cnt < 0) and (N0q_m > N1q_m)]

/////////////////////////////////////////////////////////////////////////

assign decision3 = (~cnt[4] & (n1q_m > n0q_m)) | (cnt[4] & (n0q_m > n1q_m));

////////////////////////////////////

// pipe line alignment

////////////////////////////////////

reg de_q, de_reg;

reg c0_q, c1_q;

reg c0_reg, c1_reg;

reg [8:0] q_m_reg;

always @ (posedge clkin) begin

de_q <=#1 de;

de_reg <=#1 de_q;

c0_q <=#1 c0;

c0_reg <=#1 c0_q;

c1_q <=#1 c1;

c1_reg <=#1 c1_q;

q_m_reg <=#1 q_m;

end

///////////////////////////////

// 10-bit out

// disparity counter

///////////////////////////////

always @ (posedge clkin or posedge rstin) begin

if(rstin) begin

dout <= 10'h0;

cnt <= 5'h0;

end else begin

if (de_reg) begin

if(decision2) begin

dout[9] <=#1 ~q_m_reg[8];

dout[8] <=#1 q_m_reg[8];

dout[7:0] <=#1 (q_m_reg[8]) ? q_m_reg[7:0] : ~q_m_reg[7:0];

cnt <=#1 (~q_m_reg[8]) ? (cnt + n0q_m - n1q_m) : (cnt + n1q_m - n0q_m);

end else begin

if(decision3) begin

dout[9] <=#1 1'b1;

dout[8] <=#1 q_m_reg[8];

dout[7:0] <=#1 ~q_m_reg[7:0];

cnt <=#1 cnt + {q_m_reg[8], 1'b0} + (n0q_m - n1q_m);

end else begin

dout[9] <=#1 1'b0;

dout[8] <=#1 q_m_reg[8];

dout[7:0] <=#1 q_m_reg[7:0];

cnt <=#1 cnt - {~q_m_reg[8], 1'b0} + (n1q_m - n0q_m);

end

end

end else begin

case ({c1_reg, c0_reg})

2'b00: dout <=#1 CTRLTOKEN0;

2'b01: dout <=#1 CTRLTOKEN1;

2'b10: dout <=#1 CTRLTOKEN2;

default: dout <=#1 CTRLTOKEN3;

endcase

cnt <=#1 5'h0;

end

end

end

endmodule