MCS-51硬件结构

具有CPU,RAM,ROM,定时/计数器以及IO口等基本功能

引脚

按功能可分为三类:数据总线,地址总线和控制总线.

- VCC

电源正极 - GND

电源负极 - XTAL1,XTAL2

用于外接时钟电路引脚 - RST

复位信号输入.当RST保持两个机器周期的高电平时,单片机复位 - ALE

地址锁存允许信号.访问外部存储器时锁存P0传输的低8位地址 - PSEN

外部程序存储器的读选通信号.在访问外部ROM时发出负脉冲作为通选信号 - EA

访问外部程序存储器控制信号.控制内外部ROM读取 - IO

P0:双向IO 或 外部存储器低8位地址

P1:双向IO

P2:双向IO 或 外部存储器高8位地址

P3:双向IO 或 第二功能

CPU

运算器

ALU

ACC

执行加减运算

B

执行乘除运算.

乘法:乘数取自A和B,结果A存低字节,B存高字节

除法:A存被除数,B存除数;结果商存A,余数存B

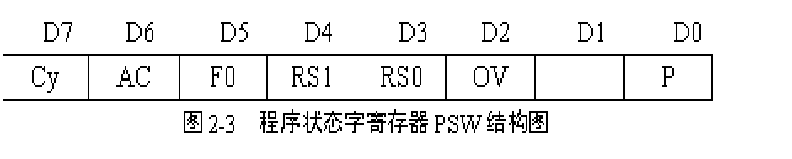

PSW

-

Cy:进位标志位.执行加减法是,最高为有进位或借位置1,否则清零.

-

AC:半进位标志位.标志低半字节向高半字节的进位或借位

-

F0:自定义

-

RS1 & RS0:工作寄存器组选择

4组R0-R7,对应内部RAM的00H-1FH共32位 -

OV:溢出标志位.补码运算溢出标志

-

P:奇偶检校位.对ACC内数据的奇偶检校

暂存器

暂存进入运算器前的数据

控制器

| PC | 程序计数器.16位地址寄存器,存放下一条要执行指令的地址.不属于SFR. |

|---|---|

| SP | 堆栈指针.指明片内RAM中开辟堆栈顶,默认07H |

| IR | 指令寄存器.对要执行的指令的存储及译码 |

| DPRT | 数据指针.两个8位寄存器DPH,DPL构成的SFR,用于外接RAM取址 |

位处理器

存储器

程序存储器

程序存储在ROM中.MCS-51共有两块ROM区,分别为片内4Kb 和片外64Kb,逻辑上统一编址,也就是片内和片外ROM前4Kb地址相同,在物理上用EA引脚电平区分.

特殊地址如下:

写入程序时不可覆盖这些特数地址,一般需要在00H处用伪指令跳转

数据存储器

片内RAM

-

工作寄存器

00H-1FH共32字节,在PSW中选定

-

位寻址

20H-2FH共16字节,128位.每一位都有其位地址.

MCS-51共有两部分可位寻址,一个是位寻址区,另一个是部分SFR.

-

数据缓冲区

30H-7FH,共80字节.一般将堆栈区开在数据缓冲区.

SP的默认初值为07H,位于工作寄存器区,需要人为设定SP的地址.

-

SFR

80H-FFH,共11字节

其中只有地址可以被8整除的寄存器可以进行位寻址.

片外RAM

0000H-FFFFH,16位地址

IO

时序

- 时钟周期

定义为系统时钟脉冲频率fosc的倒数 - 状态周期

2个时钟周期称为一个状态周期 - 机器周期

6个状态周期称为一个机器周期,也就是12个时钟周期称为一个机器周期 - 指令周期

执行一条指令所需要的时间