1. 使用DVE进行Debug

PPT1 课程目标

Unit Objectives

Learn to use basic features for debugging RTL

An introduction to the basic features

'Waveform debugging 、

Source code debugging

Listing features

Assertions

''C/C+ + " debugger

Analyzing design components

'Memories, busses, gates

仿真的log文件和波形结合效率比较高

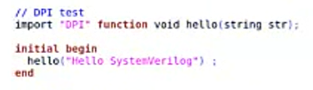

PPT2 DVE提供的文档

问题搞不定的时候,google

2. DVE介绍

PPT1 DVE的特性

DVE (Discovery Visual Environment)

■ An intuitive and easy to use GUI

■ Quickly Find Bugs

• RTL or Gates

• Assertions

• Testbench

■ Supports

• Interactive(设计验证初期,互动的模式,验证收敛的时候)

• Post-simulation analysis(随机测试,脚本调用命令)

■ Multiple Languages

• Verilog

• VHDL

• SystemVerilog

• SystemC

• C/C++

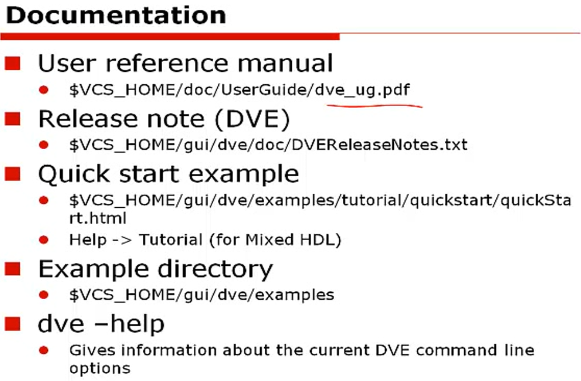

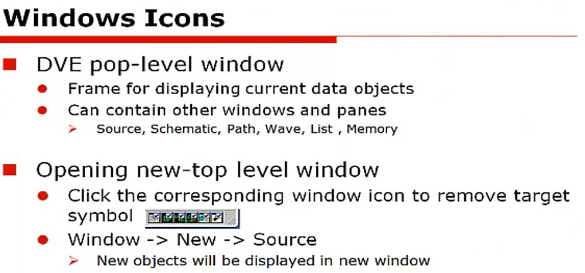

PPT2 DVE的界面

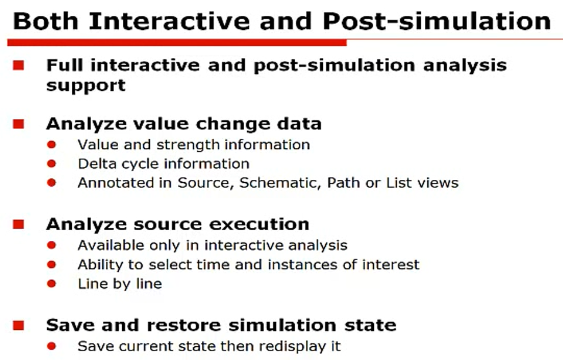

PPT3 交互式和后仿真

Annotated标注

PPT4

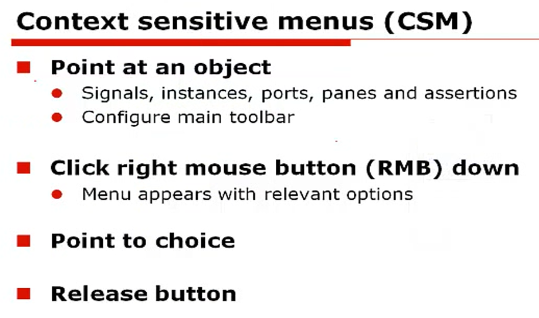

上下文相关菜单

3. DVE的启动

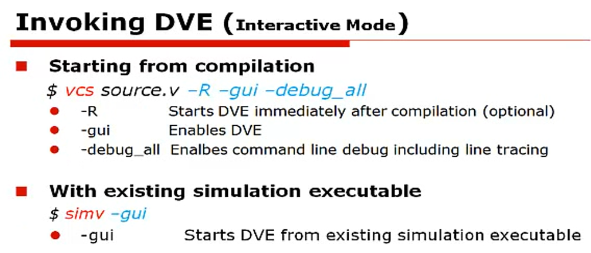

PPT1

PPT2

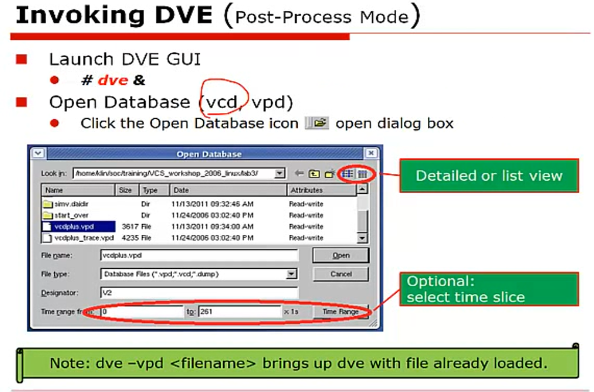

老的波形文件存储为vcd格式,占用空间比较大,后面改进为vpd占用空间比较小,加载的内存也小

verdi用的是fsdb,主流的是vcd和vpd

&后台执行的方式

PPT3

和windows下面的选项

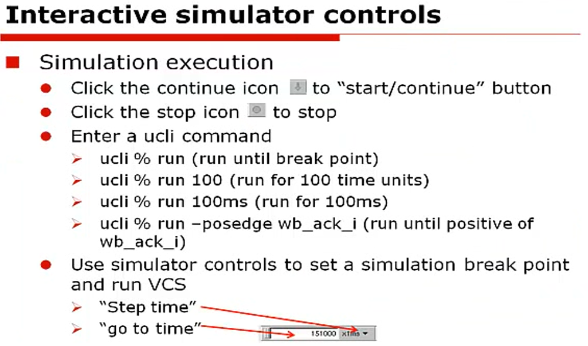

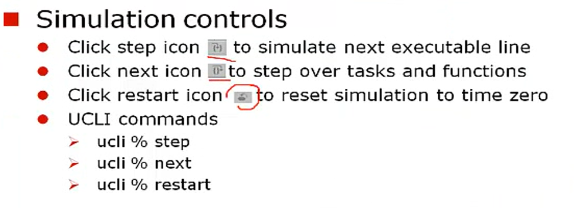

4. 交互式仿真

PPT1

PPT2

单步调试设置断点

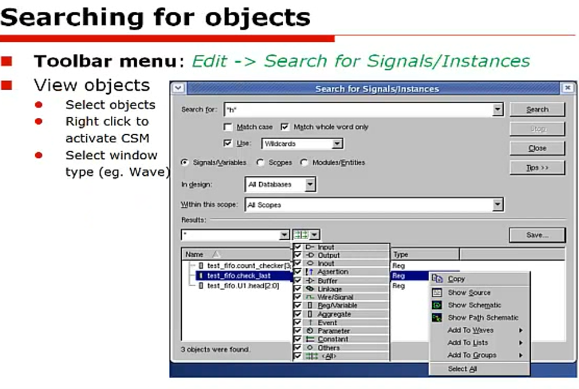

5. 文件的查找

6. 波形的窗口

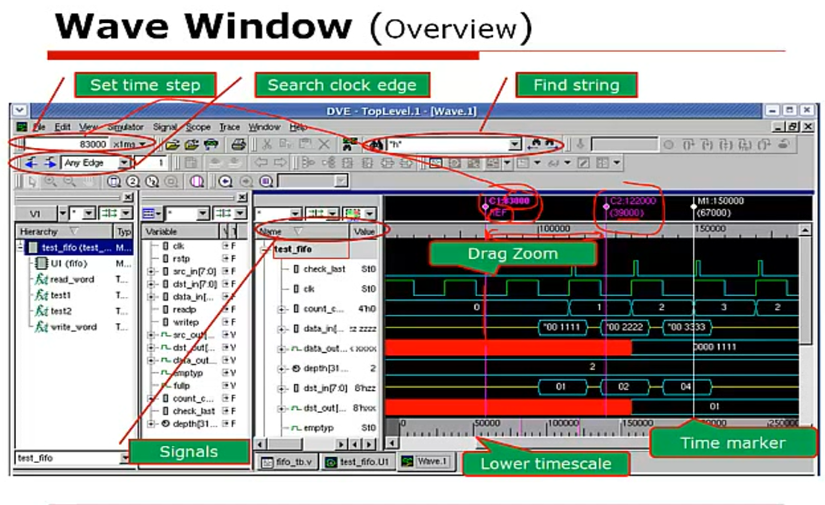

PPT1

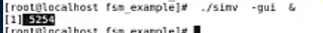

可以对仿真的步长设置,查找时钟边缘,查找变量

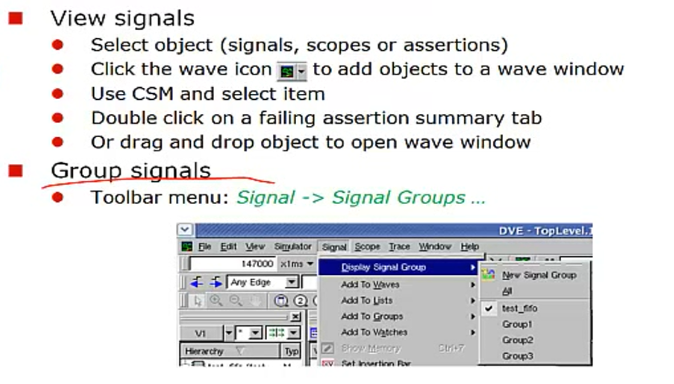

PPT2

对信号分组

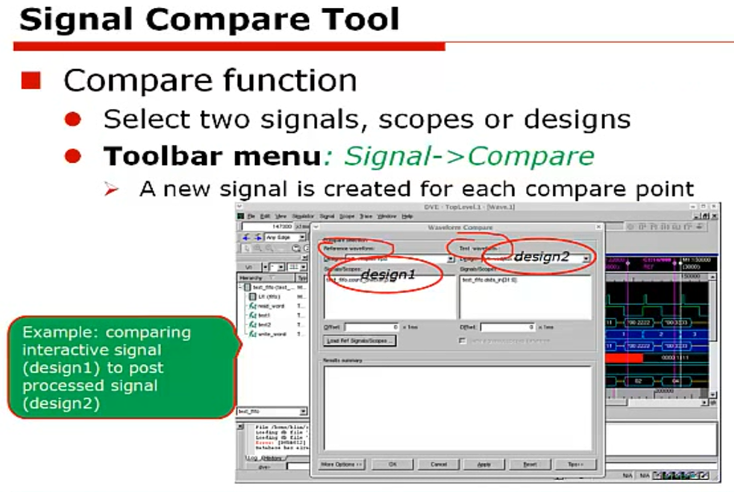

PPT3

对信号的比较

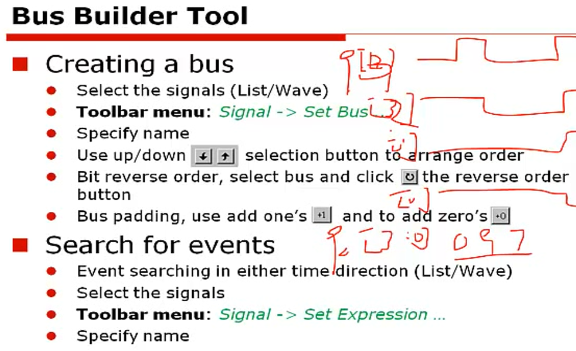

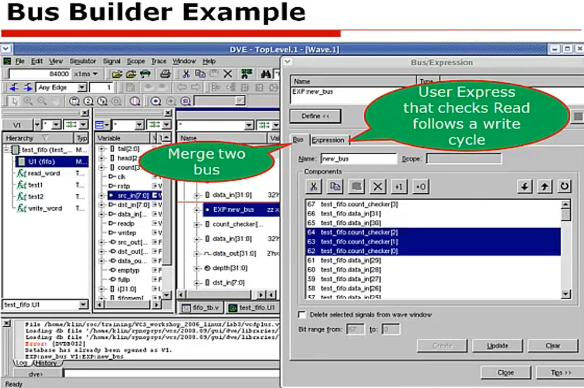

7. 建立BUS

PPT1

PPT2

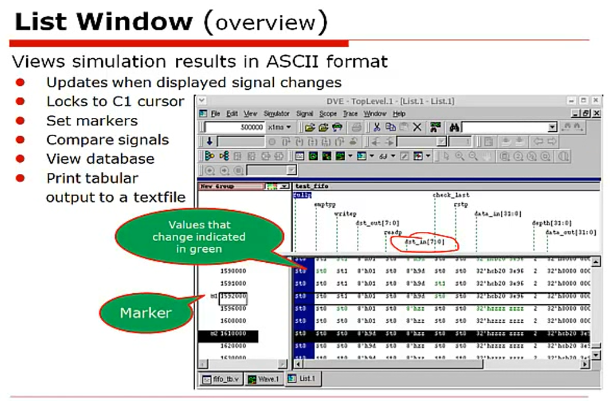

8. List Windows&Other

PPT1

PPT2

最后把Memory的波形也dump

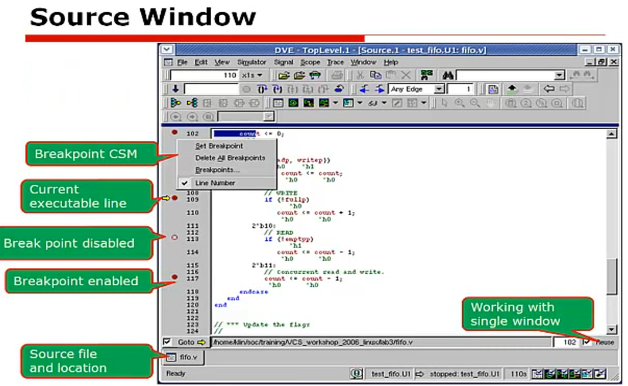

PPT3

源代码中插入断点

PPT4

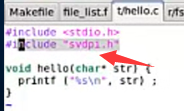

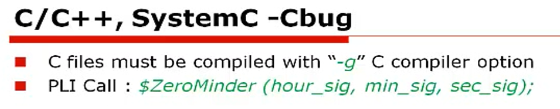

验证过程用到C语言的模型

PPT5

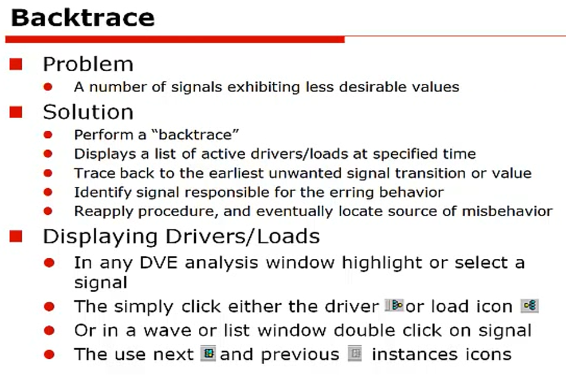

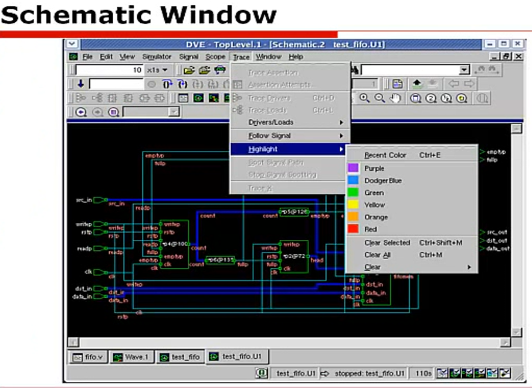

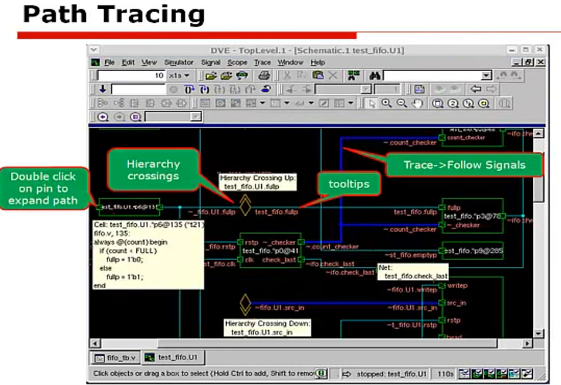

9.电路原理图

PPT1

PPT2

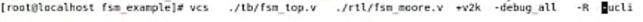

10 实验部分

执行后run一下

启动对应的进程号

点一个module显示所有的端口,task是没有信号的,funtion他们是动态的,所以task function需要monitor

add to wave form

- 拖动信号

- 按照鼠标中键,新增加标轴

- 波形放大缩小

- 区域性放大

- 设置信号的进制

- 波形里面以状态的形式(state name)

信号的分组和命名

查找7有没有出现

两个信号的比较,产生了一个新的信号

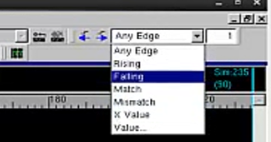

单步调试

进入到task funtion

构造一条BUS

crtl+选择信号,给总线命名

verilog调用C语言写的