1 SDRAM控制原理

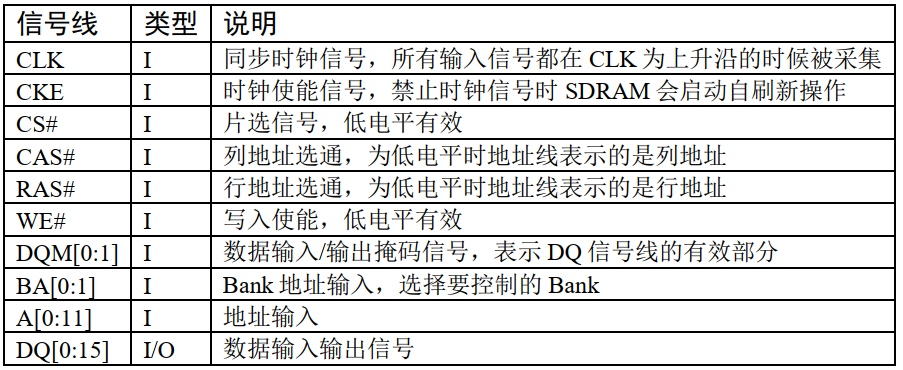

1.1 SDRAM信号线

1.2 SDRAM地址线

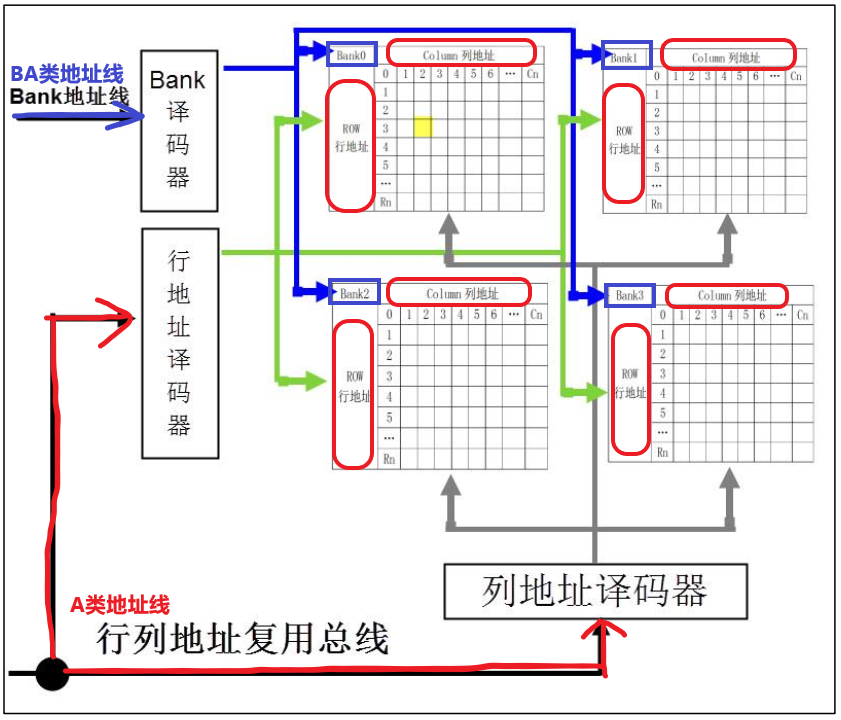

SDRAM包含有“A”以及“BA”两类地址线:

A:行(Row)与列(Column)共用的地址线

BA:独立的用于指定SDRAM芯片内部存储阵列号(Bank)

通讯时,当RAS=0,则“行地址选通器”被选通,地址线A[11:0]表示的地址会被输入到“行地址译码器”中,行地址被选中;同时地址线BA[1:0]表示的Bank也被锁存,选中要操作的Bank号;接着CAS=0,则“列地址选通器”被选通,地址线A[11:0]表示的地址会被输入到“列地址译码及锁存器”中作为列地址,完成寻址过程。

1.3 SDRAM数据线

IS45s16400J存储阵列的“数据宽度”是16位,但在实际应用中也可能会以8位宽度存取数据,这时我们只需要DQ[7:0]表示数据,而DQ[15:8]数据线表示的数据必须忽略。所以数据输入输出时,还会使用DQM[1:0]来配合,每根DQM线对应8位数据。如DQM0=0,DQM1=1时,数据线DQ[7:0]表示数据有效,而DQ[15:8]表示数据无效。

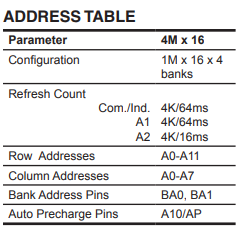

1.4 SDRAM容量计算

已知IS45s16400J芯片行地址12根线,列地址8根,4个Bank,位宽16bit。

可以计算出:

SDRAM的总单元数 =(2^行地址选择线)*(2^列地址选择线)*Bank选择线=2^(12+8)*4=2^10*4=1M bits*4

SDRAM总容量 = 单元数*位宽=1M bits*4*16=64M bits = 8MB(Bytes)

2 FMC

2.1 通信引脚

| SDRAM引脚 | FMC引脚 | 说明 |

| CLK | FMC_SDCLK | 同步时钟信号 |

| CKE | FMC_SDCKE1 | 时钟使能信号 |

| CS | FMC_SDNE1 | 片选信号 |

| CAS | FMC_NCAS | 列地址选通 |

| RAS | FMC_NRAS | 行地址选通 |

| WE | FMC_SDNWE | 写使能 |

| DQM[0:1] | FMC_NBL[0:1] | 数据输入/输出掩码信号 |

| BA[0:1] | FMC_A[14:15] | SDRAM芯片内部Bank地址输入 |

| A[0:11] | FMC_A[0:11] | 地址输入 |

| DQ[0:15] | FMC_D[0:15] | 数据输入/输出 |

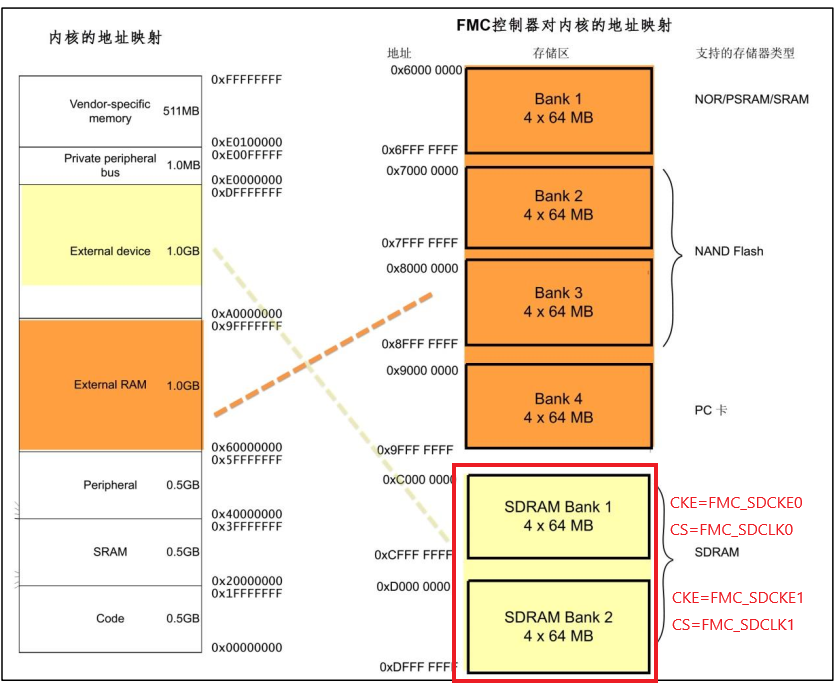

CKE和CS作用:

FMC_SDCKE0,FMC_SDCLK0:FMC映射的SDRAM的存储区域Bank1

FMC_SDCKE1,FMC_SDCLK1:FMC映射的SDRAM的存储区域Bank2

2.2 地址映射

FMC_SDCKE0,FMC_SDCLK0:FMC映射的SDRAM的存储区域Bank1(0xC000 0000~0xCFFF FFFF)

FMC_SDCKE1,FMC_SDCLK1:FMC映射的SDRAM的存储区域Bank2(0xD000 0000~0xDFFF FFFF)

注意:这里的Bank和上面所讲的SDRAM芯片内部存储区域Bank1~4是不一样的概念。