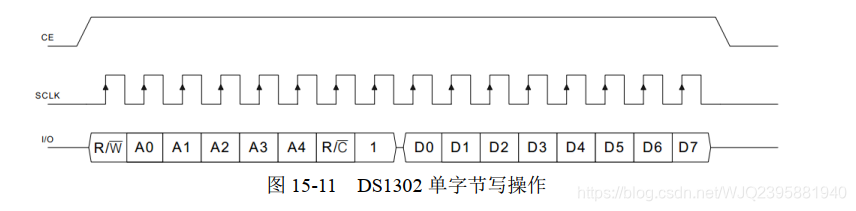

CE 和 SSEL 的使能控制是反的,对于通信写数据,

都是在 SCK 的上升沿,从机进行采样,下降沿的时候,主机发送数据。 DS1302 的时序里,

单片机要预先写一个字节指令,指明要写入的寄存器的地址以及后续的操作是写操作,然后

再写入一个字节的数据。

读操作有两处需要特别注意的地方。第一, DS1302 的时序图上的箭头都是针对 DS1302

来说的,因此读操作的时候,先写第一个字节指令,上升沿的时候 DS1302 来锁存数据,下

降沿我们用单片机发送数据。到了第二个字数据,由于我们这个时序过程相当于

CPOL=0/CPHA=0,前沿发送数据,后沿读取数据,第二个字节是 DS1302 下降沿输出数据,

我们的单片机上升沿来读取,因此箭头从 DS1302 角度来说,出现在了下降沿。

第二个需要注意的地方就是,我们的单片机没有标准的 SPI 接口,和 I2C 一样需要用 IO

口来模拟通信过程。在读 DS1302 的时候,理论上 SPI 是上升沿读取,但是程序是用 IO 口模

拟的,所以数据的读取和时钟沿的变化不可能同时了,必然就有一个先后顺序。通过实验发

现,如果先读取 IO 线上的数据,再拉高 SCLK 产生上升沿,那么读到的数据一定是正确的,

而颠倒顺序后数据就有可能出错。这个问题产生的原因还是在于 DS1302 的通信协议与标准

SPI 协议存在的差异造成的,如果是标准 SPI 的数据线,数据会一直保持到下一个周期的下

降沿才会变化,所以读取数据和上升沿的先后顺序就无所谓了;但 DS1302 的 IO 线会在时钟

上升沿后被 DS1302 释放,也就是撤销强推挽输出变为弱下拉状态,而此时在 51 单片机引脚

内部上拉的作用下, IO 线上的实际电平会慢慢上升,从而导致在上升沿产生后再读取 IO 数

据的话就可能会出错。因此这里的程序我们按照先读取 IO 数据,再拉高 SCLK 产生上升沿

的顺序。

DS1302时钟芯片时序

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

猜你喜欢

转载自blog.csdn.net/WJQ2395881940/article/details/102719294

今日推荐

周排行