1.IO端口定义

1.1 I/O端口

端口(Port)是接口电路中能被CPU直接访问的寄存器。CPU通过这些地址即端口向接口电路中的寄存器发送命令,读取状态和传送数据,因此,一个接口可以有几个端口,如状态口、数据口和命令口,分别对应于状态寄存器、数据寄存器和命令寄存器。

● 状态端口

状态端口(State Port)主要用来指示外部设备的当前状态。每种状态用一个二进制位表示,每个外部设备可以有几个状态位,它们可被CPU读取,以测试或检查外部设备的状态,决定程序的流程。一般接口电路中常见的状态位有准备就绪位(Ready)、外部设备忙位(Busy)、错误位(Error)等。

● 数据端口

数据端口(Data Port)用以存放外部设备送往CPU的数据以及CPU输出到外部设备去的数据。这些数据是主机和外部设备之间交换的最基本信息,长度一般为1-4字节。数据端口主要起数据缓冲作用。

● 命令端口

命令端口(Command Port)也称控制端口(Control Port),用来存放CPU向接口发出的各种命令和控制字,以便控制接口或设备的动作。接口功能不同,接口芯片的结构也就不同,控制字的格式和内容自然各不相同。一般可编程接口芯片往往具有工作方式命令字、操作命令字等。

1.2 I/O操作

通常所说的I/O操作是指对I/0端口的操作,而不是对I/O设备的操作,即CPU所访问的是与I/O设备相关的端口,而不是I/O设备本身。而I/O操作也就是CPU对端口寄存器的读写操作。CPU对数据端口进行一次读或写操作也就是与该接口连接的外部设备进行一次数据传送;CPU对状态端口进行一次读操作,就可以获得外部设备或接口自身的状态代码;CPU把若干位控制代码写入控制端口,则意味着对该接口或外部设备发出一个控制命令,要求该接口或外部设备按规定的要求工作。

2.编址方式

I/O端口的编址方式主要有两种:内存与I/O端口统一编址和I/O端口单独编址。

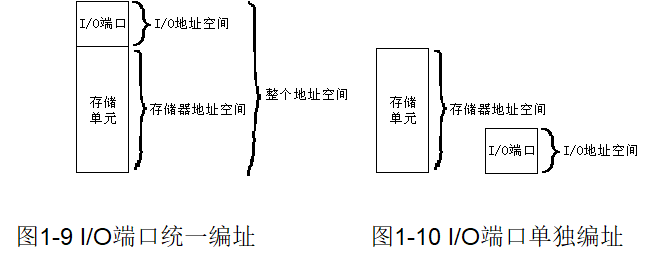

(1)统一编址

统一编址是指在整个存储空间中划分出一部分地址空间给外设端口使用,即把每一个I/O端口看作一个存储单元,与存储单元一样编址,访问存储器的所有指令均可用来访问I/O端口,不用设置专门的I/O指令,所以称为存储器映射I/O编址方式,地址空间分布情况如图1-9所示 。 摩托罗拉公司的MC6800及68HC05等处理器就采用了这种方式访问I/O设备。

这种方式的优点:在于I/O端口的地址空间较大,对端口进行操作的指令功能较强,使用时灵活方便。

这种方式的缺点是端口占用了存储器的地址空间,使存储器容量减小,另外指令长度比专门I/O指令要长,因而执行速度较慢。

(2)独立编址

独立编址是指对系统中的I/O端口单独编址,与内存单元的地址空间相互分开,各自独立,采用专门的I/O指令来访问具有独立空间的I/O端口,地址空间分布情况如图1-10所示 。8086/8088系统中就采用这种编址方式。

优点:不占用内存单元的有效地址空间,地址译码器较简单,端口操作指令长度较短,执行速度较快。

以上这两种I/O编址方式各有利弊,不同类型的CPU可根据外部设备特点采用不同的编制方式。

3. I/O端口地址分配与地址译码技术

项目名:

设计一个有6组I/O端口地址的译码电路

项目要求与目的:

(1)项目要求:通过项目了解74LS138译码器进行地址译码的方法和工作原理。

(2)项目目的:

●了解74LS138译码器的真值表。

●了解用译码器设计I/O端口地址的方法。

项目说明:

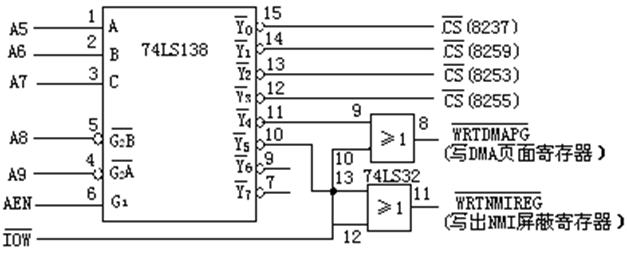

74LS138译码器有8个输出,本项目只用其中6个。而地址线的高5位A5~A9经过74LS138译码器,分别产生DMA控制器8237A、中断控制器8259A、定时/计数器8254、并行接口8255A等接口芯片的片选信号,而地址线的低5位A0~A4作为接口芯片内部寄存器的访问地址。由74LS138译码器真值表可知,当地址为000~01XH时,使输出为低,选中8237A,由于低位地址线A0~A3已接8237A,故8237A的端口地址为000H~01FH。其他端口与此同理,如8259A的片选地址是02X~03XH,端口地址为020~03FH。

项目电路图:

一个有6组I/O端口地址的译码电路如图1-9所示。电路由地址总线、控制总线、74LS138译码器和门电路等组成。

![]()

3.1 地址分配

I/O端口地址分配

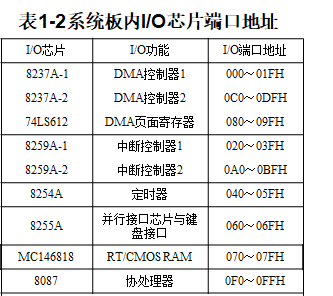

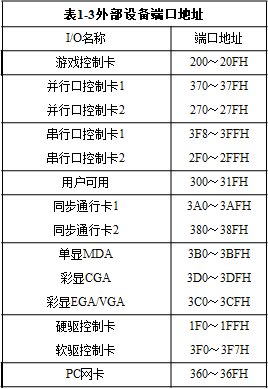

不同类型的微机系统采用不同的I/O地址编排方式,I/O地址空间的划分也各不相同。对80x86而言,采用独立编排方式,I/O端口地址的16位,最大寻址范围为64K个地址。但是,在IBM-PC机及其兼容机的设计中,主板上只用了10位I/O端口地址线,因此支持的I/O端口数位1024个,地址空间为0000H~03FFH,并且把前512个端口分配给了主板,后512个端口分配给了扩展槽上的常规外设。后来在PC/AT系统中,作了一些调整,其中前256个端口(000~0FFH)供系统板上的I/O接口芯片使用,如表1-2所示。后768(100~3FFH)供扩展槽上的I/O接口控制卡使用,如表1-2所示。按照I/O设备的配置情况,I/O接口的硬件分为如下两类。

(1) 系统板上的I/O接口

系统板上的I/O接口也称为板内接口,寻址到的都是可编程大规模集成电路,完成相应的板内接口操作。如定时/计数器、中断控制器、DMA控制器、并行接口等。随着大规模集成电路的发展,所以I/O接口芯片或控制器都已经集成在一片或几片大规模集成电路芯片中,形成了主板芯片组,并命名为南/北桥、MCH/ICH等。表1-2所示的各种接口芯片,虽然在主板上不能看见,但是仍然完整地存在于主板芯片组中(一般都在南桥中),其板内地址也保持不变。

(2)扩展卡上的I/O接口

扩展卡主要是指插接在主板插槽上的接口卡,通过系统总线与CPU系统相连。这些扩展卡一般由若干个集成电路按一定得逻辑组成一个部件,如软驱卡、硬驱卡、图形卡、声卡、打印卡、串行通信卡等,如表1-3所示。

3.2 译码

I/O端口地址译码

微机系统中有多个接口存在,接口内部往往包含多个端口,CPU是通过地址对不同的端口加以区分的。把CPU送出的地址转变为芯片选择和端口区分依据的就是地址译码电路。每当CPU执行输入输出指令时,就进入I/O端口读写周期,此时首先是端口地址有效,然后是I/O读写控制信号TOR或有效,这样就可以很好的把端口地址译码产生的译码信号同或结合起来,一同控制对I/O端口读或者写。接口地址译码方法很多,下面主要介绍两种。

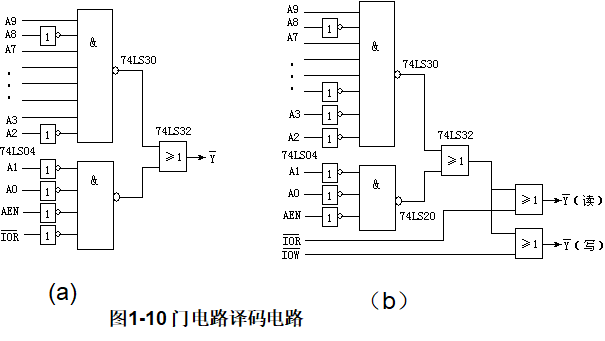

(1)用门电路进行I/O端口地址译码

门电路译码就是采用与门、与非门、反相器及或非门等简单逻辑门器件,如74LS20、74LS30、74LS32、74LS08、74LS04等,构成译码电路。这是一种最基本的I/O端口地址译码方法,下面通过举例来说明设计方法。

【例1-5】 使用74LS20/30/32和74LS04设计I/O端口地址为2F8H的只读译码电路。

分析:若要产生2F8H端口地址,则译码电路的输入地址就应具有如表1-4所示的值。

设计:按照表1-4中地址表的值,采用门电路就可以设计出译码电路,如图1-10(a)所示。

图1-10(a)中AEN信号必须参加译码,因为AEN为高电平时,I/O处于DMA方式,或信号由DMA控制器发出;AEN为低电平时,I/O处于正常方式,或信号由CPU发出。因为该接口电路中I/O处于正常方式,AEN必须为低电平,故用AEN信号参加译码来区分这两种方式。

同理可设计出能执行读/写操作的2E2H端口地址的译码电路,如图1-10(b)所示。

(2)译码器进行I/O端口地址译码

若接口电路中需要使用多个端口地址,则可采用译码器来进行译码。译码器的型号有很多,常用的译码器有3-8译码器74LS138;4-16译码器74LS154;双2-4译码器74LS139、74LS155等。下面通过举例来说明设计方法。

【例1-6】 使用74LS138设计一个系统板是上接口芯片的I/O端口地址译码电路,并且让每个接口芯片内部的端口数目为32个。

分析:由于系统板上的I/O端口地址分配在000~0FFH范围内,故只使用低8位地址线,这意味着A9和A8两位应赋0值。为了让每个被选中的芯片内部拥有32个端口,只要留出5根低地址线不参加译码,其余的高位地址线作为74LS138的输入线,参加译码,或作为74LS138的控制线与AEN一起,控制74LS138的译码是否有效。由上述分析,可以得到译码电路输入地址线的值,如表1-5所示。

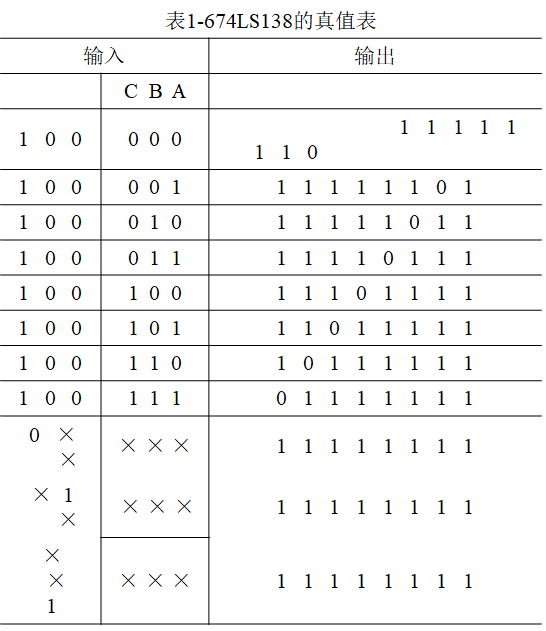

对于译码器74LS138的分析有两点:一是它的控制信号线G1、和。只有当满足控制信号线G1为高电平, ==0时,74LS138才能进行译码。二是译码的逻辑关系,即输入(C,B,A)与输入(Y0~Y7)的对应关系。74LS138输入/输出的逻辑关系,如表1-6所示。

从表1-6可知,若满足控制条件,即G1为高电平, ==0,则由输入端C、B、A的编码来决定输出:CBA=000,则为低电平,其他输出端为高电平;CBA=001,为低电平,其他输出端为高电平;…;CBA=111,为低电平,其他输出端为高电平。由此可分别产生8个译码输出信号(低电平)。若控制条件不满足,则输出全“1”,不产生译码输出信号,即译码无效。