scan的过程解说

scan分为stuck-at和at-speed两种测试模式,

| item | clk | 说明 | 对应的DC/AC |

|---|---|---|---|

| stuck-at | 测试机提供时钟 时钟慢 | 静态测试 | DC mode |

| at-speed | function clk | 测试芯片中的延迟故障,也就是transition | AC mode |

DC和AC模式下它们的shift是一样的,在launch和capture过程的时钟策略是不一样的

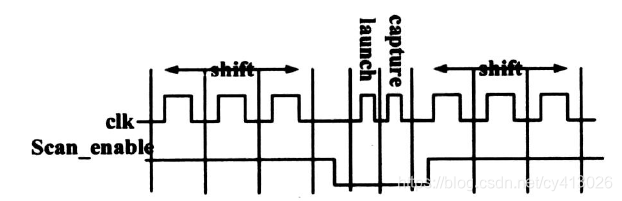

下面以At-speed来讲解scan过程

At-speed测试

at - speed测试生成的测试向量分为两部分。第一部分是在一个组合逻辑的输入端发射( launch)一个 0 - 1或1 - 0的翻转,第二个部分要捕获( capture)组合逻辑的输出端响应。如果在指定的时间周期内capture的响应正确,那么说明电路没有at-speed故障。

launch和capture的概念

launch和capture一定是对两个寄存器而言的,当前寄存器reg_cur,前一级寄存器reg_bf。对于reg_cur它的launch就是reg_bf的capture,这个概念在scan和sta中都是一样的。

以同步电路为例

reg_bf 在@posedge clk_0 时刻D端capture bit ‘1’ 那么同一时钟沿经过Tco之后launch bit ‘1’,next clk posedge reg_cur capture bit ‘1’

launch-off-shift & launch-from-capture

参考文献Launch-off-shift at-speed test

- (a). launch-off-shift

Lunch off shift (LOS):

- (b). launch-from-capture

又被称为broadside pattern或Lunch off capture (LOC)

- ©.两者的区别

LOS和LOC的区别在launch的过程中scan_en的值不同,LOC在launch时scan_en=0,而LOS在launch时scan_en=1。

对capture的影响在于LOC情况下前一级flip-flop launch值要经过combination logic,所以ATPG需要计算测试向量经过combination logic的值,才能与capture的值比对。

参考文献Launch-off-shift at-speed test详细给出两者的区别和使用情况

scan 过程

-

- scan shift

在shift阶段( scan_enable = 1)使用测试机提供的慢速时钟,A和B分别装载0和1。这个过程就是测试机将测试向量‘01’shift到对应的flip-flop。

- scan shift

-

- launch

首先set scan_enable = 0,这时发一个功能时钟( launch时钟) , B会在D端捕获0,一个1 - to - 0的翻转会传递到C。(为了简单认为两寄存器之间没有zuheluoji)

- launch

-

-

capture

保持scan_enable = 0,在第二个功能时钟脉冲( cap ture时钟) C会捕获这个变化。如果在第二个时钟C捕获到了0,意味着在一个周期内完成了所需的翻转。

图2中Clk信号在shift和launch、cap tuer阶段的切换、以及launch、cap ture2个功能脉冲的产生需要有专门的电路支持。这就是下面要介绍的OCC电路。

-

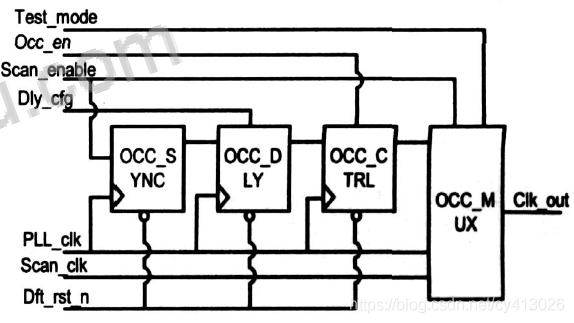

OCC电路

一般芯片内部都由CRG (Clock Reset Generation)模块来提供系统工作所需的各种时钟,然后提供给各个模块使用。为了支持at - speed测试,需要在CRG和模块之间加入OCC电路。OCC电路可以支持以下功能:

- 正常功能模式下输出系统时钟。

- stuck _ at测试模式下输出测试机慢速时钟scan_clk。

- at_speed测试模式下输出如图2的时钟。

OCC电路的模块结构示意图如图3所示。

下面分别介绍各个模块的作用。

OCC_SYNC对控制信号(通常为scan_enable)使用本地时钟进行同步处理,避免亚稳态。

OCC_DLY对控制信号进行延时,确保OCC在输出系统前,芯片处于稳定状态。一般OCC_DLY中使用计数器计算延时,计数器位宽由Dly_cfg[N:0 ]配置。此模块可以根据需要决定是否加入。

OCC_CTRL电路用来产生图2 中的at - speed测试时钟。电路如图4所示。

在2 pulse generation中前2个寄存器用来对控制信号做同步,后面的2个寄存器和与门产生2个周期长度的控制信号。然后和clock gating 中的PLL_CLK做一个gating,生成2个功能脉冲,第一个即launch 时钟, 第二个为cap ture 时钟。最后用scan_enable信号来实现图2中不同阶段的选择。Occ_en信号用来配置此OCC电路是否使能。

以上摘自(上海交通大学,上海200052)李 冬,任敏华《如何用OCC电路实现at - speed测试》,该文详细给出了scan at-speed mode的详细过程和OCC电路原理