目录

三、存储系统

容量从小到大: 寄存器 -> Cache -> 内存 -> 外存

Cache不是必需的,内存可以直接读取CPU但速度极慢,Cache一般是以K或M字节来存储,内存一般是以G字节来存储,Cache存储的是主存中极小部分的内容

1.Cache

Cache的功能:提高CPU数据输入输出的速率,突破冯·诺依曼瓶颈,即CPU与存储系统间数据传送宽带限制。

在计算机的存储系统体系中,Cache是访问速度最快的层次。

使用Cache改善系统性能的依据是程序的局部性原理。

由于在CPU与存储系统间存在着数据传送带宽的限制,因此在其中设置了Cache(高速缓冲存储器,通常速度比内存快),以提高整体效率。但由于其成本更高,因此Cache的容量要比内存小得多。Cache是一种相联存储器(即按内容进行存储的存储器)。

(1)Cache原理、命中率、失效率

使用Cache改善系统性能的主要依据是程序的局部性原理。通俗地说,就是一段时间内,执行的语句常集中于某个局部。而Cache正式将访问集中的内容放在速度更快的Cache上,以提高性能。引入Cache后,CPU在需要数据时,先找Cache,如果没有再找内存。如果Cache的访问命中率为h(通常1h就是Cache的失效率),而Cache的访问周期时间是

t 1,主存储器的访问周期时间是t 2,则整个系统的平均访存时间就应该是:

t3 = h*t1 + (1-h)*t2

从公式可以看出,系统的平均访存时间与命中率有着很密切的关系。灵活地应用这个公式,可以计算出所有情况下的平均访存时间。

例如:设某流水线计算机主存的读/ 写时间为100ns ,有一个指令和数据合一的Cache,已知该Cache的读/ 写时间为10ns ,取指令的命中率为98%,取数的命中率为95%。在执行某类程序时,约有1/ 5指令需要存/ 取一个操作数。假设指令流水线在任何时候都不阻塞,则设置Cache后,每条指令的平均访存时间约为多少?其实这是应用该公式的简单数学题:

( 2%×100ns+ 98%×10ns ) + 1/ 5×( 5%×100ns+ 95%×10ns ) =14. 7ns

(2)Cache存储器的映射机制

CPU发生访存请求时,会先让Cache判断是否包括,如果命中(即包括请求的内容)就直接使用。这个判断的过程就是Cache地址映射,这个速度应该尽可能快,常见的映射方法有直接映射、全相联映射和组相联映射三种。

直接映射:是一种多对一的映射关系,但一个主存块只能够复制到Cache的一个特定位置上

去。Cache的行号i 和主存的块号j 有函数关系:i =j %m(其中m为Cache总行数)。例如:某Cache容量为16KB(可用14位表示),每行的大小为16B(可用4位表示),则说明其可分为1024行(可用10位表示)。则主存地址的最低四位为Cache的行内地址,中间10位为Cache行号。如果内存地址为1234E8F8H的话,那么最后四位就是1000(对应16进制数的最后一位),而中间10位,则应从E8F(111010001111)中获取,得到1010001111。

相联映射:将主存中一个块的地址与块的内容一起存于Cache的行中。速度更快,但控制复

杂。

组相联映射:是前两种方式的折中方案。它将Cache中的块再分成组。然后通过直接映射方式决定组号,再通过相联映射的方式决定Cache中的块号。

要注意的是,在Cache映射中,主存和Cache存储器将均分成容量相同的块。

例如:容量为64块的Cache采用组相联方式映像,字块大小为128个字,每4块为一组。若主存容量为4096块,且以字编址,那么主存地址应该为多少位?主存区号为多少位?这样的题目,首先根据主存与Cache块的容量需一致,因此内存也是128个字,因此共有128×4096个字,即2^19( 2^7*2^12) 个字,因此主存地址需要19位;而内存所需要分为4096/ 64块,即2^6,因此主存区号需要6位.

(3)Cache淘汰算法

当Cache数据已满,并且出现未命中情况时,就是淘汰一些老的数据,更新一些新的数据。而选择淘汰什么数据的方法就是淘汰算法,常见的方法有三种:随机淘汰、先进先出(FI FO)淘汰(淘汰最早调入Cache的数据)、最近最少使用(LRU)淘法。其中平均命中率最高的是LRU算法。

(4)Cache存储器的写操作

在使用Cache时,需要保证其数据与主存一致,因此在写Cache时就需要考虑与主存间的同步问题,通常使用以下三种方法:写直达(写Cache时,同时写主存)、写回(写Cache时不马上写主存,而是等其淘汰时回写)、标记法。

Cache与主存的地址映像需要专门的硬件自动完成,使用硬件来处理具有更高的转换速率。

相联存储器一种按内容进行存储和访问的存储器。

2. 主存(内存)

(1)主存储器的种类

RAM:随机存储器,可读写,断电后数据无法保存,只能暂存数据。

SRAM:静态随机存储器,在不断电时信息能够一直保持。

DRAM:动态随机存储器,需要定时刷新以维持信息不丢失。

ROM:只读存储器,出厂前用掩膜技术写入,常用于存放BI OS和微程序控制。

PROM:可编程ROM,只能够一次写入,需用特殊电子设备进行写入。

EPROM:可擦除的PROM,用紫外线照射15~20分钟可擦去所有信息,可写入多次。

E 2PROM:电可擦除ERPOM,可以写入,但速度慢。

闪速存储器:现在U盘使用的种类,可以快速写入。

记忆时,抓住几个关键英文字母。A,即Acces s ,说明读写都行;O,即Onl y,说明只读;P,即Programmable,说明可通过特殊电子设备写入;E,即Erasabl e,说明可擦写;E平方说明是两个E,第二个E是电子。

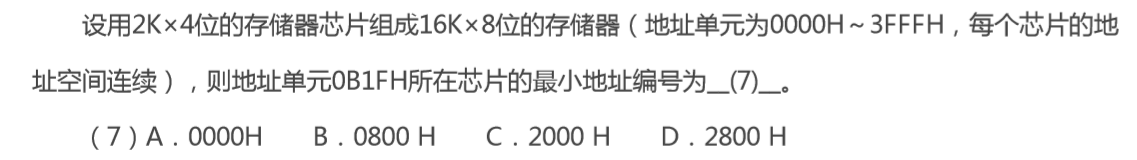

主存的编址:把芯片组成相应的存储器

(2)主存储器的组成

实际的存储器总是由一片或多片存储器配以控制电路构成的。其容量为W×B,W是存储单元(word,即字)的数量,B表示每个word由多少bit(位)组成。如果某一芯片规格为w×b,则组成W×B的存储器需要用(W/ w)×(B/ b)个芯片。

(3)主存储器的地址编码

主存储器(内存)采用的是随机存取方式,需对每个数据块进行编码,而在主存储器中数据块是以word来标识的,即每个字一个地址,通常采用的是16进制表示。例如,按字节编址,地址从A4000H到CBFFFH,则表示有( CBFFFA4000) +1个字节,28000H个,也就是163840个字节,等于160KB。

要注意的是,编址的基础可以是字节,也可以是字(字是由1个或多个字节组成的),要算地址位数,首先应计算要编址的字或字节数,然后求2的对数即可得到。

I / O接口与主存采用统一编址,即将I / O设备的接口与主存单元一样看待,每个端口占用一个存储单元的地址,其实就是将主存的一部分划出来作为I / O地址空间。

访存指令是指访问内存的指令,显然,这里需要访问内存,才能找到相应的输入输出设备,一次需要使用访存指令。

而控制类指令通常是指程序控制类指令,用于控制程序流程改变的指令,包括条件转移指令、无条件转移指令、循环控制指令、程序调用和返回指令、中断指令等。

按寻址方式划分,存储器可分为:顺序存储(如:磁带机),直接存储器(如:磁盘、硬盘、光盘),随机存储器(如:内存、U盘)。

等待时间也称“旋转延迟时间”

总线:根据总线所处的位置不同,总线通常被分成三种类型,分别是:

内部总线

内部总线是一种内部结构,是cpu、内存、输入、输出设备传递信息的公用通道,芯片级

系统总线:数据总线、地址总线、控制总线

系统总线结合数据总线的功能来搭载信息,地址总线来决定将信息送往何处,控制总线来决定如何动作,是连接计算机系统的主要组件。

外部总线

通常所说的总线(Bus)指片外总线,是CPU与内存RAM、ROM和输入/输出设备接口之间进行通讯的通路,也称系统总线。

三、可靠性计算

可靠性计算在软件设计师考试中出现频度较高,出题方式也较为单一,主要是计算;,另外一个知识点是校验码,出现频度较低,需要了解概念及计算过程。

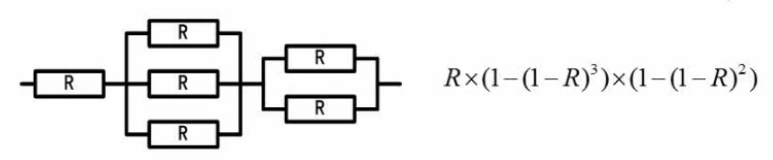

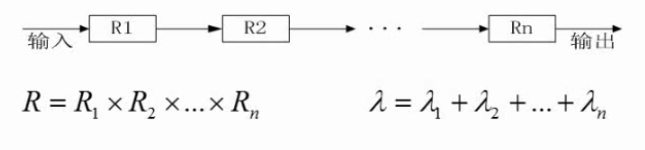

可靠性计算主要涉及三种系统,即串联系统、并联系统和冗余系统,其中串联系统和并联系统的可靠性计算都非常简单,只要了解其概念,公式很容易记住。冗余系统要复杂一些,有些学员常常搞不清楚。

(1)串联系统

假设一个系统由n个子系统组成,当且仅当所有的子系统都能正常工作时,系统才能正常工作,这种系统称为串联系统

可靠性 R=1-(1-R1)*(1-R2)*…*(1-Rn)

失效率 u=1-R

在并联系统中只有一个子系统是真正需要的,其余n1个子系统都被称为冗余子系统。该系统随着冗余子系统数量的增加,其平均无故障时间也会增加。

(2)模冗余系统

m模冗余系统由m个(m=2n+1为奇数)相同的子系统和一个表决器组成,经过表决器表决后,m个子系统中占多数相同结果的输出可作为系统的输出。

在m个子系统中,只有n+1个或n+1个以上的子系统能正常工作,系统就能正常工作并输出正确 结果。假设表决器是完全可靠的,每个子系统的可靠性为R0,则m模冗余系统的可靠性为: