版权声明:关注微信公众号:嵌入式Linux QQ群:69759006 了解更多嵌入式方面知识 https://blog.csdn.net/weiqifa0/article/details/87854888

1、obj-$

$(CONFIG_TEST) 是一个整体,$(bbb)表示引用变量 bbb

比如定义 CONFIG_TEST=y

$(CONFIG_TEST) 就是 y

obj-$(CONFIG_TEST) 就是 obj-y

又比如定义 CONFIG_TEST=m

$(CONFIG_TEST) 就是 m

obj-$(CONFIG_TEST) 就是 obj-m

obj-y += foo.o 该例子告诉Kbuild在这目录里,有一个名为foo.o的目标文件。foo.o将从foo.c 或foo.S文件编译得到。

例子:

obj-$(CONFIG_FOO) += foo.o $(CONFIG_FOO)可以为y(编译进内核) 或m(编译成模块)。如果CONFIG_FOO不是y 和m,那么该文件就不会被编译联接了

除了y、m以外的obj-x 形式的目标都不会被编译。

除了obj-形式的目标以外,还有lib-y library 库、hostprogs-y 主机程序等。

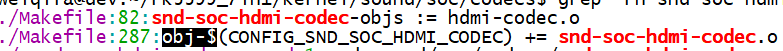

2、objs用法

obj-y = main.o

main-objs := a.o \ b.o \ c.o

将a.c b.c c.c三个文件编译后链接生成main.o