转载自:http://www.cnblogs.com/javado/p/7704579.html

这几天写了一段测试代码,跑在LPC812上面。

很吃惊的发现CPU速度为1M 时钟 串口为12M时钟 原来常测试的是STM32的 一般72M 分了再分。。。。

搞了半夜才弄明白,写在此处备忘。

LPC812

PLL输出为MAINCLK

MAINCLK分频得到 CPU 内存等用的时钟

MAINCLK分频得到 USART等外设用的时钟

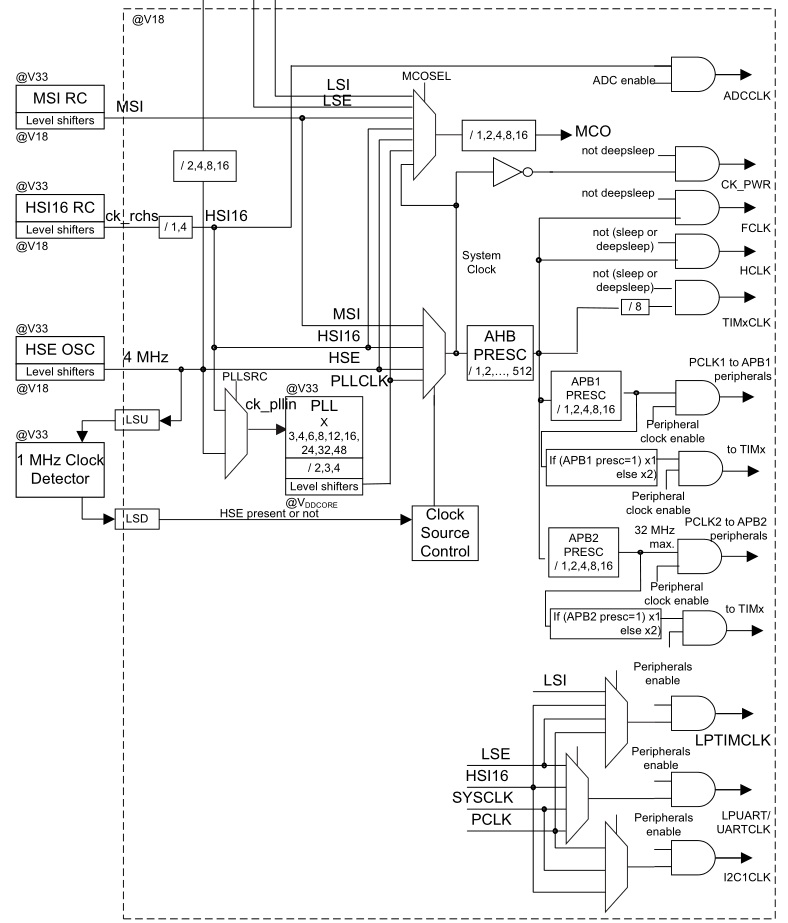

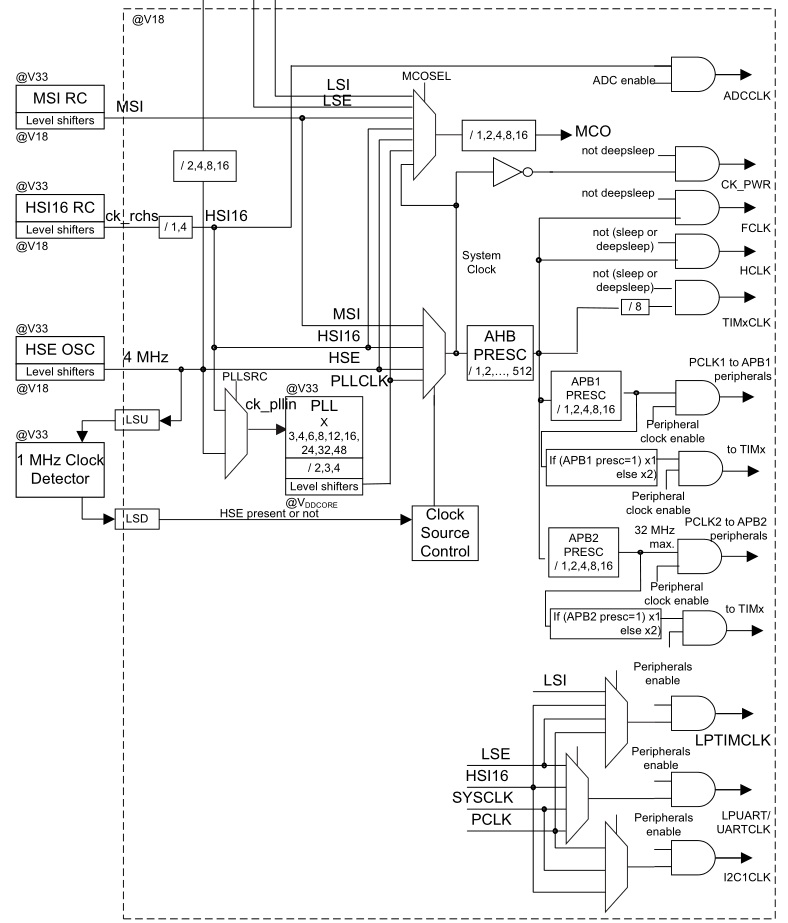

STM32

PLL输出为SYSCLK SYSCLK分频得到AHB时钟

AHB时钟不分频 直接供CPU 文档中叫FCLK

AHB时钟不分频直接供内存 FLASH等 文档中叫HCLK

AHB可APB1分频供APB1外设 文档中是PCLK1

AHB可APB2分频供APB2外设 文档中是PCLK2

附图

同时回忆一下STM32。。手头上随便找了STM32L051的手册吧。看了下,STM32比LPC812少了个CPU时钟的分频器。所以CPU时钟就是系统时钟。 外设必然低于CPU速度。

最后说一下SYSTICK 该时钟分频与否的时钟基准是CPU的时钟。虽然叫法不一样。但这个都是CPU的实际时钟为基准。

再在网上摘一段STM32的说明,以作备忘。

系统时钟SYSCLK最大频率为72MHz,它是供STM32中绝大部分部件工作的时钟源。系统时钟可由PLL、HSI或者HSE提供输出,并且它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、分频后送给STM32芯片的系统定时器时钟(Systick=Sysclk/8=9Mhz)

③、直接送给Cortex的自由运行时钟(free running clock)FCLK。【ARMJISHU注:FCLK 为处理器的自由振荡的处理器时钟,用来采样中断和为调试模块计时。在处理器休眠时,通过FCLK 保证可以采样到中断和跟踪休眠事件。 Cortex-M3内核的“自由运行时钟(free running clock)”FCLK。“自由”表现在它不来自系统时钟HCLK,因此在系统时钟停止时FCLK 也继续运行。FCLK和HCLK 互相同步。FCLK 是一个自由振荡的HCLK。FCLK 和HCLK 应该互相平衡,保证进入Cortex-M3 时的延迟相同。】④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用。

⑤、送给APB2分频器。APB2分频器可选择1、2、4、8、16分频, 其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出 供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

以上提到3种时钟Fclk、Hclk和Pclk,简单解释如下:Fclk为供给CPU内核的时钟信号,我们所说的cpu主频为XXXXMHz,就是指的这个时钟信号,相应的,1/Fclk即为cpu时钟周期;Hclk为优秀的高性能总线(AHB bus peripherals)供给时钟信号(AHB为advanced high-performance bus);HCLK :AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟,HCLK是高速外设时钟,是给外部设备的,比如内存,flash。Pclk为优秀的高性能外设总线(APB bus peripherals)供给时钟信号(其中APB为advanced peripherals bus)。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。当需要使用某模块时,记得一定要先使能对应的时钟。

这几天写了一段测试代码,跑在LPC812上面。

很吃惊的发现CPU速度为1M 时钟 串口为12M时钟 原来常测试的是STM32的 一般72M 分了再分。。。。

搞了半夜才弄明白,写在此处备忘。

LPC812

PLL输出为MAINCLK

MAINCLK分频得到 CPU 内存等用的时钟

MAINCLK分频得到 USART等外设用的时钟

STM32

PLL输出为SYSCLK SYSCLK分频得到AHB时钟

AHB时钟不分频 直接供CPU 文档中叫FCLK

AHB时钟不分频直接供内存 FLASH等 文档中叫HCLK

AHB可APB1分频供APB1外设 文档中是PCLK1

AHB可APB2分频供APB2外设 文档中是PCLK2

附图

同时回忆一下STM32。。手头上随便找了STM32L051的手册吧。看了下,STM32比LPC812少了个CPU时钟的分频器。所以CPU时钟就是系统时钟。 外设必然低于CPU速度。

最后说一下SYSTICK 该时钟分频与否的时钟基准是CPU的时钟。虽然叫法不一样。但这个都是CPU的实际时钟为基准。

再在网上摘一段STM32的说明,以作备忘。

系统时钟SYSCLK最大频率为72MHz,它是供STM32中绝大部分部件工作的时钟源。系统时钟可由PLL、HSI或者HSE提供输出,并且它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、分频后送给STM32芯片的系统定时器时钟(Systick=Sysclk/8=9Mhz)

③、直接送给Cortex的自由运行时钟(free running clock)FCLK。【ARMJISHU注:FCLK 为处理器的自由振荡的处理器时钟,用来采样中断和为调试模块计时。在处理器休眠时,通过FCLK 保证可以采样到中断和跟踪休眠事件。 Cortex-M3内核的“自由运行时钟(free running clock)”FCLK。“自由”表现在它不来自系统时钟HCLK,因此在系统时钟停止时FCLK 也继续运行。FCLK和HCLK 互相同步。FCLK 是一个自由振荡的HCLK。FCLK 和HCLK 应该互相平衡,保证进入Cortex-M3 时的延迟相同。】④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用。

⑤、送给APB2分频器。APB2分频器可选择1、2、4、8、16分频, 其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出 供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

以上提到3种时钟Fclk、Hclk和Pclk,简单解释如下:Fclk为供给CPU内核的时钟信号,我们所说的cpu主频为XXXXMHz,就是指的这个时钟信号,相应的,1/Fclk即为cpu时钟周期;Hclk为优秀的高性能总线(AHB bus peripherals)供给时钟信号(AHB为advanced high-performance bus);HCLK :AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟,HCLK是高速外设时钟,是给外部设备的,比如内存,flash。Pclk为优秀的高性能外设总线(APB bus peripherals)供给时钟信号(其中APB为advanced peripherals bus)。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。当需要使用某模块时,记得一定要先使能对应的时钟。