背景:已经输出IPcore为RTL,现在需要将相应的IPcore集成为系统并生成相应驱动。

目的:集成IPcore为系统,并生成驱动。

参考相关文档:

IPcore调用DDR https://blog.csdn.net/weixin_36474809/article/details/84942607

ARM调用DDR https://blog.csdn.net/weixin_36474809/article/details/80997945

FPGA vivado系统集成操作 https://blog.csdn.net/weixin_36474809/article/details/80690368

FPGA实践教程(三)系统搭建与烧录 https://blog.csdn.net/weixin_36474809/article/details/80840448

目录

一、系统集成范例

1.1 zynqNet的系统集成

p65系统集成

zynqNet的IPcore可能为了节省资源,并未采用Mig来控制DDR,而是通过PS与DDR相连。多生成了一个DRAM的驱动。相关方法我们编写SDK驱动时研究,为了节省硬件资源,我们暂时采用这种方法。

volatile data_t *XFPGA_shared_DRAM_virtual() {

printf("XFPGA Driver: SHARED_DRAM_virtual() = %X\n", (unsigned long)(SHARED_DRAM_virtual()));

return (volatile data_t*) (SHARED_DRAM_virtual());

}

volatile data_t *XFPGA_shared_DRAM_physical() {

printf("XFPGA Driver: SHARED_DRAM_physical() = %X\n", (unsigned long)(SHARED_DRAM_physical()));

return (volatile data_t*) (SHARED_DRAM_physical());

}1.2 之前调用DDR的流程

之前的流程都运用到了MIG内存控制器。我们可能要舍弃掉MIG,减少资源的占用。

IPcore调用DDR https://blog.csdn.net/weixin_36474809/article/details/84942607

ARM调用DDR https://blog.csdn.net/weixin_36474809/article/details/80997945

二、系统集成

流程及软件操作需要参考下面文档。

FPGA vivado系统集成操作 https://blog.csdn.net/weixin_36474809/article/details/80690368

FPGA实践教程(三)系统搭建与烧录 https://blog.csdn.net/weixin_36474809/article/details/80840448

FPGA实践教程(五)PS用MIG调用DDR https://blog.csdn.net/weixin_36474809/article/details/80997945

2.1 配置PS

PS的使用有必要使用给的例子,免得配置发生错误。

G:\Soft\Program\xilinx\Demo\MIZ7035\MIZ7035_FREE\CODE_FREE\S02

程序位置 G:\Soft\Program\xilinx\SDx

PS配置之后可以保存下来,以便以后反复调用使用。加入外设DDR,FIXED_IO

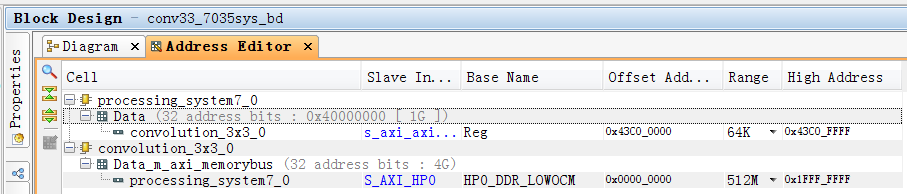

axi-master GP0,s_axi HP0

2.2 添加IP

2.3 连线

自动连接,PS的GP通过AXI interconnect接IPcore的s_axilite, IPcore通过axi-interconnect接PS的S_HP,

上面这张是虚拟机上的vivado中生成的,下面这张为window中vivado生成的。(这张生成的axilite加了register指令,并且没有return值,无法判断完成。)

重新加了return值,重新生成了IPcore,然后搭建的系统如下:

validate,create HDL wrapper,generate bitstream

可能的错因:

- 之前的axilite只生成了一个接口,而我们的程序生成了两个axi-lite的接口

- DRAM的指针值只有一个,我们有三个DRAM的指针值,并且depth调节可能有一定的问题。

三、集成后输出到SDK烧录

生成比特流成功后,file,export hardware include bitstream

用SDK打开vivado项目中的conv_Core_MTCNN\conv_sys\mtcnn_conv33_sys\mtcnn_conv33_sys.sdk

然后文件拖入BSP,右键wapper_platform_0,program FPGA,此时必须用JTAG连接。同时用安卓线microUSB连上serial看打印信息。

然后build project的文档。

launch,run