1、普通设置

在配置串口时,pinctrl的配置信息如下所示:

这里的MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA在imx6dl-pinfunc.h文件中有如下定义:

将管脚的配置展开即: 0x35c 0x744 0x000 0x2 0x00x1b0b1

想知道这六个值都是什么意思,可以从两个路出发:①查找解读dts的文件,即看内核源码;②在网上查找相关知识。

1.1 查看源码对设备树文件的解读

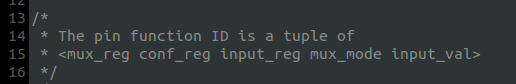

首先在imx6dl-pinfunc.h文件中有对前5个变量的解释,如下图:

为了验证这5个变量,并查找第6个变量的含义,我们打开读取设备树文件的代码。

读取dts文件的文件为:linux-3.18.22/drivers/pinctrl/freescale/pinctrl-imx.c,实现函数名为:static int imx_pinctrl_parse_groups(。。。),如下:

这段代码中list = of_get_property(np, "fsl,pins", &size);实现了读取dts文件中的fsl,pin属性值,并保存在了list指针变量中。紧接着,分别将list中的值mux_reg、conf_reg、input_reg、mux_mode、input_val、config六个变量中,由名字可以猜测个大概,前5个得以验证,第六个表示config,config的值说白了就是对寄存器配置(上拉电阻、频率等等)的值,就是pad_ctrl的值。

因此对应关系如下:

0x35c | 0x744 | 0x000 | 0x2 | 0x0 | 0x1b0b1

---------------------------------------------------------------------------------------------------------

mux_ctrl_ofs | pad_ctrl_ofs | sel_input_ofs | mux_mode | sel_input | pad_ctrl

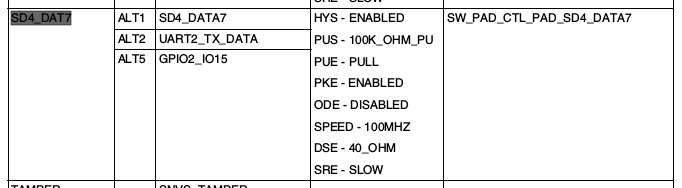

以上参数在参考手册怎么确定的呢?由于是对复用管脚的配置,于是在管脚复用的章节(IOMUXC)中查找。但是现确定pad name才方便,于是定义在External Signals and Pin Multiplexing章节,搜索MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA的中间部分:SD4_DAT7,如下图

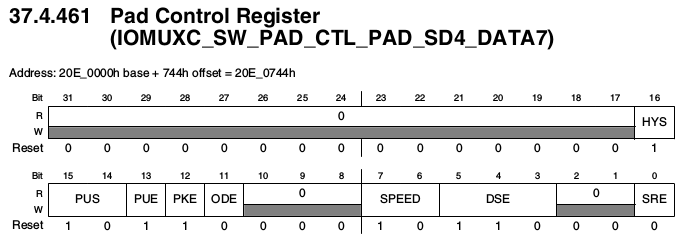

可知UART2_TX_DATA是属于SD4_DAT7的ALT2,于是mux_mode=0x2即可。上图表格中最后一列SW_PAD_CTL_PAD_SD4_DATA7是config配置需要查找的名称,跳到管脚复用的章节(IOMUXC)中,找到SW_PAD_CTL_PAD_SD4_DATA7,如下所示:

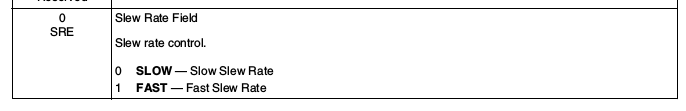

如果直接取默认值的话结果是config=0x1b0b0,这里可以根据自己的需要(硬件)更改为与自己的板子匹配的值,我把最后SRE的值设置为1,即Fast Slew Rate,如下图说明:

OK,接下来是mux_ctrl_ofs、pad_ctrl_ofs、sel_input_ofs三个偏移值,这些值都是在复用管脚的章节确定的。因为pad name为SD4_DATA7,所以在找的时候可以拿它当关键字。

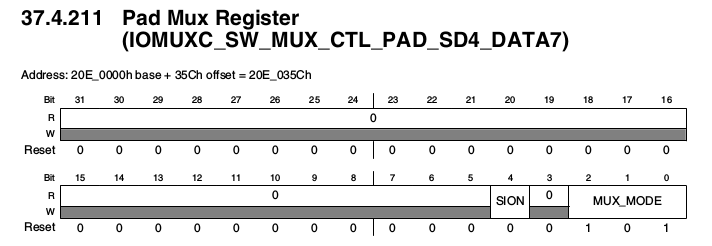

首先是mux_ctrl_ofs,找到IOMUXC_SW_MUX_CTL_PAD*开头的部分,结尾选择SD4_DATA7即可,如下图,

由”Address: 20E_0000h base + 35Ch offset = 20E_035Ch“中可知offset=35C,即mux_ctrl_oft=0x35c

其他的查找方法类似。pad_ctrl_ofs,查找IOMUXC_SW_PAD_CTL_PAD_SD4_DATA7一节,可知偏移值pad_ctrl_ofs=0x744

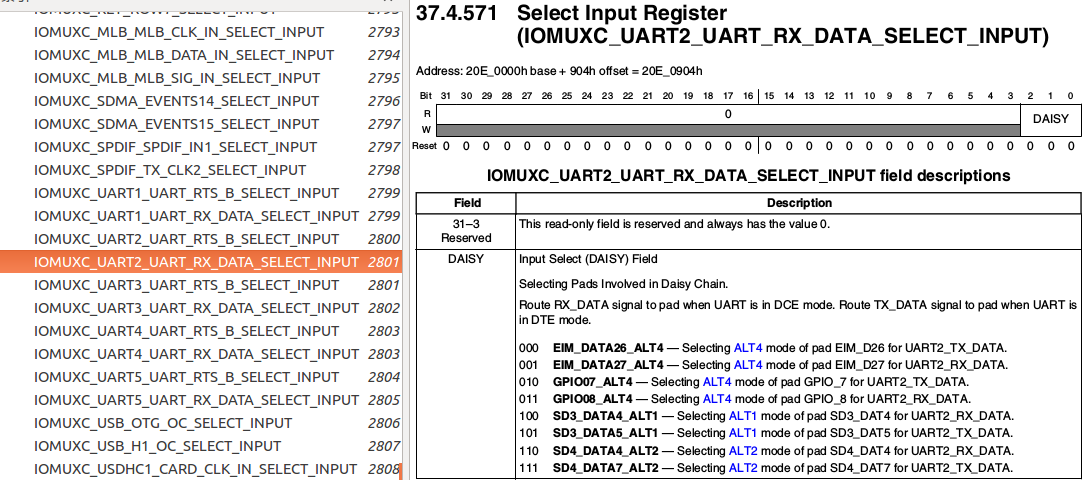

sel_input_ofs查找IOMUXC章节以SELECT_INPUT结尾的部分,中间选择UART2_TX,如果没有这里sel_input_ofs=0x000即可,对应的sel_input为0即可。如果有例如IOMUXC_UART2_UART_RX_DATA_SELECT_INPUT,即uart的rx管脚配置,如下图,所以RX的sel_input_ofs=0x904,这里选择对应的值“110 SD4_DATA4_ALT2 — Selecting ALT2 mode of pad SD4_DAT4 for UART2_RX_DATA..“所以RX(MX6QDL_PAD_SD4_DAT4__UART2_RX_DATA)的sel_input=0x6。

在Linux或Android系统中,假如我们要配置飞思卡尔IMX6处理器的GPIO管脚,比如是GPIO_19这个管脚,那么要像这样:

其中_MX6Q_PAD_GPIO_19__GPIO_4_5定义为:

这个IOMUX_PAD宏是定义GPIO的关键宏,其原型为:

IOMUX_PAD宏有6个参数,每个参数的意思是:

| 参数 |

含义 |

| _pad_ctrl_ofs |

控制寄存器的偏移地址(16进制) |

| _mux_ctrl_ofs |

MUX控制寄存器的偏移地址(16进制), 用于选择引脚的功能 |

| _mux_mode |

MUX模式,bit0~3,范围0~7 |

| _select_input_ofs |

SELECT_INPUT寄存器偏移地址(16进制) |

| _select_input |

Daisy Chain模式, bit0~1,范围0~3 |

| _pad_ctrl |

bits to be set in register _pad_ctrl_ofs for configuration selection |

具体的含义要结合IMX6数据手册【Chapter 36 IMOUX Controller(IOMUXC)】的内容。

以下就GPIO_19这个管脚的配置进行说明:

1、_pad_ctrl_ofs

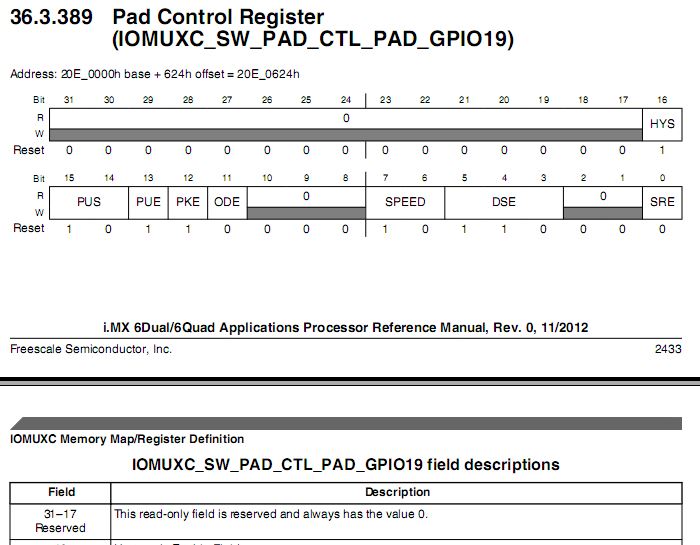

找到数据手册page 2433:

从上图可知:_pad_ctrl_ofs = 0x624

2、_mux_ctrl_ofs、_mux_mode

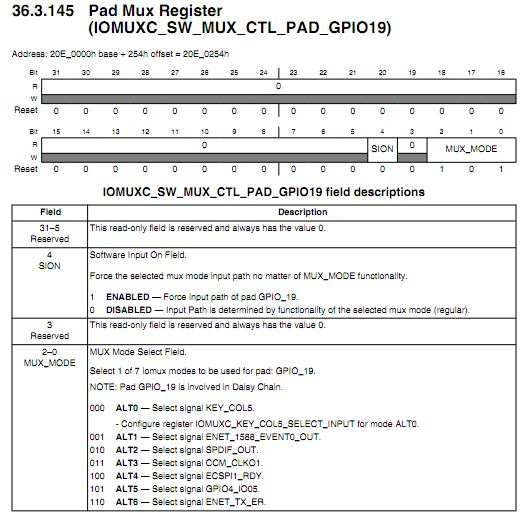

找到数据手册page 2055的内容:

如上图,_mux_ctrl_ofs取值为0x254,_mux_mode范围为000~110

只有_mux_mode = 0时,_select_input_ofs和_select_input才有效,其余时候_select_input_ofs和_select_input 都为0。

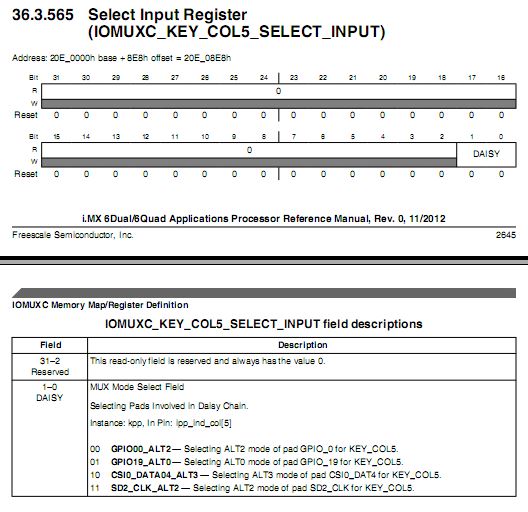

3、_select_input_of、_select_input

当_mux_mode = 0时,_select_input_ofs的取值需参考数据手册page 2654:

此时_select_input_ofs=0x8e8,_select_input=0x1

4、_pad_ctrl

_pad_ctrl一般取值为0

综上所述,GPIO_19的配置宏定义如下:

以上的宏定义来自imx6的linux源码的arm/arch/palt-mxc/include/mach/iomux-mx6q.h

1、普通设置

在配置串口时,pinctrl的配置信息如下所示:

这里的MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA在imx6dl-pinfunc.h文件中有如下定义:

将管脚的配置展开即: 0x35c 0x744 0x000 0x2 0x00x1b0b1

想知道这六个值都是什么意思,可以从两个路出发:①查找解读dts的文件,即看内核源码;②在网上查找相关知识。

1.1 查看源码对设备树文件的解读

首先在imx6dl-pinfunc.h文件中有对前5个变量的解释,如下图:

为了验证这5个变量,并查找第6个变量的含义,我们打开读取设备树文件的代码。

读取dts文件的文件为:linux-3.18.22/drivers/pinctrl/freescale/pinctrl-imx.c,实现函数名为:static int imx_pinctrl_parse_groups(。。。),如下:

这段代码中list = of_get_property(np, "fsl,pins", &size);实现了读取dts文件中的fsl,pin属性值,并保存在了list指针变量中。紧接着,分别将list中的值mux_reg、conf_reg、input_reg、mux_mode、input_val、config六个变量中,由名字可以猜测个大概,前5个得以验证,第六个表示config,config的值说白了就是对寄存器配置(上拉电阻、频率等等)的值,就是pad_ctrl的值。

因此对应关系如下:

0x35c | 0x744 | 0x000 | 0x2 | 0x0 | 0x1b0b1

---------------------------------------------------------------------------------------------------------

mux_ctrl_ofs | pad_ctrl_ofs | sel_input_ofs | mux_mode | sel_input | pad_ctrl

以上参数在参考手册怎么确定的呢?由于是对复用管脚的配置,于是在管脚复用的章节(IOMUXC)中查找。但是现确定pad name才方便,于是定义在External Signals and Pin Multiplexing章节,搜索MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA的中间部分:SD4_DAT7,如下图

可知UART2_TX_DATA是属于SD4_DAT7的ALT2,于是mux_mode=0x2即可。上图表格中最后一列SW_PAD_CTL_PAD_SD4_DATA7是config配置需要查找的名称,跳到管脚复用的章节(IOMUXC)中,找到SW_PAD_CTL_PAD_SD4_DATA7,如下所示:

如果直接取默认值的话结果是config=0x1b0b0,这里可以根据自己的需要(硬件)更改为与自己的板子匹配的值,我把最后SRE的值设置为1,即Fast Slew Rate,如下图说明:

OK,接下来是mux_ctrl_ofs、pad_ctrl_ofs、sel_input_ofs三个偏移值,这些值都是在复用管脚的章节确定的。因为pad name为SD4_DATA7,所以在找的时候可以拿它当关键字。

首先是mux_ctrl_ofs,找到IOMUXC_SW_MUX_CTL_PAD*开头的部分,结尾选择SD4_DATA7即可,如下图,

由”Address: 20E_0000h base + 35Ch offset = 20E_035Ch“中可知offset=35C,即mux_ctrl_oft=0x35c

其他的查找方法类似。pad_ctrl_ofs,查找IOMUXC_SW_PAD_CTL_PAD_SD4_DATA7一节,可知偏移值pad_ctrl_ofs=0x744

sel_input_ofs查找IOMUXC章节以SELECT_INPUT结尾的部分,中间选择UART2_TX,如果没有这里sel_input_ofs=0x000即可,对应的sel_input为0即可。如果有例如IOMUXC_UART2_UART_RX_DATA_SELECT_INPUT,即uart的rx管脚配置,如下图,所以RX的sel_input_ofs=0x904,这里选择对应的值“110 SD4_DATA4_ALT2 — Selecting ALT2 mode of pad SD4_DAT4 for UART2_RX_DATA..“所以RX(MX6QDL_PAD_SD4_DAT4__UART2_RX_DATA)的sel_input=0x6。