上一篇Linux C语言编程(上篇) | gcc的使用讲述了如何使用gcc进行编译,其中只是对hello.c这一个文件进行编译,那么当我们需要编译多个文件的时候该怎么做呢?

1.多文件编译实例

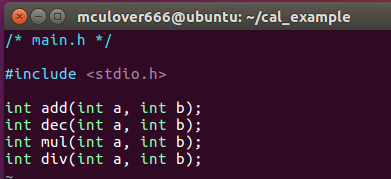

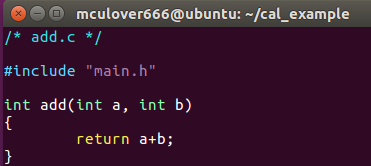

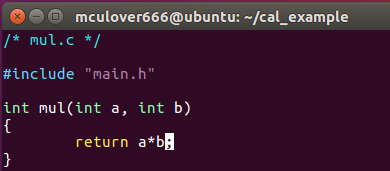

这个例子中分别在四个文件(add.c, dec.c, mul.c, div.c)实现相应的运算函数,在头文件main.h里声明,在主函数(main.c)进行调用,首先编写代码如下:

-

main.h

-

add.c

-

dec.c

-

mul.c

-

div.c

-

main.c

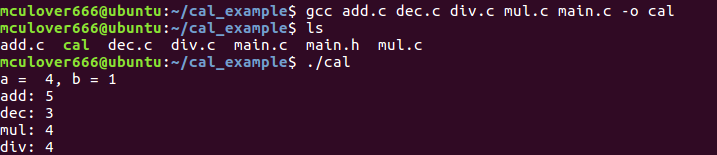

然后使用gcc添加多个文件进行编译:

gcc add.c dec.c mul.c div.c main.c -o cal

这个实例中只有5个源文件和1个头文件,可以直接一句gcc命令解决,那么,当我们需要编译的是包含几十个源文件的头文件的工程呢?这个时候就需要使用强大的make编译构建工具了~

2.make与makefile

make也属于GNU项目的一部分,是一个编译构建工具,当我,我们执行make命令时,makefile会告诉make工具如何编译和链接这些文件,所以,如何编写makefile是使用make工具的核心。

3.编写makefile

3.1.makefile组成

一个基本的makefile包含3部分:

- 目标体(target):make工具创建的目标体,目标文件或者可执行程序;

- 依赖文件(dependency_file):构建目标体所依赖的文件(原料)

- 命令(command):构建目标体所执行的命令

3.2.makefile基本格式

比如开头提到的实例,可以编写如下makefile:

然后执行make cal命令即可,注意:如果直接使用make,make工具会生成makefile文件中定义的第一个目标,所以此处可直接使用make:

3.3.makefile 伪目标

这些目标并没有依赖文件,所以称为伪目标,相当于执行命令的脚本,比如:

向之前的makefile添加clean伪目标:

可以看到删除命令执行:

3.4.makefile 变量

现在的makefile中还包含着大量的重复字符,所以可以使用变量代替~

3.4.1.变量定义

- 递归展开方式:在使用到该变量的时候进行替换,格式:

var = <value> - 直接展开方式:在定义处展开,并且只展开一次,格式:

var:= <value>

3.4.2.变量使用

使用$(<变量>)的格式使用。

3.4.3.变量分类

makefile中的变量分为以下四类:

- 用户自定义变量

- 预定义变量

- 自动变量

- 环境变量

3.4.3.1.预定义变量

| 变量名 | 描述 |

|---|---|

| CC | C编译器的名称,默认为cc |

| CXX | C++编译器的名称,默认为g++ |

| RM | 文件删除程序的名称,默认rm -f |

| CFLAGS | C编译器选项,无默认值 |

| CXXFLAGS | C++编译器选项,无默认值 |

现在可以将makefile改为如下形式:

3.4.3.2.自动变量

| 命令 | 描述 |

|---|---|

| $* | 不包含扩展名的目标文件名称 |

| $@ | 包含扩展名的目标文件名称 |

| $+ | 所有的依赖文件(可能包含重复) |

| &^ | 所有不重复的依赖文件 |

所以makefile可再次简化: