stm32 中断架构

编程语言

2018-12-23 00:07:26

阅读次数: 0

1. 初步了解

- stm32F4有两种CPU模式:特权模式和用户模式。当发生异常或中断时会进入到特权模式中

- stm32F4有两个系统栈,一个是MSP,一个是PSP。CPU在用户模式中使用PSP作为栈,当发生异常时,会从异常向量表的起始位置读取4byte (MSP),作为特权模式的栈

- stm32F4的中断架构分为:不可屏蔽异常和可屏蔽异常(将中断看作是一种特殊的异常),不可屏蔽异常是stm32F4的cpu core(cortex M4)决定,该core是ARM-V7M架构,在该架构中定义了NVIC(可嵌套的中断向量控制器),通过该控制器来分配其他的中断。

- 关于NVIC:有91个可屏蔽的中断通道,16级可编程优先级

- EXTI:外部中断控制器,可以trigger电平和边沿

2. 问题:

- 异常发生时,NVIC是否有一些状态寄存器?NVIC具体是什么样的?

- 在cortexM4中介绍:能够降低中断延时,电源管理控制

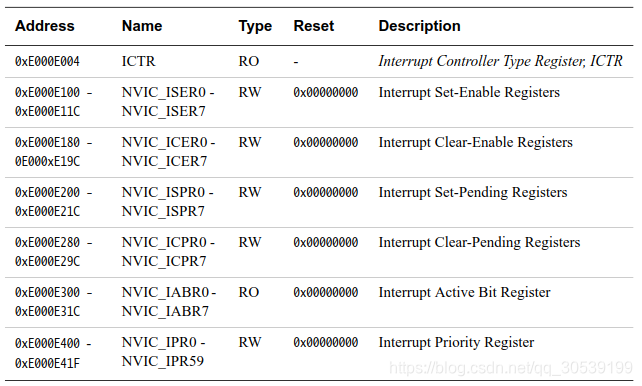

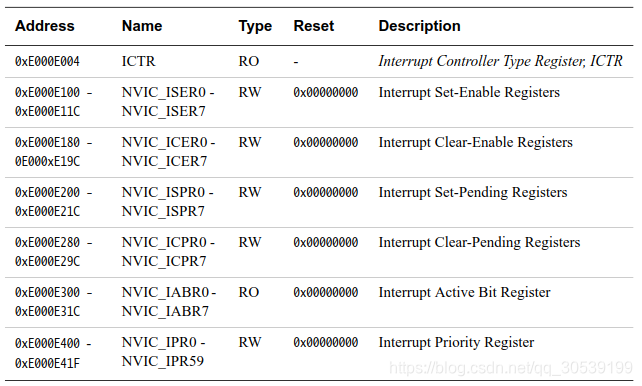

- 寄存器:

- 查看Active Bit register:在ARMV7 B3.4.1中可以看到,当中断发生时该寄存器对应位置会active

- NVIC作为ARMV7-M架构的一部分,主要用来管理中断(屏蔽,使能,状态,优先级等)

- ICTR寄存器主要可以看到CPU一共包含多少中断(cortex M4 Table 6-2可以看到)

3. 如何使用

- 中断优先级的机制是什么样的?

- 分成两组:抢占优先级和响应优先级。抢占优先级有抢占的特权,共四组。响应优先级只能决定中断优先级,不能抢占。

- 默认全部是枪战优先级0,即不具备抢占优先级能力。只具备响应优先级。那么默认的响应优先级如何确认?即中断向量表是怎么确认的?由硬件通道链接确认的吗?

- 中断嵌套如何处理?相关机制是什么样的?[留待后面进行补充]

转载自blog.csdn.net/qq_30539199/article/details/84980815