http://www.eeworld.com.cn/FPGA/2011/0330/article_1931_2.html

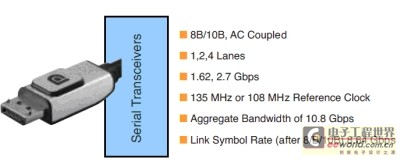

DisplayPort 一个特别重要的特性是,能够通过 VESA 的增强显示识别2010年 夏季刊37手把手课堂:FPGA 101数据 (EDID) 结构与不同的设备进行接口相连。EDID 并不是什么新事物。实际上多年以来设计人员一直在使用各种视频接口读取 EDID 的宿端设备参数,从而与设备进行接口连接。不过这些早期的 EDID 及相关接口 技术通常不包含高级可配置通信通道。如今借助 DisplayPort,VESA 为系统增添了智能性,不但能在源端(如机顶盒、DVD 播放器或 PC 图形卡)与宿端设备(如显示监控器)之间进行功能协调,而且还可优化通信参数。DisplayPort v1.1a 可协调的变量包括通道数量(1、2 或者 4)、每信道数据速率(1.62 或 2.7Gbps)、电压摆幅(0.2、0.6、0.8、1.2 V)、4 个级别的通道预加重以及链路时钟向下扩散。

由 CORE Generator 生成,并与LogiCORE 一道提供的接收宿端范例设计可提供范例 EDID(见图 3),以便满足 EDID 源端设备的读取需求,确保用户的最佳视觉体验。

图3 DisplayPort 接收高级方框图

宿端范例设计在 FPGA 内部的BRAM 中实施了 EDID 数据结构。DisplayPort 的源代码可通过 AUX 通道实现 I2C 协议。图 3 和图 4 显示了连接至源端的 DisplayPort 宿端的方框图。宿端的 Link 与 Stream Policy Maker属于宿端内核的组成部分,不过源端的 LinkPolicy Maker 具有更高的复杂性,将作为源代码随参考设计提供。EDID 通过I2C 接口与接受宿端进行接口连接。

I2C 协议非常适合针对 EDID 数据结构的连接,并常常用于这种类型的应用。I2C 控制器负责定位与管理在EDID 中发现的数据,并通过串行接口与 I2C 接口协议(通过 AUX 通道)将数据传输至宿端内核。在工作模式下,用户无需知晓 EDID 是否正被访问。用户可通过检测 I2C 总线来监控 ROM 的内容。在调试模式下,用户能够修改I2C 控制器,覆盖 EDID ROM 提供的 3位内容。I2C 提供控制信号,在与适当的开集输出相连时,可提供 I2C 主接口。

宿端内含名为“DisplayPort 配置数据(DPCD)”的数据结构,可以存储配置数据并作为宿端与源端都可读写的通信邮箱使用。源端一般使用跨 AUX 通道的 DPCD 内容(参见图 3 和图 4)。

图4 VESA DisplayPort v1.1a 主链路