Vivado Design Suite - HLx 版本

生产力成倍加速

Vivado Design Suite HLx 版本 - 加速高层次设计

Vivado® Design Suite HLx 现已提供部分可重配置功能,该功能随 Vivado HL Design Edition 和 HL System Edition 免费提供。保修期内的客户可重新生成其许可证,获得该特性。部分重配置可以降价提供给 Vivado WebPACK™ 版本。

Vivado HLx 版本可为设计团队提供实现基于 C 的设计、重用优化、IP 子系统重复、集成自动化以及设计收敛加速所需的工具和方法。与 UltraFast™ 高层次生产力设计方法指南相结合,这种特殊组合经过验证,不仅可帮助设计人员以高层次抽象形式开展工作,同时还可促进重复使用,从而可加速生产力。

加速高层次设计

软件定义 IP 生成 - Vivado 高层次综合 (HLS)

基于模块的 IP 和 Vivado IP 集成

基于模型的设计,集成 Model Composer 和 System Generator for DSP

加速验证

Vivado 逻辑仿真器

集成混合语言仿真器

集成 & 独立 编程与调试环境

加速验证超过 100 倍,通过 C、 C++ 或 SystemC 以及 Vivado HLS

验证 IP

加速实现

设计实现时间缩短 4 倍

设计密度提升 20%

在低端 & 中档产品中实现高达 3 速度级性能优势,在高端产品中实现 35% 功耗优势

=======================================================================

Vivado 高层次综合(HLS)

通过启用 C、C++ 和 System C 规范,加速 IP 创建

当今无线、医疗、军用产品和消费类产品应用中使用的高级算法比以往更加复杂。Vivado® 高层次综合(HLS)在所有 Vivado HLx 版本中以免费升级形式提供,可以实现直接使用 C,C++ 以及 System C 语言规范对赛灵思可编程器件进行编程,无需手动创建 RTL,从而可加速 IP 创建。 Vivado 高层次综合使系统和设计架构师支持ISE® 和 Vivado 设计环境,能够以更快速的方式创建 IP。

算法描述摘要、数据类型规格 (整数、定点或浮点) 以及接口 (FIFO, AXI4, AXI4-Lite, AXI4-Stream)

支持任意精度数据类型、视频以及 DSP 等的广泛库,查看各种库下的以下部分

指令驱动型架构感知综合可提供最优的 QoR。

在竞争对手还在手动开发 RTL 的时候快速实现 QoR。

使用 C/C++ 测试平台仿真、自动 VHDL 或 Verilog 仿真和测试平台生成加速验证

多语言支持和业界最广泛的语种覆盖率。

自动使用 Xilinx 片上存储器、DSP 元素和浮点库

Vivado HLS 不仅支持专门用于 ISE 设计套件的较早架构,而且还能够以 Vivado HLx 的一部分自动安装.

=======================================================================

加速集成

基于模块的 IP 和 VIVADO IP Integrator 集成

Vivado® Design Suite 可提供业界首款即插即用型 IP 集成设计环境并具有IP 集成器特性,从而解决了 RTL 设计生产力问题。

Vivado IP 集成器可提供基于 Tcl、设计期正确的图形化设计开发流程。IPI 特性可提供具有器件和平台意识的互动环境,能支持关键 IP 接口的智能自动连接、一键式 IP 子系统生成、实时 DRC 和接口修改传递等功能,此外还提供强大的调试功能。

在 IP 之间建立连接时,设计人员工作在“接口”而不是“信号”的抽象层面上,从而大幅提高了生产力。 这通常采用业界标准的 AXI4 接口,不过 IP 集成器也支持数十个其它接口。

设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vivado HLS、System Generator、Xilinx SmartCore™ 和 LogiCORE™ IP 创建的 IP、联盟成员 IP 和自己的 IP。通过利用 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

Vivado IP 集成器的优势包括:

在 Vivado 集成型设计环境中的紧密集成

IP Integrator 层次化子系统在整个设计中的无缝整合

快速捕获与支持重复使用的 IP Integrator 设计封装

支持图形和基于 Tcl 的设计流程设计

快速仿真与多设计视窗间的交叉探测

支持所有设计域

支持处理器或无处理器设计

算法集成 (Vivado HLS 和 System Generator) 和 RTL-level IP

融 DSP、 视、模拟、嵌入式、连接功能和逻辑为一体

注重设计生产力

可在设计装配过程中,通过复杂接口层面连接实现 DRC

常见设计错误的识别和纠正

互联 IP 的自动 IP 参数传递

系统级优化

自动设计辅助

=======================================================================

验证 IP

验证. 加速.

Xilinx 验证 IP (VIP) 系列将赋予用户在仿真环境下更高效便捷地验证和调试其设计的能力。验证 IP 核是特定构建的验证模型,旨在确保正确的互操作性和系统行为。EDA 产业的公司面向各种基于标准的接口开发 VIP,其中包括 AXI、PCIe、SAS、SATA、USB、HDMI 和 ENET 等。使用 VIP 的优势包括提高设计质量以及通过重复使用缩短时间周期等。

Xilinx VIP 内核是基于 SystemVerilog 的仿真模型,不仅可通过 ARM 许可的断言提供全面的 AXI 协议检查,而且还支持所有主要仿真器,该模型随 Vivado 免费提供。Xilinx 提供的 VIP 不仅可用于使用 AXI 组件层次(AXI-MM、AXI_Stream)的设计,而且还可用于处理系统 (Zynq®-7000) 设计。

AXI 验证 IP

支持 AXI3、AXI4 和 AXI-Lite 协议

支持所有协议数据位宽及地址位宽、传输类型与响应

全面的 AXI 协议检查器支持

集成的 ARM 许可证协议断言

事务处理级协议校验(突发类型、长度、大小、锁定类型、高速缓存类型)

可配置为主、从或通过工作模式

AXI Stream 验证 IP

支持 AXI4-Stream 协议

支持所有协议数据位宽及地址位宽、传输类型与响应

全面的 AXI Stream 协议检查器支持

集成的 ARM 许可证协议断言

事务处理级协议校验(突发类型、长度、大小、锁定类型、高速缓存类型)

可配置为主、从或通过工作模式

Zynq-7000 验证 IP

允许针对处理器系统接口为可编程逻辑进行 AXI 事务处理验证

可替换 Zynq-7000 BFM

全面的 AXI 协议检查

支持 AXI3 协议

集成的 ARM 许可证协议断言

支持所有 9 个 Zynq-7000 AXI 接口

基于任务的 API 可进行事务处理编程

AXI_HP 的 32/64 位数据位宽、AXI_GP 的 32 位数据位宽以及 AXI_ACP 的 64 位数据位宽(加速器缓存一致性端口)

验证 IP

在 Zynq Ultrascale+ MPSoC 中支持可编程逻辑与处理器系统之间的 AXI 事务验证

在 Zynq Ultrascale+ MPSoC 中支持 11 个 AXI PL 到 PS 数据接口

包含片上存储器和 DDR 外部存储器模型

支持所有 AXI 接口(符合 AXI 4.0)

基于 SystemVerilog 任务的 API

允许所有受 Zynq UltraScale+ MPSoC 支持的突发长度和突发大小

随 AXI VIP 一同提供协议检查功能

=======================================================================

Xilinx 软件开发套件 (XSDK)

Xilinx 软件开发套件 (XSDK) 是集成型设计环境,可在任何 Xilinx 获奖微处理器上创建嵌入式应用: Zynq® UltraScale+ MPSoC、Zynq-7000 SoC、和业界领先的 MicroBlaze™ 软核微处理器。SDK 是首款应用 IDE,可实现真正的同质及异构多处理器设计、调试和性能分析。 它提供了如下优势:

支持 Zynq UltraScale+ MPSoC、 Zynq-7000 SoCs、和 MicroBlaze

随 Vivado 设计套件提供给嵌入式软件开发人员,也可单独免费下载获取。

基于 Eclipse 4.5.0 和 CDT 8.8.0 (自 2016.3 版起)

完整的集成设计环境 (IDE) 可直接用于连接 Vivado 嵌入式硬件设计环境

实现完整的软件设计和调试流程支持,包括全新多处理器和硬件/软件协调试功能

编辑器、编译器、生成工具、闪存管理和 JTAG/ 调试集成

整套库与器件驱动

作为 RTOS 集成的 FreeRTOS 现已针对所有平台提供

Xilinx 软件命令行工具 (XSCT) 用于脚本

系统调试程序

Xilinx 系统调试器是一款支持 Zynq UltraScale+ MPSoC、Zynq-7000 SoC 和 MicroBlaze 核的集成型调试器。 可使用 XSCT 通过命令行获得,也可在调试应用的 SDK GUI 中获得。它支持所有常见的调试特性,如设置断点或观察点、通过程序执行步进、查看程序变量和协议栈以及查看系统中存储器的内容等。还可以在同一调试环境中同时调试多处理器系统中不同处理器上的程序。例如在基于 Zynq 或基于 Zynq UltraScale+ 的设计中,系统调试器可通过单个 JTAG 线缆在同一个调试会话中显示两个 ARM CPU 和多个 MicroBlaze 软处理器,从而可在硬件化处理系统和已添加至可编程逻辑中的任何附加处理系统之间实现前所未有的深入观察。

基于开源目标通信框架 (TCF)

同质和异构多处理器支持

层次分析

裸机与 Linux 开发,包括 Linux OS-Aware 调试

支持 SMP 和 AMP 设计

关联每个内核的硬件与软件断点。

支持 NEON™ 库

除了全功能标准软件调试工具的所有特性外, 该系统调试工具还可在 PS 的处理器与 PL 的处理器及硬件之间实现交叉触发。软件编程工具可通过直观的 GUI 设置向 PL 上的外部处理器或硬件发出触发或从这些组件接受触发的条件。 ,不仅可采集数据,而且还可在不同的工具中显示,从而可在调试过程中提供帮助。

定制设计感知

Xilinx SDK 了解 Vivado 设计套件中定义的定制嵌入式硬件设计。在该设计基础上,系统会自动配置一些重要的参数,其中包括存储器映射、外设寄存设置、工具和库路径、编译器选项、JTAG 和闪存设置、调试器连接以及Linux、裸机板支持包 (BSP)。 该定制的设计感知预配置与自动生成的关键系统软件完美地整合在了一起,您只需花费少量的学习时间便可快速进行软件开发了。

驱动程序和库

XSDK 为所有支持的 Xilinx IP 硬核提供了可用户定制的驱动程序,并提供了符合 POSIX 规范的内核库、网络和文件处理库。这些库和驱动程序可以根据功能需要、存储器要求和硬件功能为定制设计进行缩放。

软件特性描述

XSDK 提供了性能分析工具,可帮助用户识别因在可编程逻辑中和在处理器上的交互而可能造成的代码瓶颈。支持分级特性描述,能让用户查看是什么调用了函数、或者什么调用函数对处理器性能的影响最大。

系统性能分析和优化

创建高性能 SoC 系统需要时间,还要了解软件和外设之间的交互情况。 帮助您收集性能数据、实现系统可视化的工具对于满足性能目标要求至关重要。Xilinx 系统性能分析工具箱(XSDK 中提供)可帮助您对系统进行建模、评测、分析和优化。在新的性能视图中,您能查看:

处理器使用率

每个工作周期的指令

高速缓存未命中/击中率

读写时延和 PL 到 PS 接口的带宽

系统性能分析工具箱帮助您与系统互动,能调节系统达到您所需的性能目标。

利用上述工具,您能快速发现瓶颈,并就如何进行系统软硬件分区设定假设性情境。您用 AXI 流量生成器可对 IP 块进行性能建模,在完成前这些 IP 块会在可编程逻辑中。完成分析后,就可通过优化软件源代码、拆分处理器和可编程逻辑之间的功能或者将全部功能迁移到可编程逻辑上来提高性能。

=======================================================================

PetaLinux 工具

PetaLinux 工具提供在 Xilinx 处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件。理想适用于提升设计生产力,该解决方案与 Xilinx 硬件设计工具协同工作,为 Zynq® UltraScale+™ MPSoC、 Zynq®-7000 SoC、和 MicroBlaze™ 简化了 Linux 系统的开发。

PetaLinux 开发工具(主机)

PetaLinux 工具可帮助简化基于 Linux 产品的开发;您可以使用下列工具来完成从系统启动到执行的所有操作:

命令行接口

应用、器件驱动程序、库生成器以及开发模板

可引导的系统映像生成器

调试代理程序

GCC 工具

集成的 QEMU 全系统仿真器

自动化工具

支持 Xilinx 系统调试器

使用这些工具,开发人员可以定制引导载入程序、Linux 内核或 Linux 应用。他们可以通过网络或 JTAG 在随附的全系统仿真器 (QEMU) 或物理硬件上添加新的内核、器件驱动程序、应用和库,以及启动并测试软件协议栈。

定制的 BSP 生成工具

随着新添加的特性和设备,PetaLinux 工具使开发人员能够同步软件平台和硬件设计。

PetaLinux 工具将会为 Xilinx 嵌入式处理 IP 核、内核以及引导载入程序配置自动生成定制的 Linux 开发板支持包(其中包括器件驱动程序)。该性能让软件工程师把精力集中于有附加值的应用上,而非低层次的开发任务。

Linux 配置工具

PetaLinux 包含工具用于定制引导加载程序、Linux 内核、文件系统、库和系统参数。

这些配置工具可与 Xilinx 硬件开发工具和特定于定制硬件的数据文件充分集成,以便根据工程师指定的该器件的地址自动为 Xilinx 嵌入式 IP 核构建和部署器件驱动程序。

软件开发工具

PetaLinux 工具集成开发模板,软件团队可创建定制器件驱动器、应用程序、库和 BSP 配置。

一旦建立了产品的软件基本组件(BSP、器件驱动程序和内核应用等)PetaLinux 工具可帮助开发人员打包和分配(便于 PetaLinux 开发人员轻松安装和使用的)所有软件组件。

参考 Linux 发行版

PetaLinux 提供完整的参考 Linux 发行版,面向 Xilinx 器件进行了集成和测试。参考 Linux 发行版包括二进制和源 Linux 封装包括:

引导载入程序

CPU 优化的内核

Linux 应用 & 库

C & C++ 应用开发

调试

线程和 FPU 支持

集成式网络服务器便于远程管理网络和固件配置

快速启动的 Linux 映像

所有 PetaLinux 开发板支持包(BSP) 均提供了预配置的引导载入程序、系统映像和比特流。通过这些内置工具,您可以执行单个命令为物理硬件或随附的全 QEMU 系统仿真器 部署和启动这些组件。

使用 PetaLinux ,开发人员可以在安装后大约 5 分钟之内启动并运行其基于 Xilinx 的硬件,并随时可以进行应用、库和驱动程序的开发。

=======================================================================

https://www.xilinx.com/html_docs/xilinx2017_3/SDK_Doc/sdk_getting_started/sdk_getting_started.html#sdk_getting_started

Xilinx SDK入门

Xilinx®软件开发套件(SDK)是一个集成开发环境(IDE),用于开发针对Xilinx嵌入式处理器的嵌入式软件应用。SDK适用于使用Vivado®DesignSuite创建的硬件设计。SDK基于Eclipse开源标准。SDK功能包括:

功能丰富的C / C ++代码编辑器和编译环境

项目管理

应用程序构建配置和自动Makefile生成

错误导航

良好集成的环境,用于嵌入式目标的无缝调试和分析

源代码版本控制

系统级性能分析

专注于配置FPGA的专用工具。

可启动映像创建

Flash编程

可编写脚本的命令行工具

Xilinx SDK开发流程概述

使用Xilinx®SDK为Vivado®嵌入式系统设计开发软件应用程序的典型流程如下:

调用Xilinx SDK。出现提示时,打开现有工作区或创建新工作区。

注意:创建新工作区时,请使用从Vivado®IPIntegrator生成的硬件平台。

开发您的软件应用程序 Xilinx SDK提供了作为电路板支持包一部分的软件库和驱动程序的文档。

SDK为应用程序创建默认链接描述文件。链接器生成工具可用于修改内存映射。

准备好在硬件目标上测试应用程序时,通过创建运行/调试配置来运行/调试应用程序。此外,如果需要,将硬件比特流下载到FPGA器件。

您可以与软件开发并行设计硬件平台。您可以通过指向不同的版本让Xilinx SDK更新您的硬件平台规范,并让它修改新硬件平台的工作空间。

本产品包含Eclipse Project(http://www.eclipse.org/)开发的软件。

=========================================================================

嵌入式硬件组件

Xilinx®Vivado®IP集成器为可以创建的各种嵌入式硬件提供了极大的灵活性。通常,使用IP集成器创建的嵌入式平台包含:

一个或多个MicroBlaze™或ARM Cortex A9处理器

FPGA内部的易失性存储器

FPGAM外部的易失性(如DDR或SDRAM)和/或非易失性(闪存)存储器

IP控制外部接口,例如GPIO,UART或以太网MAC

调试IP,例如处理器跟踪信号

硬件开发人员创建的其他自定义IP

软件开发人员的任务是编写在硬件平台上存在的处理器上运行的软件,以执行特定于应用程序的任务。Xilinx为Xilinx IP和一些基本软件组件提供驱动程序,以帮助加速此类软件开发。

FPGA比特流

FPGA比特流是包含FPGA的编程信息的文件。必须使用特定的比特流对Xilinx FPGA器件进行编程,才能使其成为嵌入式硬件平台。该比特流通常由创建嵌入式平台的硬件设计者提供。

FPGA编程是将比特流加载到FPGA中的过程。在开发阶段,FPGA器件使用Vivado®等实用程序或SDK中的菜单选项进行编程。这些工具将比特流传输到板载FPGA。在生产硬件中,比特流通常放在非易失性存储器中,并且硬件配置为在通电时对FPGA进行编程。

=========================================================================

硬件平台规范

硬件平台规范文件从硬件设计中捕获所有信息和文件,软件开发人员需要为该硬件编写,调试和部署软件应用程序。

通常,使用Vivado®开发硬件的硬件设计人员会在目录中创建硬件平台规范。然后,软件开发人员在Xilinx软件开发工具包(SDK)中使用此信息。该规范的主要组成部分是:

XML格式的硬件描述

与硬件描述对应的FPGA比特流

与比特流对应的块RAM存储器映射(BMM)文件

Zynq®-7000 AP SoC初始化文件

ps7_init.tcl文件。这是在将任何应用程序下载到目标之前要获取并执行的预初始化文件。这个tcl包含clock,pll和ddr初始化代码。

ps7_init.c / .h文件。这些文件是ps7_init.tcl文件的C等效文件。在创建FSBL应用程序项目期间使用ps7_init.c和.h文件。

SDK使用硬件描述文件来检测硬件中存在的处理器和内存映射外围设备。

FPGA比特流使用硬件设计人员创建的硬件对FPGA器件进行编程。

BMM文件是硬件描述中使用的内部存储器的描述。它根据需要用程序或数据填充内部块RAM。

查看硬件平台规范

通过双击Project Explorer 视图中硬件平台项目下的HDF / XML文件,可以查看硬件系统的硬件平台规范。SDK打开硬件平台规范查看器,显示有关硬件设计的以下概述信息:

设计资料

设计中的处理器列表,处理器存储器映射以及处理器子系统中的外围设备列表

设计中存在的IP块列表。

导入硬件平台规范文件

SDK要求您在开始开发C / C ++应用程序项目之前指定硬件平台规范文件。

更改硬件规格文件

更新硬件平台规范文件时,SDK会将该信息与项目中存储的文件的先前版本进行比较。

只要硬件规范文件发生更改,SDK就会自动在工作区中进行更改,以使其适应新的硬件设计。它可能会提供有关您可以进行的其他更改的建议。除了这些自动和建议的更改之外,应用程序级别可能还需要进行其他更改以匹配新硬件。

例如,如果从设计中删除外围设备,则在检测到硬件更改后,BSP将立即自动更新。这意味着应用程序将无法再使用已删除外围设备的API,并且任何文件或对已删除外围设备的引用都将显示为错误。

SDK执行以下操作:

使用新的硬件规范文件,比特流和BMM文件更新硬件项目。

如果从硬件设计中删除了处理器子系统,则SDK将关闭软件项目,基于先前硬件设计的任何板支持包以及针对已移除的处理器子系统的任何应用程序项目。

通过硬件处理器子系统的更改来更新板级支持包项目。这包括删除已移除外围设备的驱动程序以及添加新外围设备的默认驱动程序。

重新构建与硬件项目相关的所有软件项目。

监视硬件项目更改

如果您同时开发硬件(使用Vivado®DesignSuite)和软件,则可能需要使用SDK来监视从Vivado Design Suite导出的原始硬件规范文件的任何更改。SDK中的硬件项目维护指向原始硬件规范文件的链接,并监视文件以查找影响该硬件的软件项目的更改。这包括以下更改:

添加或删除处理器或外围设备

对处理器内存映射的更改

更改硬件组件参数

=====================================================================================

使用XSDB

Xilinx®系统调试器(XSDB)使用Xilinx hw_server作为底层调试引擎。SDK将每个用户界面操作转换为一系列TCF命令。然后,它处理系统调试器的输出,以显示正在调试的程序的当前状态。它使用Xilinx hw_server与硬件上的处理器通信。

调试工作流程如下图所示:

工作流程由以下组件组成:

可执行的ELF文件:要调试应用程序,必须使用为调试编译的可执行文件和可链接格式(ELF)文件。调试ELF文件包含调试器的其他调试信息,以在源代码和从该原始源生成的二进制文件之间建立直接关联。有关更多信息,请参阅构建配置。

调试配置:要启动调试会话,必须在SDK中创建调试配置。此配置捕获启动调试会话所需的选项,包括可执行文件名,要调试的处理器目标以及其他信息。有关更多信息,请参阅启动配置。

SDK Debug Perspective:使用Debug透视图,您可以在Workbench中管理程序的调试或运行。您可以通过设置断点,暂停已启动的程序,单步执行代码以及检查变量的内容来控制程序的执行。

您可以重复修改代码,构建可执行文件以及在SDK中调试程序的循环。

推荐的调试器用法

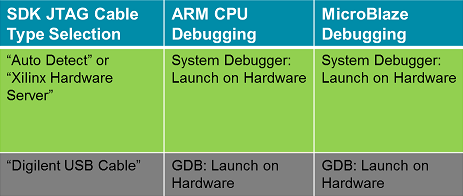

下表显示了调试器的建议用法。颜色键是:

绿色:推荐用法

橙色:不太喜欢

灰色:不推荐(但支持)

注意:对于所有处理器和电缆,建议对SDK中的所有调试流使用系统调试器。

查看IP注册详细信息

Xilinx®SDK现在支持使用硬件(system.hdf)视图或使用寄存器视图在调试期间查看IP寄存器详细信息。

使用Hardware(system.hdf)视图查看IP寄存器详细信息

创建成功的硬件项目后,SDK将在“ 编辑器”视图中打开system.hdf文件。该文件现在显示对设计中存在的IP块寄存器的交叉引用。

=============================================================================

Xilinx软件命令行工具(XSCT)

诸如Xilinx®软件开发套件(Xilinx SDK)等图形开发环境对于快速开发新的处理器架构非常有用。它有助于抽象并将大多数常见功能组合成逻辑向导,即使是初学者也可以使用。但是,工具的可编程性对于提供扩展该工具的灵活性也是必不可少的。在开发将每晚运行的回归测试或运行开发人员经常使用的一组命令时,它尤其有用。

Xilinx软件命令行工具(XSCT)是Xilinx SDK的交互式脚本命令行界面。与其他Xilinx工具一样,XSCT的脚本语言基于工具命令语言(Tcl)。您可以交互方式运行XSCT命令,也可以编写自动化命令脚本。XSCT支持以下操作:

创建硬件,板级支持包(BSP)和应用程序项目

管理存储库

设置工具链首选项

配置和构建BSP /应用程序

在硬件目标上下载并运行应用程序

通过运行Bootgen和program_flash工具创建和刷新启动映像。

本参考指南旨在提供开发针对Xilinx系列处理器的软件开发和调试脚本所需的信息。

在阅读本文档时,您会注意到Xilinx生产的各种产品的缩写。例如:

使用ps7源代码意味着这些文件针对Zynq® - 7000 AP SoC系列产品,并在SoC特别是双核Cortex™ARM®A9处理器。

使用的psu源代码中的指的是此代码的目标是一个ZYNQ的UltraScale +™片上多核装置,其包含的Cortex四核ARM A53,双核ARM R5,ARM马里400 GPU,和一个的MicroBlaze™处理器基于平台管理单元( PMU)。

硬件定义文件(HDF)用于将包含处理器的硬件系统的信息传输到嵌入式软件开发工具,如Xilinx SDK(XSDK)和Xilinx软件命令行工具(XSCT)。它包括有关实例化哪些外设,时钟,存储器接口和存储器映射的信息。

微处理器软件规范(MSS)文件用于存储有关BSP的信息。它们包含BSP的OS信息,与硬件设计的每个外围设备相关的软件驱动程序,STDIO设置以及优化和调试信息级别等编译器标志。

XSCT命令

Xilinx®软件命令行工具允许您从命令行创建完整的Xilinx SDK工作区,调查硬件和软件,调试和运行项目。

XSCT命令大致分为以下类别。随后描述每个类别中的命令。

目标连接管理

目标登记册

程序执行

目标记忆

目标下载FPGA / BINARY

目标重置

目标断点/观察点

Jtag UART

杂

JTAG访问

SDK项目

HSI命令

connect

Connect to hw_server/TCF agent.

Syntax

connect [options]

Allows users to connect to a server, list connections or switch between connections.

Options

Option Description

-host <host name/ip> Name/IP address of the host machine

-port TCP port number

-url URL description of hw_server/TCF agent

-list List open connections

-set Set active connection

-new Create a new connection, even one exist to the same url

-xvc-url Open Xilinx Virtual Cable connection

Returns

The return value depends on the options used.

-port, -host, -url, -new: of the new connection or error if the connection fails

-list: list of open channels or nothing when there are no open channels

-set: nothing

Example(s)

connect -host localhost -port 3121

Connect to hw_server/TCF agent on host localhost and port 3121.

connect -url tcp:localhost:3121

Identical to previous example.

Target Registers

The following is a list of registers commands:

rrd

rwr

Target Memory

The following is a list of memory commands:

mrd

mwr

osa

memmap

Target Download FPGA/BINARY

The following is a list of download commands:

dow

verify

fpga

Target Reset

The following is a list of reset commands:

rst

HSI Commands

XSCT provides higher level abstraction commands for Hardware Software Interface (HSI) commands and you normally do not have to run the HSI commands in XSCT. However, if there is a need, you can run HSI commands by prefixing hsi to each HSI command. For example, hsi open_hw_design.

Note: You can use only one set of the commands at a time on any design. Interleaving both sets of commands will lead to internal errors. For example, a design opened with hsi open_hw_design cannot be closed using closehw.

XSCT keeps track of the open designs (both software and hardware). The table below lists the HSI commands and their corresponding XCST commands.

HSI Command Corresponding XSCT Command

hsi open_hw_design

openhw

hsi close_hw_design

closehw

hsi open_sw_design

openbsp

hsi close_sw_design

closebsp

Any modifications done to the software design or the BSP, using HSI commands, are stored in memory. Before using any other XSCT commands, you should run the updatemss XSCT command, to ensure that these modifications are stored in the .mss file of the BSP.

For more details on the HSI commands and their usage, refer to the Generating Basic Software Platforms Reference Guide (UG1138).

======================================================================================

软件分析

分析是确定每个例程的软件执行时间的方法。您可以使用此信息来确定设计中的关键代码片段和最佳代码放置。经常调用的例程最适合放置在快速存储器中,例如高速缓冲存储器。您还可以使用分析信息来确定是否可以将一段代码放在硬件中,从而提高整体性能。

Xilinx SDK支持TCF分析和gprof分析。这两种分析方式彼此显着不同。对于基于gprof的分析,硬件系统应具有用于产生周期性采样中断的定时器中断。

注意: gprof目前仅支持Cortex A9和Microblaze处理器。