3. Developing Reusable Verification Components

本章描述了构成典型验证环境的基本概念和组件。它还展示了如何使用经过验证的层次结构组合这些组件来创建可重用的验证组件。

—Modeling Data Items for Generation

— Transaction-Level Components

— Creating the Driver

— Creating the Sequencer

— Creating the Monitor

— Instantiating Components

— Creating the Agent

— Creating the Environment

— Enabling Scenario Creation

— Managing End of Test

— Implementing Checks and Coverage

3.1 Modeling Data Items for Generation

为了帮助调试和跟踪事务,uvm_transaction基类通过get_transaction_id()成员函数提供对唯一事务号的访问。此外,uvm_sequence_item基类(扩展自uvm_transaction)还包含get_transaction_id()成员函数,允许序列项与最初生成它们的序列相关联。

3.1.1Inheritance and Constraint Layering

为了满足验证目标,验证组件用户可能需要通过向类定义添加更多约束来调整数据项生成,在SystemVerilog中,这是通过继承完成的。

3.1.2Defining Control Fields

枚举

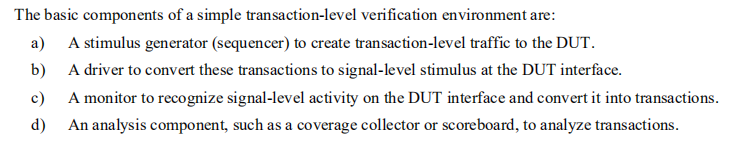

3.2 Transaction-Level Components

UVM中的TLM接口为组件之间发送和接收事务提供了一组一致的通信方法。组件本身在测试台上被实例化并连接,以执行验证设计所需的不同操作。

UVM中TLM接口的一致性和模块化允许组件在替换和/或封装时被重用。每个组件都有其接口,而不管其内部实现如何。本章讨论如何将这些类型的组件封装到经过验证的体系结构(验证组件)中,从而进一步提高重用。

上图显示了将各个组件分组到可重用的接口级验证组件中。开发人员不是单独重用低级类,而是创建一个组件,以一致的方式封装它的子类,促进一致的体系结构使这些组件更容易学习、采用和配置

3.3 Creating the Driver

drv的角色是按照接口协议将数据项驱动到总线。drv从seqr中获取数据项以便执行。UVM类库提供uvm_driver基类,所有驱动类都应该直接或间接地从这个基类扩展。驱动程序有一个TLM端口,通过它与seqr通信。drv还可以实现一个或多个运行时阶段(运行和pre_reset - post_shutdown)来完善其操作。

3.4 Creating the Sequencer

seqr生成刺激数据并将其传递给drv执行。UVM类库提供uvm_sequser基类,它由请求和响应两种类型参数。uvm_sequser基类包含允许序列与驱动程序通信所需的所有基本功能。使用适当的参数化直接实例化uvm_sequencer

uvm_sequencer #(simple_item, simple_rsp) sequencer;3.5 Connecting the Driver and Sequencer

drv和seqr通过TLM连接,drv的seq_item_port连接到seqr的seq_item_export。seqr生成要通过export提供的数据项。drv通过它的seq_item_port消费数据项,并可选地提供响应。组件包含drv和seqr实例的组件在它们之间建立连接,如下图。

uvm_driver中的seq_item_port定义了drv用来获取序列中下一个item的一组方法。这种交互的一个重要部分是drv与总线同步的能力,以及在适当的时间与seqr交互以生成数据项的能力。seqr实现了一组方法,允许drv和seqr之间灵活而模块化的交互。

3.5.1 Basic Sequencer and Driver Interaction

drv和seqr之间的基本交互是使用get_next_item()和item_done()任务完成的。drv使用get_next_item()来获取下一个要发送的随机项。发送到DUT后,drv向seqr发出信号,表示使用item_done()处理。

备注:其详细联结如下:

- drv调用seq_item_port.get_next_item();

- seqr调用wait_for_grant();

- seqr调用begin_tr(req);

- seq调用start_item(req);

- seq调用randomize()函数;

- seq调用finish_item(req)函数;

- 在上一步的继续上,seqr相继调用send_request(req)函数;

- drv调用send()函数;

- drv调用seq_item_port.item_done();

- seqr调用wait_for_item_done()函数

- seqr调用end_tr()函数

3.5.2 Querying for the Randomized Item

除了get_next_item()任务之外,uvm_seq_item_pull_port类还提供了另一个任务try_next_item()。如果没有可供执行的数据项,此任务将在相同的模拟步骤中返回。您可以使用这个任务让drv执行一些空闲事务,例如当没有有意义的数据需要传输时,需要刺激DUT。

3.5.3 Fetching Consecutive Randomized Items

3.5.4 Sending Processed Data back to the Sequencer

3.5.5 Using TLM-Based Drivers

内置在uvm_driver中的seq_item_port是一个双向端口。它还包括标准的TLM方法get()和peek(),用于从seqr请求item,并put()提供响应。

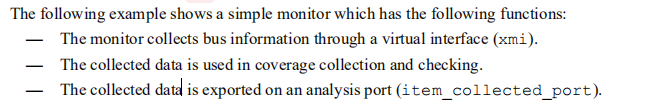

3.6 Creating the Monitor

monitor负责从总线中提取信号信息并将其转换为事件,数据和状态信息。 此信息可通过标准TLM接口和通道提供给其他组件和测试编写器。 mon不应该依赖于其他组件(例如drv)收集的状态信息,但它可能需要依赖于特定于请求的id信息才能正确设置响应的序列和事务ID信息。

监视器功能应限于始终需要的基本监视。 这可以包括协议检查 - 应该是可配置的,以便可以启用或禁用 - 以及覆盖范围收集。 其他高级功能(如记分板)应在监视器顶部单独实施。

3.7 Instantiating Components

type_id::create()方法是一个特定于类型的静态方法,它从工厂返回所需类型的实例。要创建的参数与标准构造函数参数、字符串名和父组件相同。

3.8 Creating the Agent

agent使用TLM连接实例化和连接drv、seqr和mon,如前几节所述。为了提供更大的灵活性,agent还包含配置信息config和其他参数。

class simple_agent extends uvm_agent;

... // Constructor and UVM automation macros

uvm_sequencer #(simple_item) sequencer;

simple_driver driver;

simple_monitor monitor;

// Use build_phase to create agents's subcomponents.

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase)

monitor = simple_monitor::type_id::create("monitor",this);

if (is_active == UVM_ACTIVE) begin

// Build the sequencer and driver.

sequencer = uvm_sequencer#(simple_item)::type_id::create("sequencer",this);

driver = simple_driver::type_id::create("driver",this);

end

endfunction : build_phase

virtual function void connect_phase(uvm_phase phase);

if(is_active == UVM_ACTIVE) begin

driver.seq_item_port.connect(sequencer.seq_item_export);

end

endfunction : connect_phase

endclass : simple_agent3.9 Creating the Environment

3.9.1 The Environment Class

环境类是可重用组件的顶级容器,它实例化并配置所有子组件。大多数验证重用发生在环境级别,其中用户实例化一个环境类并为特定的验证任务配置它和它的agent。

class ahb_env extends uvm_env;

int num_masters;

ahb_master_agent masters[];

`uvm_component_utils_begin(ahb_env)

`uvm_field_int(num_masters, UVM_ALL_ON)

`uvm_component_utils_end

virtual function void build_phase(phase);

string inst_name;

super.build_phase(phase);

if(num_masters ==0))

`uvm_fatal("NONUM",{"'num_masters' must be set";

masters = new[num_masters];

for(int i = 0; i < num_masters; i++) begin

$sformat(inst_name, "masters[%0d]", i);

masters[i] = ahb_master_agent::type_id::create(inst_name,this);

end

// Build slaves and other components.

endfunction

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction : new

endclass3.9.2 Invoking build_phase