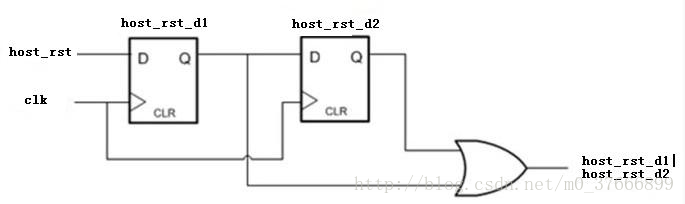

滤掉小于1个周期glitch的原理图如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

always@(posedge clk_in or negedge rst)

begin

if(~rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2;

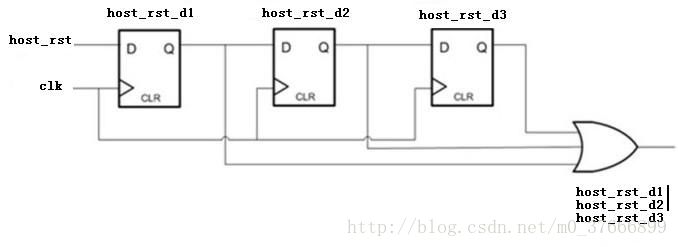

endmodule滤掉大于1个周期且小于2个周期glitch的原理图如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

reg host_rst_d3;

always@(posedge clk_in or negedge rst)

begin

if(~rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

host_rst_d3 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

host_rst_d3 <= host_rst_d2;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2 | host_rst_d3;

endmodule