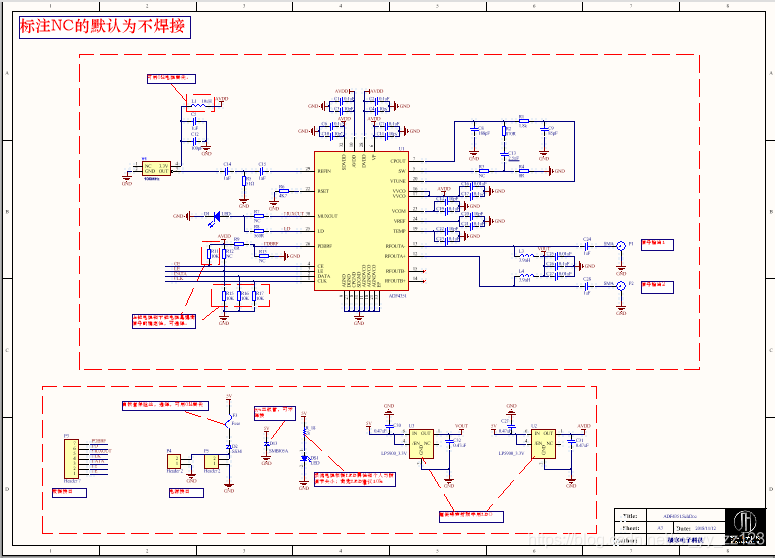

- 照列先上原理图和PCB(使用的AD软件设计),原理图上备注详细说明,也建议大家养成这个好习惯,发现问题就及时记录,因为很多时候当时明白,可是过段时间就忘记了~~~~

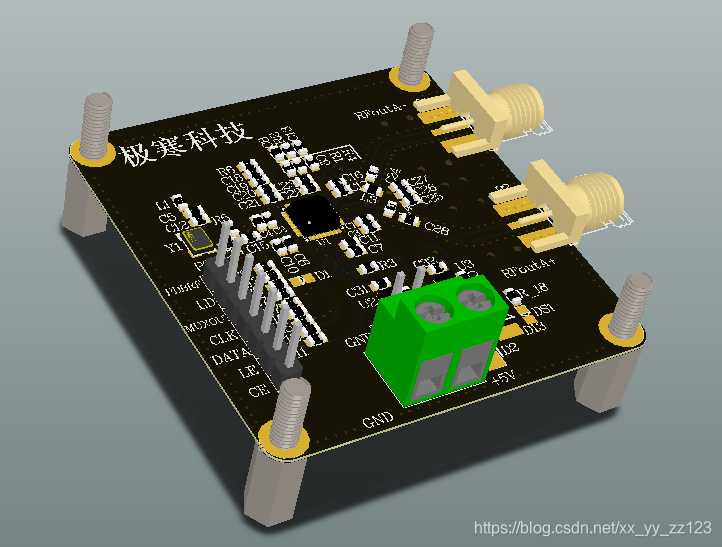

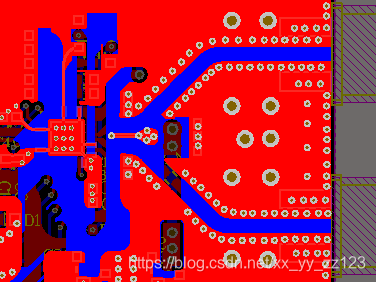

- PCB也是采用的3D封装,看着舒服,嘻嘻,丝印基本加好,方便调试焊接,设计完之后一定要记得通过报告(Report)看有没有漏连接的地方,鄙人之前就是疏忽大意漏连一根线导致开板浪费掉了……

- 芯片简介

ADF4350/ADF4351具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/16分频电路,用户可以产生低至35Mhz/137.5 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

输出频率范围:137.5 MHz至4400 MHz;

小数N分频频率合成器和整数N分频频率合成器;

具有低相位噪声的VCO;

可编程1/2/4/8/16分频输出;

均方根(RMS)抖动:小于0.4 ps rms(典型值);

电源电压:3.0 V至3.6 V;

逻辑兼容性:1.8 V;

可编程双模预分频器:4/5或8/9;

可编程的输出功率;

RF输出静音功能;

三线式串行接口;

模拟和数字锁定检测;

在宽带宽内快速锁定模式;

周跳减少;

- 使用经验和建议

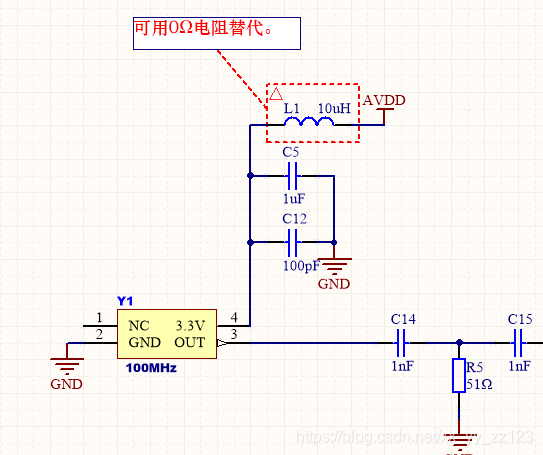

- ADF4351一般作为系统的信号源,因此它晶振非常关键,直接会影响AD4351出来信号的稳定性,所以大家在选择器件以及布局的时候都要格外谨慎,器件一定要选择正规大厂商的,晶振布局的时候紧挨着主芯片,使晶振信号线尽可能的做短,另外也可以使用外部信号作为ADF4351的时钟,鄙人的板子只设计了板载晶振,调试结果也还可以。 如果是放在系统机箱里边的,一定要做好EMC,建议加一个独立的屏蔽盒。

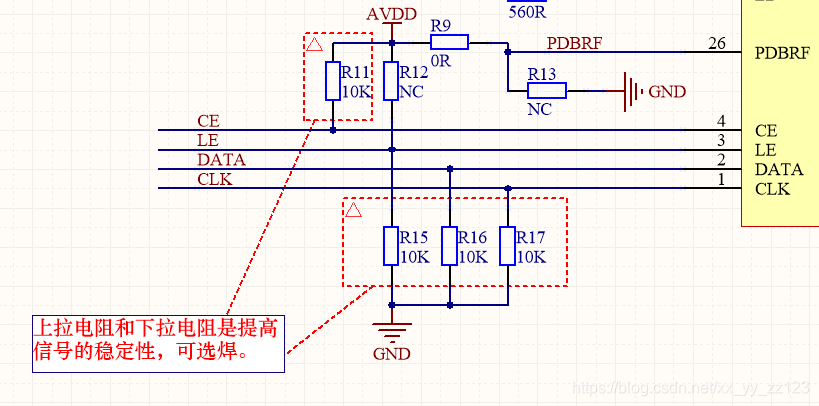

2. 与单片机通信这里的几个管脚可以选择加上下拉电阻,以提高通信信号的稳定性,一般不焊接的情况问题也不大,当然肯定是建议焊接上保险一些哈~

3. 电源也非常关键,十分建议大家一定采用低噪声的LDO芯片,鄙人这里采用的是超低噪声射频专用芯片LP5900,效果还不错。

4. 在PCB设计的时候过孔一定要加足够,提高地信号的完整性。

5. 如果自己手工焊接,一定要注意ADF4351芯片管脚不要短路了,稍有不慎可能就会烧坏片子

- 结语,总的来说ADF4351注意晶振的器件质量以及布局布线合理性,使用上基本没啥问题。

下面是鄙人设计的原理图和PCB源文件,另附了程序仅供参考哈

链接: https://pan.baidu.com/s/11ZwsC_yG4VYksxcblDSD-Q

提取码: rkws