Design Compiler

1.

DC默认的设计环境:同步时钟,上升沿

2.

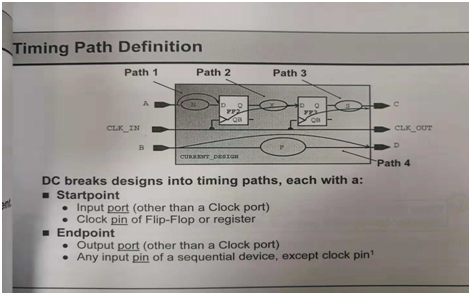

时钟路径划分以及判断约束是否满足步骤

三个步骤:a. 把需要综合的设计拆分成时序路径的组合

b. 计算每条路径的延时

c. 用路径延时和期望到达的时间作比较,判断约束是否满足

四条路径

起始点:输入端口(不包括时钟端口),时钟引脚

终点: 输出端口(不包括时钟端口),时序逻辑的输入引脚(不包括时钟引脚)

3.

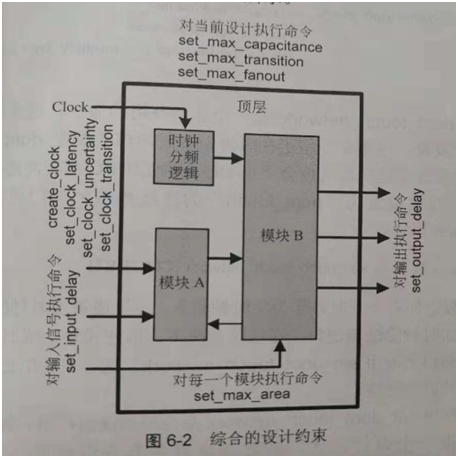

设定时钟的period,latency,transiton,uncertainty,还有对所有的输入信号执行命令input delay,对所有的输出信号执行命令 output delay。

对当前设计执行命令set_max_capacitance,set_max_transition,set_max_fanout

对每一个模块执行命令set_max_area

4.

create_clock命令用于定义有特定周期和波形的时钟对象,-period选项定义时钟周期,而-waveform选项控制时钟的占空比和起始边沿。

下例指定端口Clk为时钟类型,周期2ns,时钟正边沿开始于0ns,下降边沿发生在1ns,通过改变下降沿的值,可以改变时钟的占空比。

create_clock -period 2 -waveform [list 0 1] [get_ports Clk] 时钟的单位由工艺库定义,通过report_lib <lib_name> 或者 get_attribute<lib_name> time_unit_name 命令查看时钟单位。

此时钟的时钟周期为2ns。如果creat_clock命令中没有 -waveform 选项,则时钟默认 rises at 0ns with 50% duty cycle 。

注意:

在某些情况下,模块可能只包括组合逻辑,为定义这一模块的延迟约束,可生成一个虚时钟,并指定相对于虚时钟的输入和输出延迟。也可选择使用set_max_delay和set_min_delay来约束这样的模块。

create_generated_clock命令用于设计内部生成的时钟。这一命令可用于描述作为主时钟函数的分频/倍频时钟。

create_generated_clock -name <clock name> -source <clock source> -divide_by <factor> | -multiply_by <factor>

5.

理想的时钟有无限的驱动能力,zero rise/fall transtion times; zero skew; zero insertion delay or latency。

时钟树buffer 和skew balancing 是在CTS阶段,CTS是在综合后执行,用的是IC Compiler工具。在DC中,时钟需要排除在设计规则约束(max_transition,max_capacitance)之外。

The recommended approach to dealing with clocks is to model estimated skew,latency and transition times during synthesis.

6.

set_clock_uncertainty -setup Tu [get_clocks CLK] Tu包括时钟skew jitter margin

uncertainty 也可以用在时钟域之间,set_clock_uncertainty -setup Tu -from <Clk1> -to <Clk2>

7.

clock latency可分为souce latency和network latency【 clock network delay = source latency + network latency , "clock network delay" seen in a default timing report】

source latency是这clock信号来源到芯片的clock输入端的delay【source latency from the actual clock origin to the create_clock port or pin -used for either ideal or propagated clocks (post layout)】

network latency是指芯片clokc输入端到flip-flop clock输入的delay【network latency from the create_clock port or pin to the register clock pins 】

命令:create_clock -period 10 [get_ports CLK]

set_clock_latency -source -max 3 [get_clocks CLK]

set_clock_latency -max 1 [ get_clocks CLK ] #pre-layout

##set_propagated_clock [get_ports CLK] ## post-layout

8.

关于时钟的约束

set_clock_latency命令用于定义在综合时估计的时钟插入延迟,这主要用于布图前综合和时序分析。所估计的延迟值是时钟树网络插入(在布图阶段)产生延迟值的近似值。

set_clock_uncertainty命令让用户定义时钟扭斜信息。基本上此命令用于给时钟的建立和保持时间增加一定的余量。布图前阶段可比布图后阶段增加更多的余量。

强烈建议用户在布图前和布图后阶段都指定一定的余量,这样做的主要原因是使芯片少受制造工艺偏差的影响。

set_clock_transition命令很有用,用于进行布图前综合和时序分析。这个命令使DC对时钟端口或引脚使用指定的转换值(因为时钟网络伴有大的扇出,所以在布图前为时钟信号的转换时间设定一个固定值是必要的)

set_propagated_clock 用于当设计已完成时钟树网络插入的布图后阶段。在这种情况下,将用传统的延迟计算方法求出延时。

creat_clock -period 5 [get_ports Clk]

set CLOCK [get_clocks Clk]

set_clock_latency -source -max 4 $CLOCK

set_clock_latency -max 2 $CLOCK #######################(可被pro计算出来)

set_clock_transition -max 0.08 $CLOCK ##################(可被pro计算出来)

set_clock_uncertainty -setup 0.5 $CLOCK

#set_propagated_clock [get_ports Clk]

9.

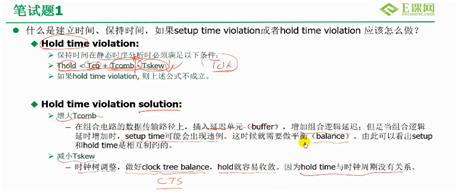

setup:在时钟到来之前,数据保持稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器。

(Tclock>Tclock_q_max+Tlogic_max+Tseup+Tskew)(Tskew考虑时钟树向后偏斜的情况)

hold:在时钟到来之后,数据保持稳定不变的时间, 如果保持时间不够,数据同样不能被打入触发器。

(Tlogic_min+Tclock_q_min >Tskew+Thold)(Tskew考虑时钟树向前偏斜的情况)

数据到达时间:launch time +Tclka + Tco + Tdata

数据要求时间(setup):capture time + Tclkb - Tsetup

setup slack = T+Tskew - Tco -Tdata -Tsetup(负的skew)

数据要求时间(保持):capture time + Tclkb + Thold

hold slack = Tskew + Thold - Tco -Tdata (正的skew)

10.

降频一般是可以解决setup violation的,但是如果出现hold violation, 如果负slack的值比较大,一般要修改设计或约束,如果负slack值较小,可以在P&R阶段通过insert buffer 来fix掉

recovery:有些类似于setup检查,是指撤销复位时,rst变到非复位状态的电平必须在clk之前一定的时间到来,可以保证clk在采样时,DFF处于非复位状态

removal:有些类似与hold检查,但又不完全相同,它是指复位时,rst在clk到来之后还需要维持的时间,否则会出现复位不成功

clock skew:clock在不同时序器件clk脚上的时间差异叫做clock skew

clock uncertainty:clock在时序器件clk脚上的不确定性,包括clock jitter和clock skew两部分的总和.

clock transition:clock信号的skew时间。分为上升沿时间和下降沿时间。

clock gating:指门控时钟。由于低功耗的要求,有些模块会停止工作。通过停掉clock减少这些模块的耗电.

clock jitter:clock源是芯片外部管脚引入或是内部PLL产生的。clock的每个周期时间都会有微小的偏差,这种偏差叫做clock jitter.

clock latency:clock源到时序器件的clk脚的延迟叫做clock latency.

clock tree:从一个clock源出发,clock网络经过多级buffer,到达每个时序器件的clk脚。为了保证从clock源到每个器件clk脚的延时相差不多,clock在布局布线时做成树形网络结构,叫做clock tree

11.

12.

set_input_delay 命令 用于输入端口

set_input_delay -max 23.0 -clock CLK {datain}

set_inuput_delay -min 0.0 -clock CLK {datain}

上述两条指令为信号datain指定了23ns的最大输入延时约束和0ns的最小输入延时约束,换言之,输入信号datain的建立时间要求为7ns,而保持时间要求为0ns。

如果,-min和-max选项都被省略的话,最大和最小输入延时规范使用相同的值。

13.

set_output_delay 命令 用于输出端口,表示在时钟边沿到来之前数据有效所需要时间。

set_out_delay -max 19.0 -clock CLK {dataout}

为信号dataout指定19ns的输出延时约束,这意味着在时钟沿后11ns数据有效。

注意:1. 在布图前阶段,有时有必要对选择的信号进行过紧约束以最大化建立时间,因此压缩额外时序余量以减少综合-布图迭代次数。为了达到这一目的,可在上述命令中指定过紧的约束值而我“愚弄”DC。切记,过分地过紧约束设计将导致不必要的面积增大和功耗增加。

2.当布图后利用原位优化设计修正保持时间违例时,也可使用负值【如 -0.5】提供额外的时序余量。

参考文献:

高级ASIC芯片综合

E课网

DC user guide

http://www.eefocus.com/sunleijun/blog/10-09/195236_f7476.html