目录

Computer Components - Top Level View 计算机组成顶层视图

Example of Program Execution 程序执行示例

Bus Interconnection Scheme 总线互连方案

Physical Realization of Bus Architecture 总线结构的物理实现

PCI(Peripheral Component Interconnection) Bus 外设组件互连标准

Computer Components - Top Level View 计算机组成顶层视图

Instruction Cycle 指令周期

Two steps: 1)Fetch 2)Execute

1)Fetch Cycle

程序计数器(Program Counter, PC)存储要取出的指令的地址;

处理器(Processor)从内存(memory)中取出PC所指向的指令;

指令加载进指令寄存器(Instruction Register, IR);

处理器翻译指令并执行相应操作

2)Execute Cycle

Processor-memory(处理机-存储器):Data transfer between CPU and main memory

Processor I/O(处理器输入输出):Data transfer between CPU and I/O module

Data processing:Some arithmetic or logical operation on data

Control:Alteration of sequence of operations

Combination of above

Instruction Cycle State Diagram 指令循环状态图

Example of Program Execution 程序执行示例

图中Memory中:

Step1:300~302为指令存储的地址 --> 指令加载进IR(指令寄存器);指令300 -> 取出操作数0003

Step2:940~941为操作数地址 --> 操作数加载进AC

Step3:加载指令301进IR;指令301 -> 取出操作数相加

Step4:取出操作数0002,与0003相加后,结果存储在AC中

Step5:加载指令302进IR;指令302 -> 将AC中的结果存入941(原操作数0002的地址)

Step6:将结果存入地址941中

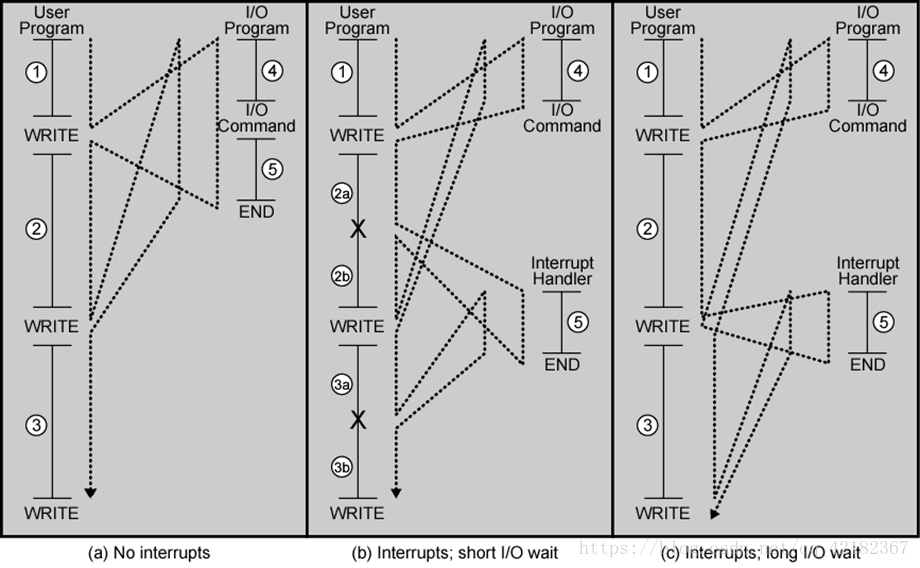

Interrupts 中断

中断:其他模块(例如I/O)可能中断正常处理顺序的机制

Interrupts:Mechanism by which other modules (e.g. I/O) may interrupt normal sequence of processing

Program:overflow / division by zero

Timer(计时器):Generated by internal processor timer(由内部处理器定时器生成 )/ Used in pre-emptive multi-tasking(用于抢占式多任务处理 )

I/O:from I/O controller

Hardware failure:memory parity error(存储器奇偶误差 )

Program Flow Control 程序流程控制

Interrupt Cycle 中断周期

添加到指令循环中 -> 处理器检查中断(用中断信号表示) -> 如果没有中断,获取下一条指令 -> 如果中断未决 -> 暂停执行当前程序 -> 保存上下文 -> 将PC设置为中断处理程序的起始地址 -> 进程中断 -> 恢复上下文并继续中断程序

Instruction Cycle with Interrupts 包含中断的指令周期

Instruction Cycle with Interrupts - State Diagram

Multiple Interrupts

1. Disable Interrupt 禁用中断

处理器在处理一个中断时将忽略其他中断。 中断保持未决,并在第一个中断被处理后进行检查。中断按发生的顺序进行处理。

2. Define priorities 定义优先级

低优先级的中断可以被高优先级的中断所中断(Low priority interrupts can be interrupted by higher priority interrupts)

当优先级较高的中断被处理完后,处理器就返回到之前的中断。

Multiple Interrupts - Sequential Multiple Interrupts – Nested(嵌套)

ISR:中断服务程序

Connecting 连接

Buses 总线

总线:连接两个或多个设备的通信路径(A communication pathway connecting two or more devices)

Usually broadcast ; Often grouped

Data Bus:

Carries data:Remember that there is no difference between “data” and “instruction” at this level

Width is a key determinant of performance(宽度是性能的关键决定因素 ):8, 16, 32, 64 bit

Address Bus:

Identify the source or destination of data:e.g. CPU needs to read an instruction (data) from a given location in memory

Bus width determines maximum memory capacity of system:e.g. 8080 has 16 bit address bus giving 64K address space

Control Bus:

Control and timing information / Memory read/write signal / Interrupt request / Clock signals

Bus Interconnection Scheme 总线互连方案

总线的外观:电路板上的平行线,带状电缆,母板上的带状连接器 (例如PCI(周边元件扩展接口)),成套电线

Physical Realization of Bus Architecture 总线结构的物理实现

单总线(single bus)存在的问题:

传播延迟(Propagation delays):长数据路径意味着总线使用的协调(co-ordination of bus use)会对性能产生不利影响(If aggregate data transfer approaches bus capacity)

大多数系统都使用多总线来克服这种问题

总线类型:

dedicated(专用):分开的数据总线与地址总线 (Separate data & address lines)

Multiplexed(多路复用):Shared lines,Address valid or data valid control line

优点:fewer lines

缺点:More complex control,Ultimate performance(最大性能)

Bus Arbitration 总线仲裁

多个模块同时控制总线(如, CPU and DMA(直接存储器存取) controller)

一次只能有一个模块可以控制总线,仲裁可以是集中的,也可以是分散的(Arbitration may be centralised or distributed)

Centralised:Single hardware device controlling bus access; May be part of CPU or separate

Distributed:Each module may claim the bus; Control logic on all modules

PCI(Peripheral Component Interconnection) Bus 外设组件互连标准

PCI Bus Lines:

(required)

Systems lines:Including clock and reset

Address & Data:32 time mux lines for address/data(用于地址/数据的32time多路复用线路 )

Interrupt & validate lines (中断和验证线):Interface Control(接口控制)

Arbitration:Not shared,Direct connection to PCI bus arbiter (直接连接到PCI总线仲裁器)

Error lines

(Optional)

Interrupt lines:Not shared

Cache support (缓存支持)

64-bit Bus Extension (64位总线扩展):Additional 32 lines,Time multiplexed (时间复用),2 lines to enable devices to agree to use 64-bit transfer

JTAG/Boundary Scan (JTAG / 边界扫描):For testing procedures