下面列出ZYQN内部核心的几个框架:

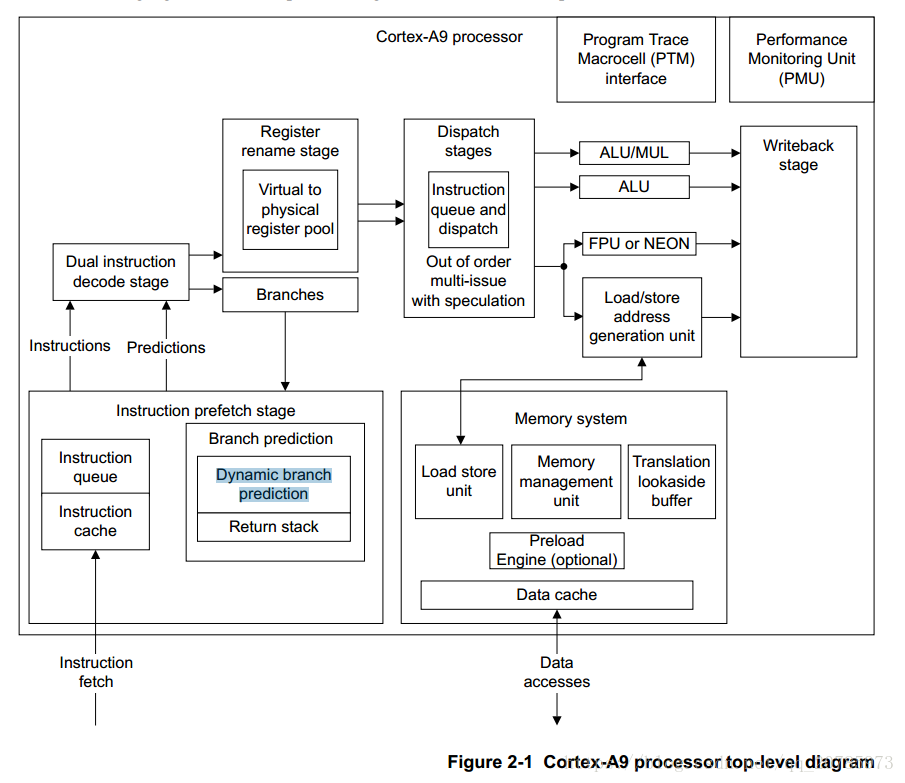

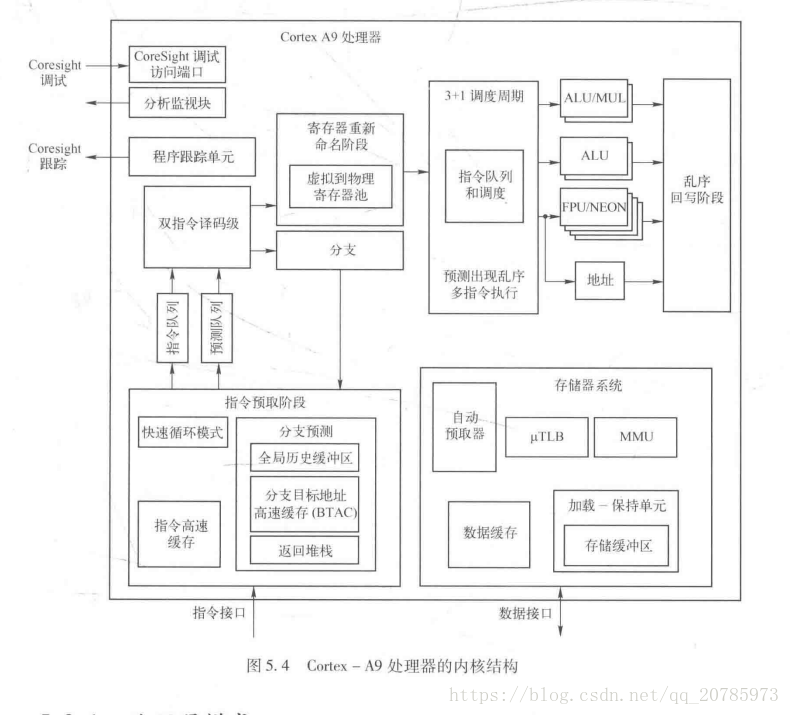

在ARM Cortex A9处理器中,存储指令首先通过主存储器或者L2 cache加载到L1指令cache中,在instructionprefetch stage阶段,主要是做指令预取以及分支预测。然后指令通过Instruction Queue队列被送到解码器进行指令的解码工作。解码器支持两路解码,可以同时解码两条指令。在Register rename stage阶段会做寄存器重命名,避免机器指令不必要的顺序化操作,提高处理器的指令级并行能力。在Dispatch stage阶段,这里支持4路猜测发射和乱序执行(Out-of-Order Multi-Issue with Speculation),然后在ALU/MUL/FPU中乱序执行。存储指令会计算有效地址并发射到内存系统中的LSU部件,最终LSU部件最终会去访问L1数据cache。

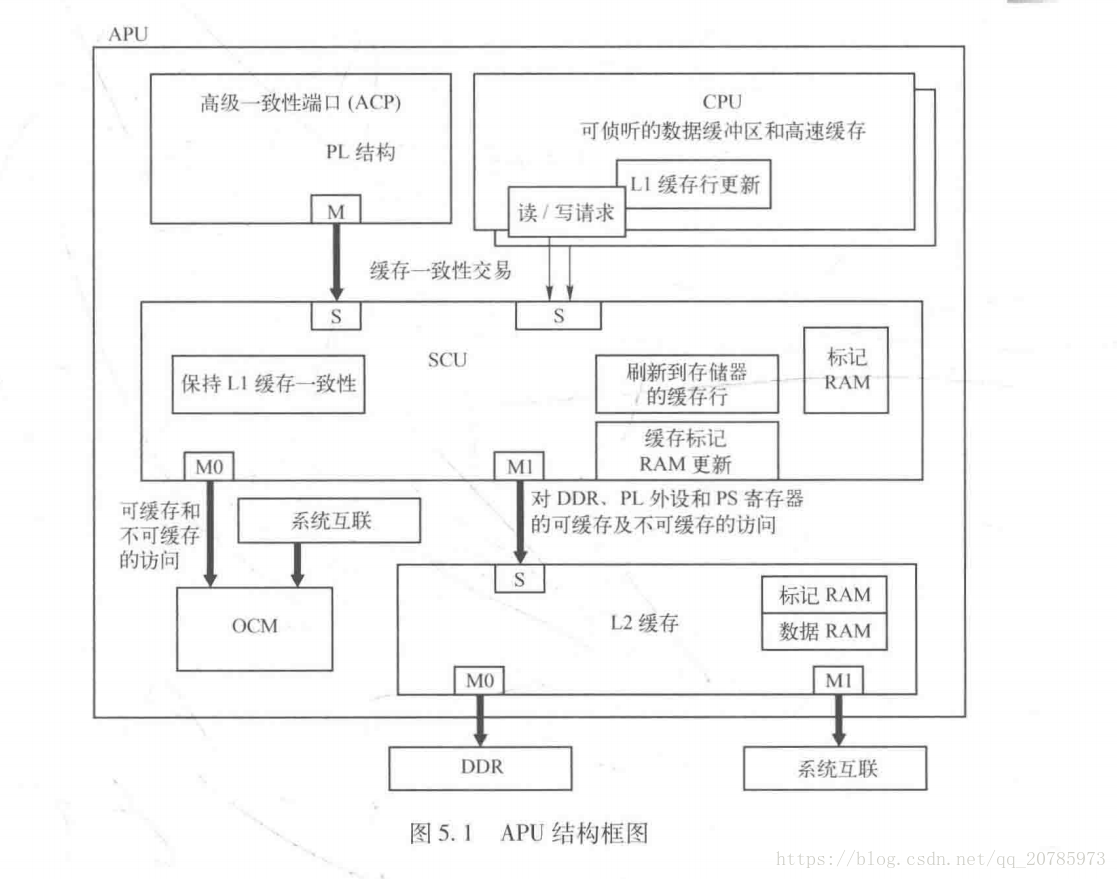

在多处理器环境下,还需要考虑cache的一致性问题。L1和L2cache控制器需要保证cache的一致性,在CortexA9中cache的一致性实现MOSEI协议,在最糟糕情况下访问主存储器DDR,并将数据重新传递给LSQ,完成一次存储器读写的全过程。

关于上面详细概念和知识,请参考书籍:Xilinx Zynq-7000 嵌入式系统设计与实现 基于ARM Cortex-A9双核处理器和Vivado的设计方法。

下载该书籍链接:https://download.csdn.net/download/qq_20785973/10628445