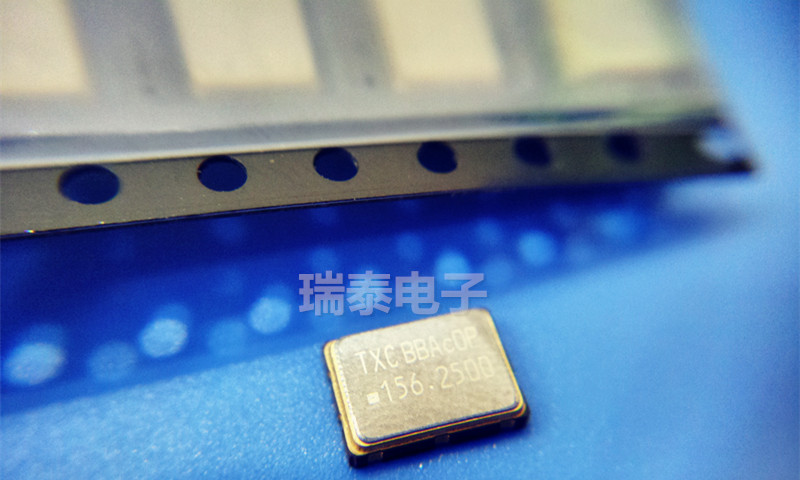

差分晶振近年来逐渐出现在我们的视线中,以及越来越多的电子工程师会更青睐差分晶振。随着信息化的发展,差分晶振高性能、低功耗、低噪声的优点,使其成为很多设计适合的方案。但仍有不少电子工程师对差分晶振选型上存在误区以及盲点。差分晶振与常规晶振不同,差分晶振有不同的输出信号,LVPECL,LVDS,HCSL是差分晶振通用的输出信号,其中前两者较长被应用于各大差分系统中,那么两者有什么区别吗,在电路工作原理上又有着怎样的差异呢?瑞泰电子资深工程师郭工带领各位认识LVPECL与LVDS的电路认识。

LVPECL即Low Voltage PosiTIve Emitter-Couple Logic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源。想要了解LVPECL电路,我们要首先认知PECL电路。PECL即PosiTIve Emitter-Couple Logic,也就是正发射极耦合逻辑的意思,使用5.0V电源。PECL 是由ECL 演变而来的,ECL 即Emitter-Couple Logic,也就是发射极耦合逻辑。该电路是一种非饱和型的数字逻辑电路,电路内晶体管工作在线性区或截止区,速度不受少数载流子的存储时间的限制,所以它是现有各种逻辑电路中速度最快的一种, 能满足高达10Gbps工作速率。ECL 有两个供电电压VCC和VEE。当VEE接地时,VCC接正电压时,这时的逻辑称为PECL;当VCC 接地时,VEE接负电压时,这时的逻辑成为NECL,VEE一般接-5.2V电源;一般狭义的ECL 就是指NECL。由于PECL/LVPECL可以和系统内其他电路共用一个正电源供电,所以PECL/ LVPECL相对于ECL应用更为广泛。起初的PECL器件是将VCC接+5V,后来为了直接利用广泛使用的3.3V和2.5V电压,出现了VCC=3.3V/2.5V的LVPECL(Low Voltage PECL)。

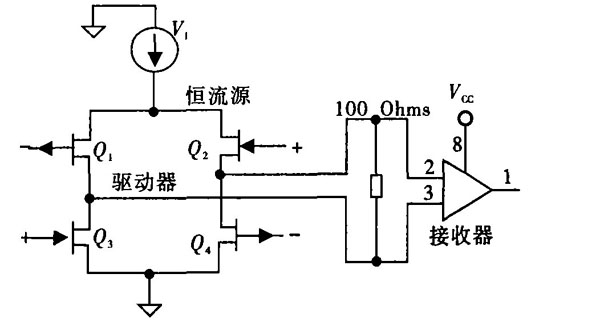

LVDS(Low Voltage Differential Signaling)它是一种低摆幅的差分信号技术,它使得信号能够在差分PCB 线对或平衡电缆上以几百的Mbps 的速率传输,其低压幅以及低电流驱动输出实现了低噪声以及低功耗。LVDS(Low Voltage Differential Signaling)是一种小振幅差分信号技术,LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。