1、GENERAL DESCRIPTION

The SGM4073 is both a timer for resetting a mobile device and an advanced load management switch for applications requiring a highly integrated solution.

SGM4073既是一个可以复位移动终端设备的定时器也是一个性能优越的负载管理开关。

If the mobile device is off, holding nSR0 low (by pressing power-on key) for 1.9s turns on the PMIC.

手机关机后,保持nSR0低电平1.9s即可打开PMIC电源管理芯片。

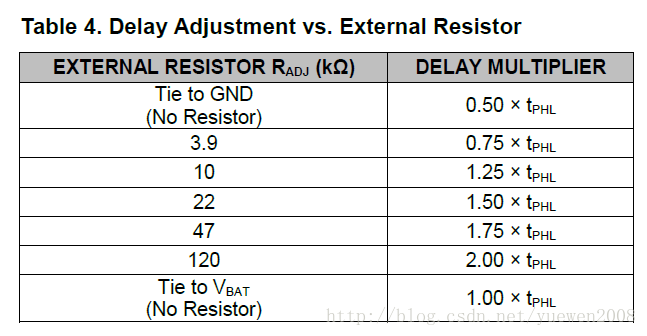

As a reset timer, it has one input and one fixed delay output. It generates a fixed delay of 7.7s by disconnecting the PMIC from the battery power supply for 468ms. Then the load switch is turned on again to reconnect the battery to the PMIC such that PMIC goes into power-on sequence. The reset delay can be customized by connecting an external resistor to the DELAY_ADJ pin. Refer to Table 4

作为一个复位定时器,有一路输入和一路固定的延时输出,通过产生一个固定的7.7s延时来断开PMIC和电池之间的供电,然后重新打开PMIC重新上电开始工作,达到一个硬件复位的效果。复位延时时间可以通过连接到DELAY_ADJ管脚的外部电阻来调节。

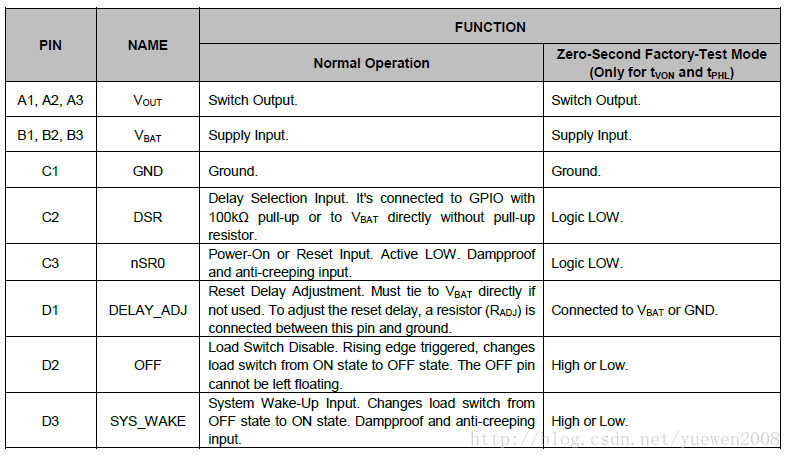

2、PIN DESCRIPTION

Vout为复位芯片的输出端,连接系统以及PMIC等。

Vbat为芯片输入端,连接电池正极输入。

Nsr0位上电或复位输入端,通常连接powerkey

D1位复位延时时间的电阻调节端,外接电阻不同复位延时时间不同。

D2负载开关关闭脚,上升沿触发,该管脚不能悬空,通常接AP的一个GPIO,通过GPIO来控制开关。

D3系统唤醒输入端,可以将芯片从off状态切换到on状态,通常连接系统的USB的VBUS端。

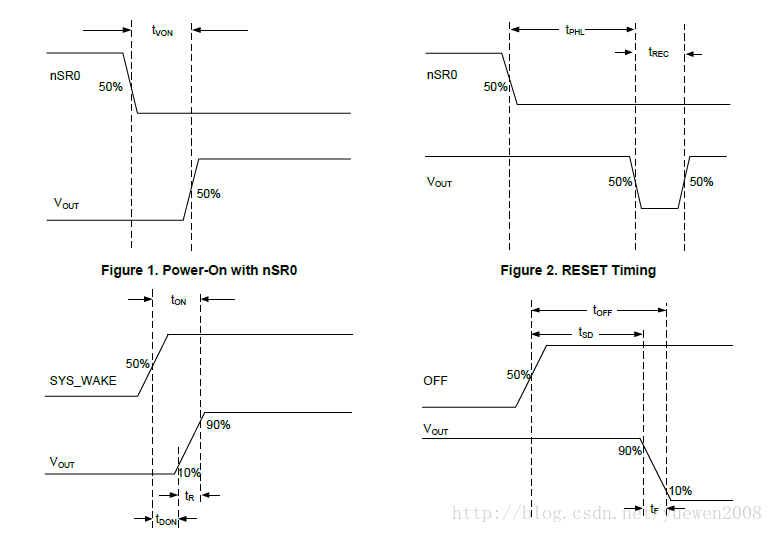

3、TIMING DIAGRAMS

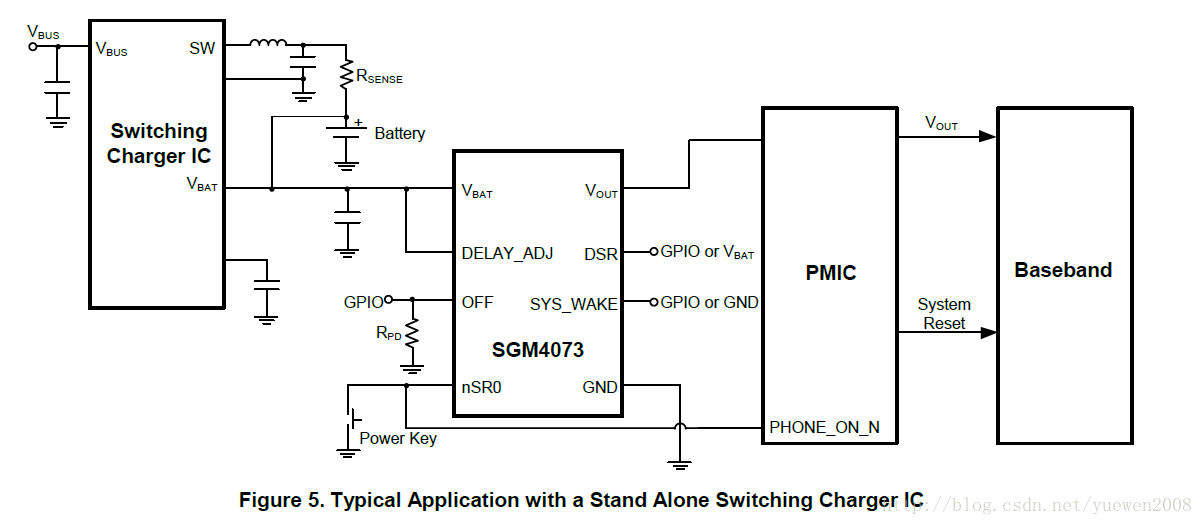

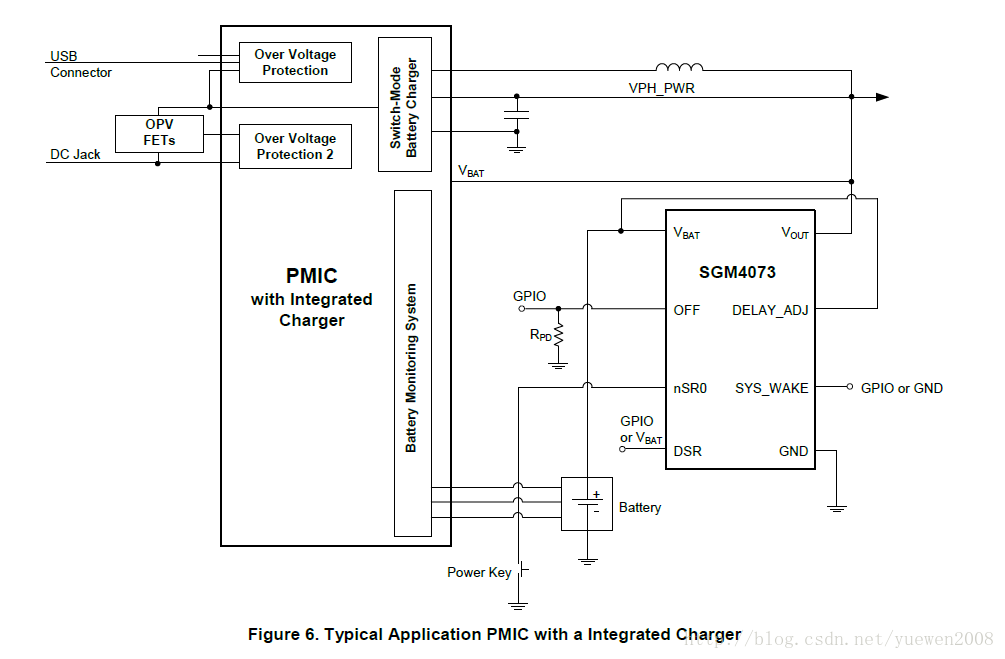

4、TYPICAL APPLICATION CIRCUITS

5、APPLICATION INFORMATION

Power-On

There are two methods to turn on the load switch to wake up the PMIC. When a HIGH is applied to the SYS_WAKE pin or when nSR0 is held LOW for > 1.9s (see Figure 1), the SGM4073 turns on its load switch to allow PMIC to connect to the battery. The reset feature is disabled when VOUT is toggled from OFF to ON. Continuously holding nSR0 LOW does not trigger a reset event.

有两种方式可以唤醒PMIC,一个是在SYS_WAKE上施加一个高电平或者是nSR0保持低电平至少1.9s。

Reset Timer

During normal operation of a mobile device, if a reset operation is needed for mobile equipment, holding the power switch, to which nSR0 is connected and is forced LOW, for at least 7.7s, causes the SGM4073 to cut off the supply power to PMIC for 468ms by turning off the load switch. If after 468ms, VOUT is less than VDIS (0.4V), the SGM4073 then automatically turns on the load switch to reconnect the PMIC to battery. If after 468ms, VOUT is larger than VDIS (0.4V), the SGM4073 will not turn on the load switch to reconnect the PMIC to battery until VOUT is less than VDIS. This forces PMIC to enter a power-on sequence.

如果移动终端设置需要复位操作长按连接到Nsr0的poweykey 7.7s将会断电。如果468毫秒后Vout小于0.4V ,SGM4073将会自动打开负载开关以重新连接PMIC和电池。

Disconnect PMIC from Battery (Turn-Off)

After holding the DSR pin HIGH, changing the OFF pin from LOW to HIGH (rising edge triggered) and holding it HIGH for at least 2ms, the SGM4073 triggers an internal counter to allow a factory-customized 7.7s delay before turning off internal load switch. The delay is intended to allow the PMIC to complete a power-down sequence before safely disconnected from the power supply. However, the turn-off sequence is terminated if a higher priority input is detected in tSD period (see Resolving Input Conflicts section). 保持DSR为高电平,off脚从低电平到高电平(上升沿触发),并保持至少2ms,SGM4073会触发内部计数器允许一个7.7s延时之后关闭内部负载开关,即断开电池和PMIC之间的供电。

Alternatively, after holding the DSR pin LOW, changing the OFF pin from LOW to HIGH (rising edge triggered) and holding it HIGH for at least 2ms, the SGM4073 triggers the zero-second turn-off. Delay tSD is significantly reduced to 2ms to avoid the default delay time to turn off load switch.

With its low shutdown current, the SGM4073 significantly reduces the current drain on a battery when the PMIC is turned off. In other words, it preserves the battery power for a longer period when a mobile device is in shutdown mode.

同样的如果DSR为低电平,off脚从低电平到高电平(上升沿触发),并保持至少2ms,SGM4073会触发一个0秒延时的关闭动作。

Zero-Second Factory-Test Mode

SGM4073 includes a Zero-Second Factory Test Mode to shorten the turn-on time for VOUT (tVON) and timer delay before reset (tPHL) for factory testing.

When VOUT is OFF, the default turn-on time (tVON) is 1.9s. If the DSR pin is LOW prior to nSR0 going LOW, the SGM4073 bypasses the 1.9s delay and VOUT is changed from OFF to ON immediately.

Similarly, default reset delay (tPHL) is 7.7s. If VOUT is ON and the DSR pin is LOW prior to nSR0 going LOW, the SGM4073 enters Zero-Second Factory Test Mode and bypasses the default reset delay of 7.7s; VOUT is pulled from ON to OFF immediately. The reset pulse (tREC) remains at 468ms in Zero-Second Factory Test Mode.