1 数字IC(ASIC)设计流程:

规格定制、详细设计、HDL编码、仿真验证、逻辑综合(产生网表)、静态时序分析(STA)、形式验证(对比综合后网表与HDL设计功能是否一致)。之后包括布局布线(进行硬件模块和连线资源映射)等操作,最终生成验证后的版图文件用于流片。其中综合是划分IC设计前端和后端的界限。

2 MCU结构:

它是由CPU系统、程序存储器(ROM)、数据存储器(RAM)、各种I/O端口、基本功能单元(定时器/计数器等)组成。

3 SOC低功耗技术:

在各个设计层级上均有低功耗技术:

a.工艺级:降低电源供电电压和阈值电压。

b.电路级:降低总线电压摆幅。

c.门级:同样通过低电压实现低功耗技术。

d.RTL级:主要从减少不希望的跳变入手。

e.系统级:门控技术(控制和消除不必要的寄存器活动)和异步电路(电路只在需要时工作,消除全局时钟树功耗)。

4 MOS管基本概念:

MOS中文意思是金属氧化物半导体场效应管,由栅极(G)、漏级(D)、源级(S)组成。分为PMOS和NMOS两种类型,区别在于G级高电平时,N型管导通,P型管截止。两者往往是成对出现的,即CMOS。只要一只导通,另一只则不导通,现代单片机主要是采用CMOS工艺制成的。

5 FPGA内部结构及资源:

FPGA主要由可编程单元、可编程I/O单元及布线资源构成。

可编程逻辑单元(可配置逻辑单元,CLB)由两个SLICE构成,SLICE主要包括实现组合逻辑的LUT和实现时序逻辑的触发器。FPGA内部还包含专用存储单元BRAM,运算单元DSP Slice,及专用内嵌功能单元,如:PLL、Serdes等。

6 FPGA内部LUT实现组合逻辑的原理:

LUT相当于存放逻辑表达式对应真值表的RAM。软件将逻辑表达式所有可能结果列出后存放在RAM中,输入作为RAM地址,输出为逻辑运算结果。如使用LUT模拟二输入“与”逻辑。列出真值表:00 -- 0,01 -- 0,10 -- 0,11 -- 1。此时将00 01 10 11作为地址线,依次将结果0 0 0 1存放在RAM中。当输入00时及输出0&0=0.

7 常用逻辑表达式化简公式:

左右关系为*变+,+变*

交换律:A*B = B*A A+B = B+A

结合律:(A*B)*C = A*(B*C) (A+B)+C = A+(B+C)

分配率:A(B+C) = AB+AC A+BC = (A+B)(A+C)

特殊定律:

8 FIR滤波器与IIR滤波器函数表达式、特点及结构:

FIR(有限冲激响应)滤波器:非递归,具有线性相位。IIR(无限冲激响应)滤波器:递归结构,非线性相位。相同阶数FIR和IIR滤波器,IIR滤波器滤波效果较好,但会产生相位失真。

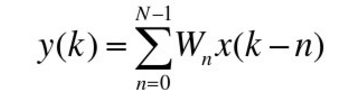

FIR滤波器:

对N个采样数据进行加权和平均处理。

表达式:

结构图:

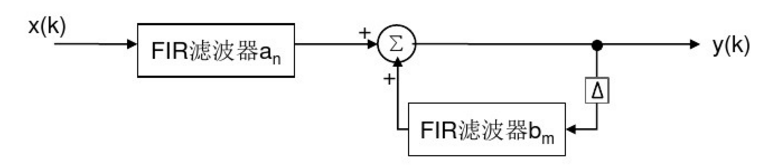

IIR滤波器:

包含递归部分也包含非递归部分。

表达式:(具有N个前馈系数和M-1个反馈系数)

结构图: