一.中央处理器(CPU)

1.1 CPU的构成与基本工作方式

一般的处理器由运算器、控制器、一系列寄存器以及高速缓存构成。

- 运算器

运算器实现任何指令中的算术和逻辑运算,是计算机计算的核心。 - 控制器

控制器负责控制程序运行的流程,包括取指令、维护CPU状态、CPU与内存的交互等。 - 寄存器

寄存器是指令在CPU内部作处理的过程中暂存数据、地址以及指令信息的存储设备,在计算机的存储系统中它具有最快的访问速度。 - 高速缓存

高速缓存处于CPU和物理内存之间,一般有控制器中的内存管理单元管理,它的访问速度快于内存,低于寄存器,它利用程序局部性原理使得高速指令处理和低速内存访问得以匹配,从而大大提高了CPU的效率。

1.处理器的寄存器

- 用户可见寄存器

对于高级语言来说,编译器通过一定的算法分配并使用这些寄存器,以最大限度地减少程序运行时访问主存储器的次数,这对程序的运行速度影响很大。 控制和状态寄存器

它们用于控制处理器的操作,一般由具有特权的操作系统代码使用以控制其他程序的执行。常见的控制和状态寄存器

- 程序计数器(PC:Program Counter),它记录了将要取出的指令的地址。

- 指令寄存器(IR:Instruction Register),包含了最近取出的指令。

- 程序状态字(PSW:Program Status Word),它记录了处理器的运行模式信息等,有的处理器中它还包含了条件码。

2.指令执行的基本过程

处理器先从存储器中每次读取一条指令。然后执行这条指令。一个这样的单条指令处理过程称为一个指令周期。程序的执行就是由不断取指令和执行指令的指令周期组成的。仅当机器关机、发生某些未发现的错误或者遇到停机相关的指令时,程序才会停止。

1.2 特权指令和非特权指令

- 特权指令

是指在指令系统中那些只能由操作系统使用的指令。

例如:启动I/O指令、设置时钟指令、控制中断屏蔽的某些指令、清主存指令、建立存储保护指令。 非特权指令

用户程序可以使用的指令。

例如:控制转移、算术运算、访管指令、取数指令。实例 :X86系列处理器

X86支持4个处理器特权级别,特权环:R0、R1、R2、R3- 从 R0 到 R3,特权能力由高到低

- R0 属于内核态,R3属于用户态,R1 和 R2 则介于两者之间

- 不同级别 能够运行的指令集合不同

1.3 处理器的状态

1. 操作系统需要两种CPU状态

- 内核态(Kernel Model)、系统态、管态

运行操作系统程序 - 用户态 (User Model)、目态

运行用户程序

2. CPU 状态之间的转换

- 用户态 –> 内核态

唯一途径 : 中断/异常/陷入机制 内核态 –> 用户态

设置程序状态字PSW陷入指令 又称:访管指令

提供给用户程序的接口,用于调用操作系统的功能(服务)

例如 :int , trap , syscall , sysenter , sysexit

3.限制用户程序执行特权指令

1.4程序状态字PSW

作用 : 指示处理器状态

处理器的程序状态字(PSW)通常包括以下状态代码

- CPU的工作状态码

指明管态与目态 - 条件码

反映指令执行后的结果特征 - 中断屏蔽码

指出是否允许中断

二.存储体系

2.1存储器的层次结构

1.容量、速度和成本的匹配

2.存储访问局部性原理

2.2存储保护

1.界地址寄存器(界限寄存器)

2.存储键

三.中断与异常机制

2.1 中断与异常的作用

操作系统是 中断驱动 或者 事件驱动 的

主要作用

- 及时处理设备发来的中断请求

- 可使OS捕获用户程序提出的服务请求

- 防止用户程序执行过程中的破坏性活动

2.2 中断与异常的概念

CPU对系统发生的某个事件作出的一种反应

CPU暂停正在执行的程序,保留现场后自动转去执行相应事件的处理程序,处理完成后返回断点,继续执行被打断的程序。

事件的发生改变了处理的控制流

中断 :外部事件,正在运行的程序所不期望的

异常 :由正在执行的指令引发

2.3 中断与异常的特点

- 是随机发生的

- 是自动处理的

- 是可恢复的

2.4 中断与异常的背景历史

中断的引入 :为了支持CPU与设备之间的并行操作

当CPU启动设备进行输入/输出后,设备便可以独立工作,CPU转去处理与此次输入/输出不相关的事情;

当设备完成输入/输出后,通过向CPU发中断报告此次输入/输出的结果,让CPU决定如何处理以后的事情

异常的引入 :表示CPU执行指令时本身出现的问题

如算术溢出、除零、取数时的奇偶错,访存地址时越界或执行了“陷入指令”等,

这事硬件改变了CPU当前的执行流程,转到相应的错误处理程序或异常处理程序或执行系统调用

三.中断/异常机制工作原理

3.1 软硬件分工:

硬件

中断/异常响应: 捕获中断源发出的中断/异常请求,以一定方式响应,将处理器控制权交给特定的处理程序。软件

中断/异常处理程序: 识别中断/异常类型并完成相应的处理。

软件提前设置好,硬件部件来执行

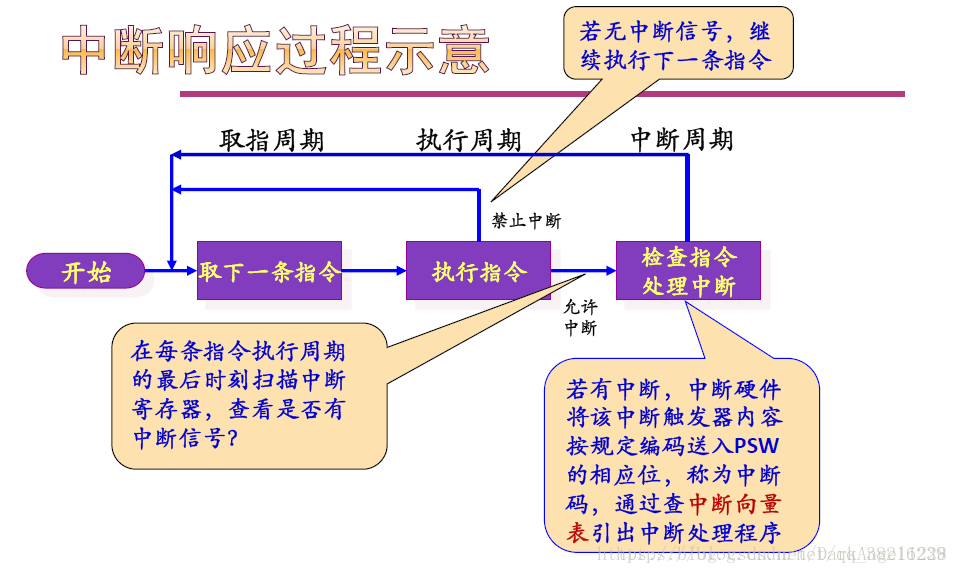

3.2 中断响应过程:

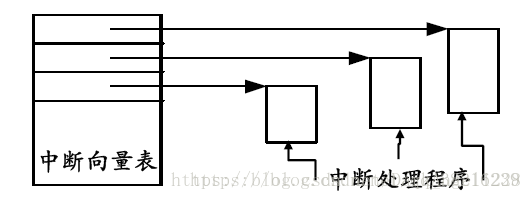

(中断向量:一个内存单元,存放中断处理程序入口地址和程序运行时所需的处理机状态字)

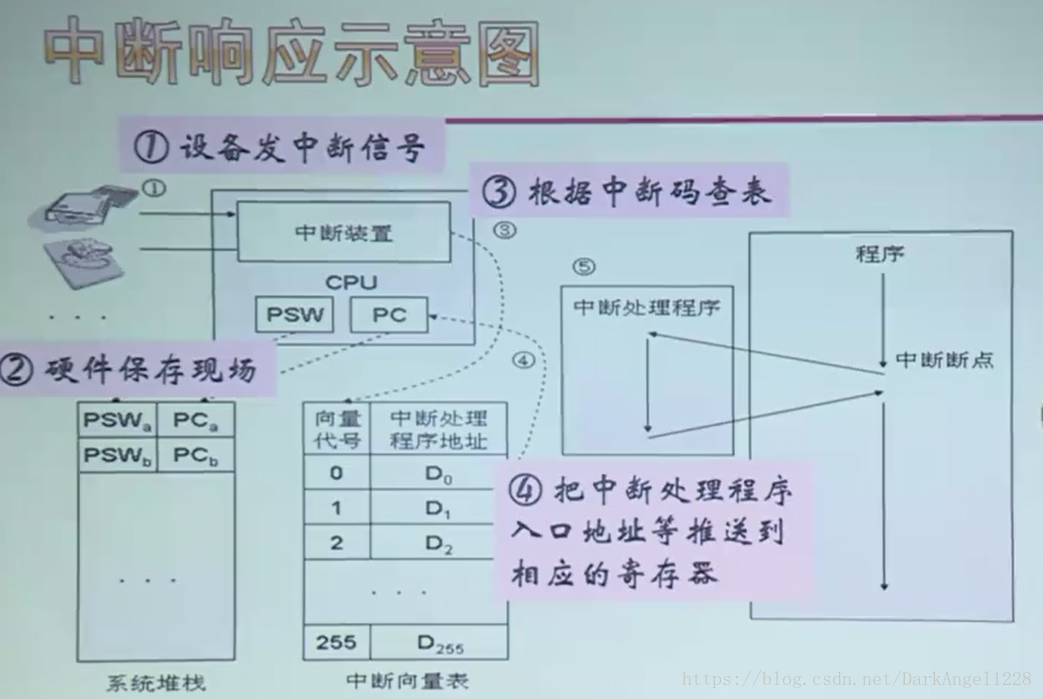

中断响应步骤:

① 设备发中断信号。

② 硬件保存现场(PC、PSW的内容)。

③ 根据中断码查表。

④ 把中断处理程序入口地址等推送到相应的寄存器。

⑤执行中断处理程序。

3.3 中断处理程序:

设计操作系统时,为每一类中断/异常事件编好相应的处理程序,并设置好中断向量表:

中断处理程序步骤:

①保存相关寄存器信息。

②分析中断/异常的具体原因。

③执行对应的处理功能。

④恢复现场,返回被事件打断的程序。

3.4 实例:

- 打印机给CPU发中断信号。

- CPU处理完当前指令后检测到中断,判断出中断来源并向相关设备发确认信号。

- CPU开始为软件处理中断做准备:

- 处理器状态被切换到内核态。

- 在系统栈中保存被中断程序的重要上下文环境,主要是程序计数器PC、程序状态字PSW。

CPU根据中断码查中断向量表,获得与该中断相关的处理程序的入口地址,并将PC设置成该地址,新的指令周期开始时,CPU控制转移到中断处理程序。

中断处理程序开始工作 :

- 在系统栈中保存现场信息 。

- 检查I/O设备的状态信息,操纵I/O设备或者在设备和内存之间传送数据等等

中断处理结束时,CPU检测到中断返回指令,从系统栈中恢复被中断程序的上下文环境,CPU状态恢复成原来的状态,PSW和PC恢复成中断前的值,CPU开始一个新的指令周期。

举例 : I/O中断处理程序

- I/O操作正常结束

- 若有程序正在等待此次I/O的结果,则应将其唤醒

- 若要继续I/O操作,需要准备好数据重新启动I/O

- I/O操作出现错误

- 需要重新执行失败的I/O操作

- 重试次数有上限,达到时系统将判定硬件故障

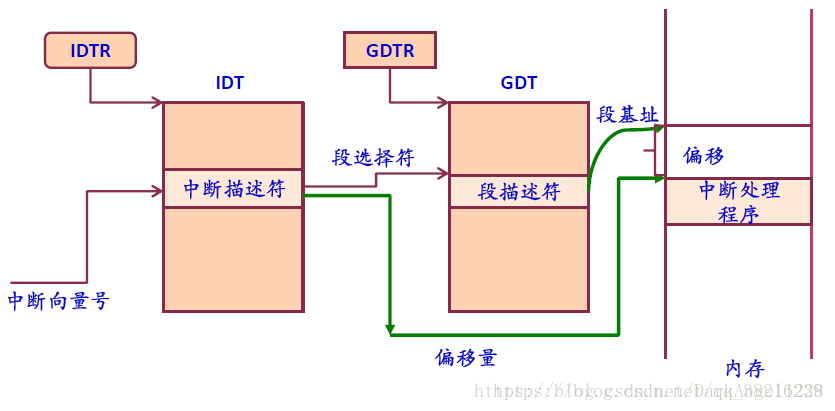

3.5 x86处理器对中断的支持:

中断描述符表 (Interrupt Descriptor Table):采用门(gate) 描述符数据结构表示中断向量。

全局描述符表(Global Descriptor Table):在整个系统中,全局描述符表GDT只有一张(一个处理器对应一个GDT),GDT可以被放在内存的任何位置,但CPU必须知道GDT的入口,也就是基地址放在哪里,Intel的设计者门提供了一个寄存器GDTR用来存放GDT的入口地址。

四.系统调用

系统调用 :用户在编程时可以调用的操作系统功能

系统调用时操作系统提供给编程人员的唯一接口,使CPU状态从用户态陷入内核态

每个操作系统都提供了几百种系统调用 : 进程控制、进程通信、文件使用、目录操作、设备管理、信息维护等等

4.1 系统调用的执行过程

当CPU执行到特殊的陷入指令时 :

- 中断/异常机制 :

硬件保护现场 :通过查中断向量表,把控制权转给系统调用总入口程序 - 系统调用总入口程序:

保护现场 : 将参数保存在内核的堆栈里,通过查系统调用表把控制权转给响应的系统调用处理程序或内核函数 - 执行系统调用例程

- 恢复现场,返回用户程序