ARM920T的7种工作模式

(1)usr:正常模式

(2)sys:系统

(3)异常模式

- und:未定义模式

- svc:管理模式

- abt:中止模式:

- 指令预取

- 数据访问

- irq:中断模式

- fiq:快中断模式

2种状态

(1)ARM指令集

每条指令占用4字节

(2)thumb指令集

每条指令占用2字节

比如指令 mov r0, r1使用不同指令集编译后,每条指令占用的空间大小不同

- ARM:4byte机器码

- THUMB:2byte机器码

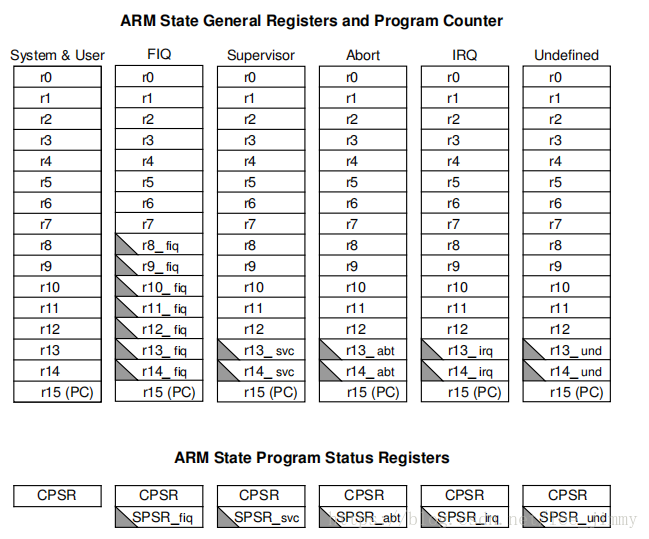

寄存器

(1)我们可以看到在异常情况下的寄存器有些事带有灰色的三角,表明在这几种异常模式下,这几个寄存器是有别的用处

其中r13还是我们常说的sp寄存器;r14就是lr寄存器,保存放回的地址

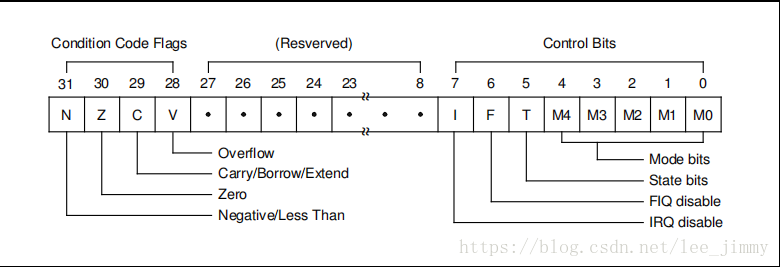

(2)下面是当前状态寄存器(CPSR)每一位的含义

(3)而异常模式下还有一个SPSR,就是用来保存用户模式下的CPSR的值

ARM手册上的简单异常处理流程描述

Action on Entering an Exception(进入异常模式的几个动作)While handling an exception, the ARM920T does following activities:

1. Preserves the address of the next instruction in the appropriate Link Register(LR_异常 = 下一个PC+4或者+8). If the exception has been

entered from ARM state, then the address of the next instruction is copied into the Link Register (that is,

current PC + 4 or PC + 8 depending on the exception. See Table 2-2 on for details). If the exception has been

entered from THUMB state, then the value written into the Link Register is the current PC offset by a value

such that the program resumes from the correct place on return from the exception. This means that the

exception handler need not determine which state the exception was entered from. For example, in the case of

SWI, MOVS PC, R14_svc will always return to the next instruction regardless of whether the SWI was

executed in ARM or THUMB state.

2. Copies the CPSR into the appropriate SPSR

3. Forces the CPSR mode bits to a value which depends on the exception

4. Forces the PC to fetch the next instruction from the relevant exception vector

It may also set the interrupt disable flags to prevent otherwise unmanageable nestings of exceptions.

If the processor is in THUMB state when an exception occurs, it will automatically switch into ARM state when the

PC is loaded with the exception vector address.

On completion, the exception handler:

1. Moves the Link Register, minus an offset where appropriate, to the PC. (The offset will vary depending on the

type of exception.)

2. Copies the SPSR back to the CPSR

3. Clears the interrupt disable flags, if they were set on entry