I/O接口标准

1.单端信号接口标准

LVTTL和LVCMOS(JESD8-5,JESD8-B)

SSTL(JESD8-8,JESD8-9B,JESD8-15)

HSTL(JESD8-6)

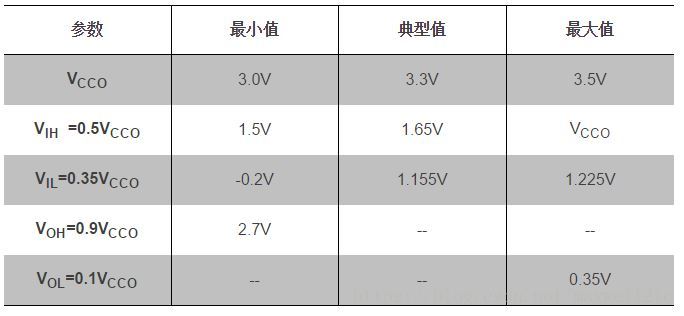

LVTTL和LVCMOS结构通常是简单的push-pull。最简单的例子就是CMOS反向器,需要满足的唯一参数是VIL/VIH,VOL/VOH以及驱动电流,接口标准相对易于实现。其输入和输出参数见下面的表格。随着VDD范围的不同,参数有所不同。

SSTL(Stub Series TerminatedLogic)有三种:SSTL_18,SSTL_2,SSTL_3。SSTL不同于LVTTL和LVCMOS的一个重要方面是SSTL要求传输线终端匹配。所以,SSTL有输出阻抗参数以及不同的终端匹配方法。这个差异对高速信号来说是非常重要的,因为合适的的终端匹配可以减少反射减少EMI并改善稳定速度提高定时裕度。LVTTL和LVCMOS信号也可以进行终端匹配,但是因为这个要求并没有清晰地在参数中说明,对于终端匹配电阻对信号摆动的影响用户需要仔细调整。

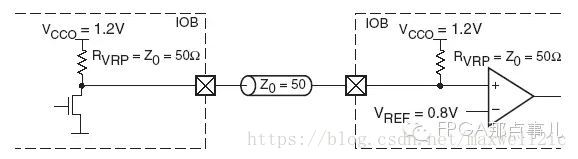

SSTL与LVTTL驱动器没有太多的不同,但是输入缓冲却非常不同。SSTL输入是查分对,因此输入级提供较好的电压增益以及较稳定的阈值电压,这使得对小的输入电压摆幅具有比较高的可靠性。如图1所示。

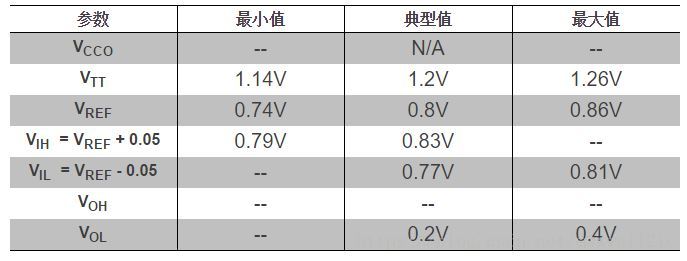

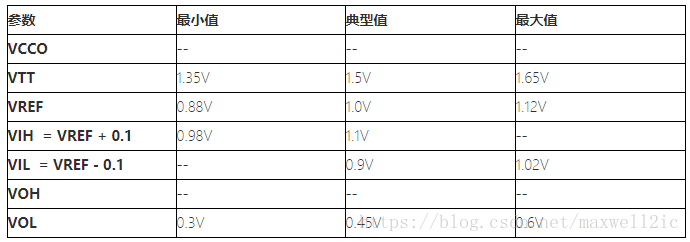

下面的表是关于SSTL的电源和输入参数,注意,SSTL对于不同类型的驱动器有不同的参数。SSTL_3和SSTL_2定义2类驱动器,以区别不同的终端匹配方案。SSTL_18没有明确的类型定义,但是,取决于终端环境,驱动器必须能够在输入缓冲处产生相应的电压摆幅。建议用户参考相关标准。

AC参数指的是一个阈值电压,当信号跨越这个阈值电压时,接收器状态一定会发生改变。只要输入保持在定义的DC阈值之上,接收器将维持逻辑状态不变。这有利于系统设计者对整个系统性能进行优化。

HSTL(High-SpeedTransceiver Logic)是另外一个标准,与SSTL一样,HSTL输入级使用差分放大器,类似于SSTL,HSTL有输出电压和器件电压,允许这两个电压不同。

2.差分信号接口标准

CML(Current-mode llogic)它并没有一个标准,是基于简单的差分放大器,如图2所示。通常取R1=R2=50欧姆,|VOUT+ - VOUT-| = R1 * i1 = 50*i1,不同的厂家i1值不一样,所以,电压摆幅不同的厂家也不一样。不同厂家电阻也不一样,不可能是高性能高速器件,另一个因素是共模电压,这对直流耦合是非常重要的,用户必须保证发送器和接收器共模电压相匹配,如果是AC耦合,则共模电压不是问题。

PECL(positive-emitter coupled logic)和LVPECL(low-voltagePECL),基本结构如图3所示。输入缓冲与CML一样,输出增加了一个共源放大器。输出是开源级。用户需要在外部增加对地电阻形成输出信号。与CML一样,PECL和LVPECL没有一个标准,不同的厂家输出电压摆幅都不一样,输出电压摆幅不仅取决于外部电阻,还与共源放大器的门级电压有关系。与CML类似,PECL和LVPECL需要用户考虑共模电压、电压摆幅、互换性等。与CML相比,由于多了个共源放大器,所以,具有比CML低的输出阻抗,所以可以驱动更重的负载,使用外部电阻或许是个优点,使得用户可以控制输出摆幅、功耗、终端匹配等。

LVDS(low-voltage differential signaling),电路基本结构如图4所示。LVDS是有标准的(TIA/EAI-644)。在VOUT+和VOUT-之间的负载电阻一般为100欧姆。一般使用DC耦合。

Xilinx FPGA的I/O兼容多种电平标准,包括LVTTL、LVCMOS、LVDS、LVPECL等,下面对各类电平标准做简要介绍。

一、LVTTL(LowVoltage Transistor-Transistor Logic)

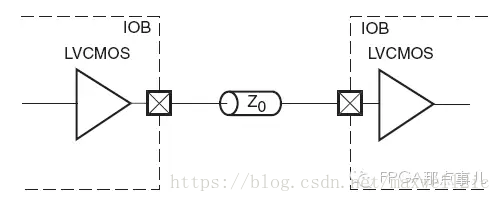

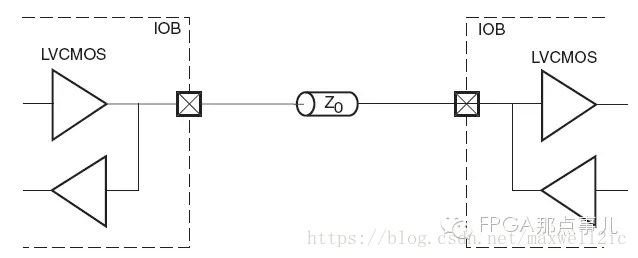

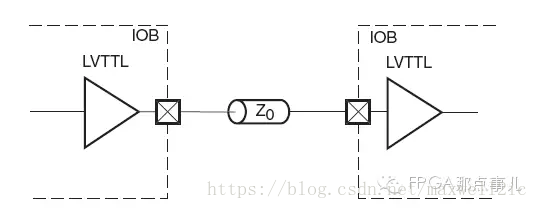

LVTTL电平标准即低电压三极管-三极管逻辑电平标准是EIA/JESDSA的一种通用的3.3V电平标准,该标准的输入输出供电电压(VCCO)为3.3V,不需要参考电压(VREF)和终端电压(VTT)。LVTTL电平标准终端连接示意图如下所示,包括单向的和双向的终端链接方式。

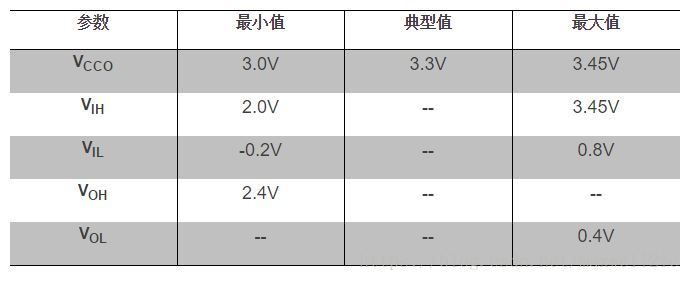

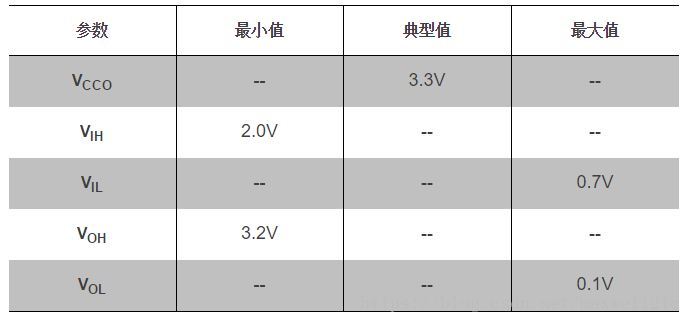

LVTTL电平标准的具体参数如下表所示。

二、LVCMOS(LowVoltage Complementary Metal Oxide Semiconductor)

LVCMOS电平标准即低压互补金属氧化物半导体电平标准是JEDEC(JESD8-5)的一种通用电平标准,该标准在V5系列FPGA中包括LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25和LVCMOS33。LVCMOS电平标准终端连接示意图如下所示,包括单向的和双向的终端链接方式。

常用的LVCMOS电平标准为LVCMOS33和LVCMOS25。

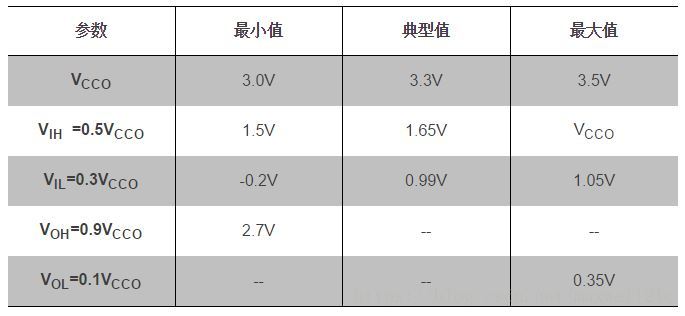

LVCMOS33电平标准的具体参数如下表所示。

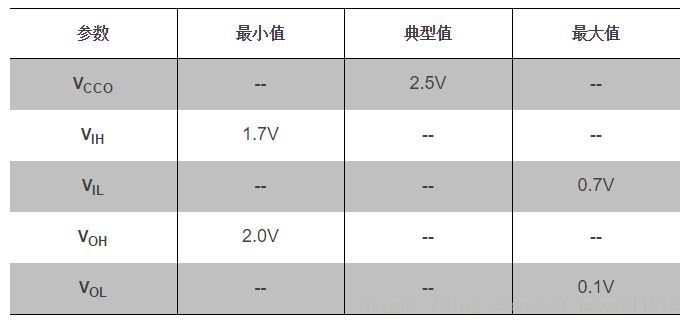

LVCMOS25电平标准的具体参数如下表所示。

三、PCI(PeripheralComponent Interconnect)

PCI电平标准即外设器件互联电平标准,该标准支持33MHz和66MHz的总线应用,包括PCI-X、PCI-33、PCI-66等各类电平标准,该标准的输入输出供电电压(VCCO)为3.3V,不需要参考电压(VREF)和终端电压(VTT)。

PCI33_3和PCI66_3电平标准的具体参数如下表所示。

PCI-X直流电平标准的具体参数如下表所示。

四、GTL(GunningTransceiver Logic)

GTL电平标准即冈宁收发器逻辑电平标准,是Xerox发明的一种高速总线电平标准,该标准需要差分放大输入buffer和漏极开路(高阻)输出buffer。不连接VCCO的电路连接方式如下图所示。

GTL标准不需要VCCO,但GTL_DCI标准需要连接1.2V的VCCO。其电路连接方式如下图所示。

GTL电平标准的具体参数如下表所示。

五、GTLP(GunningTransceiver Logic Plus)

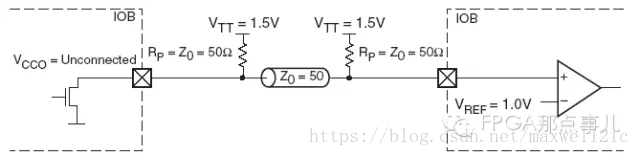

GTL+电平标准即冈宁收发器逻辑电平标准加,是在Pentium Pro处理器中首先使用的一种高速总线电平标准,该标准需要差分放大输入buffer和漏极开路(高阻)输出buffer。差分负端的输入buffer要连接VREF电平。GTL+标准电路连接方式如下图所示。

GTL+标准不需要VCCO,但GTLP_DCI标准需要连接1.5V的VCCO。其电路连接方式如下图所示。

GTLP电平标准的具体参数如下表所示。

六、HSTL(High-SpeedTransceiver Logic)

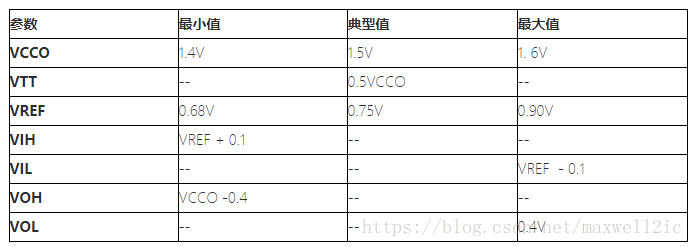

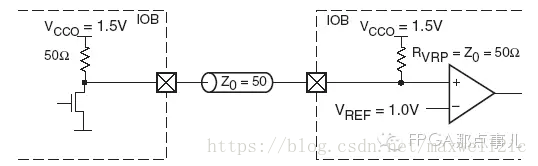

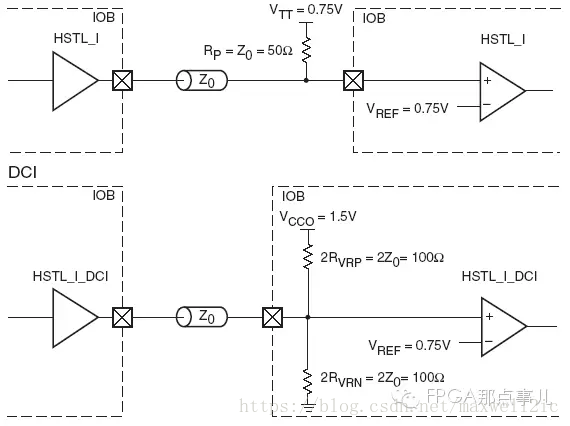

HSTL电平标准即高速收发器逻辑电平标准,是一种通用目的的高速总线电平标准,由IBM首先提出,包括HSTL_I、HSTL_II、HSTL_III、HSTL_IV、DIFF_HSTL_I、DIFF_HSTL_II、DIFF_HSTL_III、DIFF_HSTL_IV等诸多版本。其1.5V和1.8V的标准有四个等级,Xilinx V5系列支持所有等级的1.5V和1.8V的标准,并支持差分版本的等级I和等级II。

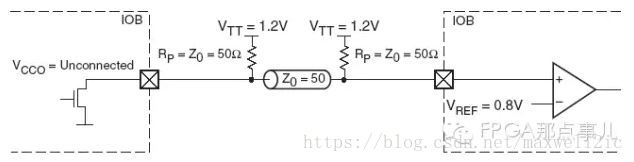

HSTL Class I电平标准电路连接方式如下图所示。

HSTLClass I电平标准的具体参数如下表所示。