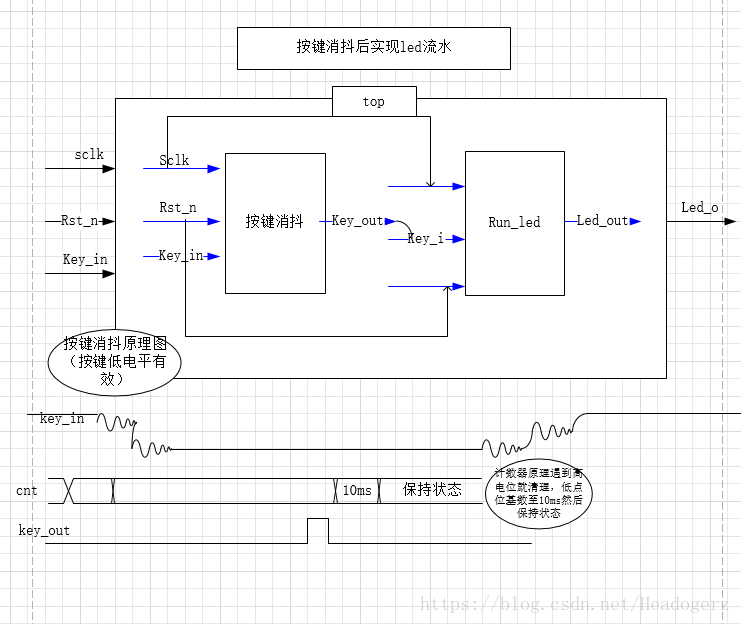

第一步,依旧上原理图

第二部,编译代码,以及测试文件

module key_out(

input wire sclk,

input wire rst_n,

input wire key_in,

output reg key_out

);

reg [18:0]cnt;

parameter CNT_MAX=500000-1; //这里边的数据是对的时钟周期,而1个时钟周期为20ns延时10ms足够

always@(posedge sclk or negedge rst_n)

if(rst_n==0)

cnt<=19'b0;

else if (key_in==1)

cnt<=19'b0;

else if(cnt==CNT_MAX)

cnt<=cnt;

else

cnt<=cnt+1'b1;

always@(posedge sclk or negedge rst_n)

if(!rst_n)

key_out<=1'b0;

else if (cnt==CNT_MAX-1)

key_out<=1'b1;

else

key_out<=1'b0;

endmodulemodule run_led(

input wire sclk,

input wire rst_n,

input wire key_o,

output reg [3:0] led

);

always@(posedge sclk or negedge rst_n)

if(!rst_n)

led<=4'b0001;

else if(key_o==1)

led<={led[2:0],led[3]};

endmodule`timescale 1ns/1ns

module tb_o();

reg sclk;

reg rst_n;

reg key_in;

wire key_out;

initial

begin

sclk=0;

rst_n<=0;

key_in<=0;

#20

rst_n<=1;

key_in<=1;

#200

key_in<=0;

#2000

key_in<=1;

#500

key_in<=0;

#200

key_in<=1;

#200

key_in<=0;

#10000000

key_in<=1;

end

always # 10 sclk=~sclk;

key_out key_out_inst(

.sclk (sclk ),

.rst_n (rst_n ),

.key_in (key_in ),

.key_out (key_out)

);

endmodule第三步,modulesim仿真

补充说明,测试文件的#200延时是对于上一状态。仿真的信号分别是时钟、复位、输入按键、计数器、开关有效时钟周期。很多知识点还不是很理解。计数器要在输入按键处于高电平的时候清零,记到10ms的时候保持。