cache是干啥的?

在以前,CPU的主频比较慢,CPU和内存DRAM之间速度差别不是很大,存储数据或者指令还OK。但是CPU的飞速发展,CPU大哥速度已经飞快,而内存速度却跟不上大哥的步伐,所以大哥每次要读取或者写入内存的时候都要等一等小弟,这个时候怎么办。cache就出来了,它类似与一个第三方。位于内存和CPU之间,速度非常快,所以CPU就把数据直接写入cache,然后CPU就可以干其他的了,剩下的事情就交给cache这个跑腿的,cache在合适的时机可以慢慢的把数据写入内存,也就是相当于解了CPU的燃眉之急。

说白了,CPU要读数据首先是在cache中读,如果cache命中,也叫cache hit,CPU就可以极快的得到该地址处的值。如果cache miss 也就是没有命中,它就会通过总线在内存中去读,并把连续的一块单元加载到cache中,下次好使用。

cache大多是SRAM(静态RAM),而内存大多是DRAM(动态随即存储)或者DDR(双倍动态随机存储)。

cache容量一般非常小,因为价格贵,所以cache小是有道理的。一级cache一般就几KB,cache 的单位又分成cache line ,它是从内存单元加载到cache中的最小单元,一般为几个字大小,32字节或者64字节偏多。(因为时间局部性和空间局部性所以加载一次是以一个cache单元为最小单位)

cache有两种模式(写回模式) 和 (写通模式)

写回?写通? 回哪儿?通哪儿?

当然是内存啊!!!

简单介绍,写通也就是当CPU写入cache的时候,将数据再从cache 中写到内存中,这两个过程要都结束后,CPU的写入操作才算完成,也就是时刻保持内存和缓存的同步,这显然是很耗时的。

什么是多级cache?

一级cache 有指令cache和数据cache之分,这使整个系统更加高效,因为1Lcache 容量小,所以有了多级cache ,比如二级cache ,他容量大,但是速度就要比1Lcache 慢些,但比内存快多了。三级cache就更一些了。

写回也就是当CPU写入cache中的时候,数据不会马上从cache中写到内存里面,而是等待时机成熟后写入(比如 发生cache miss,其他内存要占用该cache line的时候将该单元写回到内存中,或者一定周期后写入到内存中 ,或者其它地核需要读取该内存的时候)。

内存写入cache的时候,如果cache 满了,则用一定的算法淘汰,比如随机淘汰还有或者LRU淘汰(用的少的被淘汰 常用)来替换掉原来的cache line 单元。

缓存(cache)大小是CPU的重要指标之一,其结构与大小对CPU速度的影响非常大。简单地讲,缓存就是用来存储一些常用或即将用到的数据或指令,当需要这些数据或指令的时候直接从缓存中读取,这样比到内存甚至硬盘中读取要快得多,能够大幅度提升cpu的处理速度。

CPU与cache之间的数据交换是以”字”为单位,而cache与主存之间的数据交换是以”块”为单位,一个块由若干字组成,是定长的,以体现”保存下级存储器刚才被存取过的数据及其邻近小范围的数据”这一概念。

CPU进行存储器读操作时,根据主存地址可分成命中和未命中两种情况。对于前者,从Cache中可直接读到所需的数据;对于后者,需访问主存,并将访问单元所在的整个块从内存中全部调入Cache,接着要修改Cache标记。若Cache已满,需按一定的替换算法,替换掉一个旧块。

一级缓存中还分数据缓存(data cache,d-cache)和指令缓存(instruction cache,i-cache)。二者分别用来存放数据和执行这些数据的指令,而且两者可以同时被cpu访问,减少了争用cache所造成的冲突,提高了处理器效能。

采用分立Cache技术,也就是将指令和数据分开,分别存放在指令Cache 和数据Cache中。这种分立Cache技术有利于CPU采用流水线方式执行指令。在流水线中,往往会发生在同一个操作周期同时需要预取一条指令和执行另一条指令的取数据操作的情况。若采用指令和数据统一的Cache,则这种情况会造成取指令和取数据的访存冲突,冲突的结果就是使得流水线产生断流的情况发生,从而严重影响流水线的效率。采用分立Cache技术,因为取指令和取数据分别在不同的Cache中同时进行,因而不会产生冲突,有利于流水线的实现

二级缓存(L2 CACHE)出现是为了协调一级缓存与内存之间的速度。最初缓存只有一级,后来处理器速度又提升了,一级缓存不够用了,于是就添加了二级缓存。二级缓存是比一级缓存速度更慢,容量更大的内存,主要就是做一级缓存和内存之间数据临时交换的地方用。“L1级Cache-L2级Cache-主存”这种层次从工作原理上讲与前述的Cache工作原理是完全相同的,即CPU首先访L1级Cache,若不命中,再访问L2级Cache和主存。

Cache/主存系统的读操作原理:

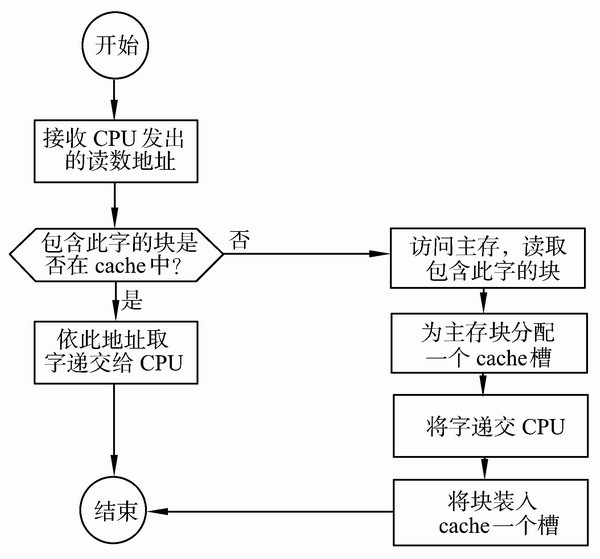

当CPU试图读取主存一个字时,发出此字内存地址同时到达cache和主存,此时cache控制逻辑依据地址的标记部分进行判断此字当前是否在cache中。若是(命中),此字立即递交给CPU,若否(未命中),则要用主存读取周期把这个字从主存读出送到CPU,与此同时把含有这个字的整个数据块从主存读出送到cache中。由于程序的存储器访问具有局部性,当为满足一次访问需求而取来一个数据块时,下面的多次访问很可能是读取此块中的其它字。

图1 Cache/主存系统的读操作原理

图2 cache的读操作流程示意

cache是干啥的?

在以前,CPU的主频比较慢,CPU和内存DRAM之间速度差别不是很大,存储数据或者指令还OK。但是CPU的飞速发展,CPU大哥速度已经飞快,而内存速度却跟不上大哥的步伐,所以大哥每次要读取或者写入内存的时候都要等一等小弟,这个时候怎么办。cache就出来了,它类似与一个第三方。位于内存和CPU之间,速度非常快,所以CPU就把数据直接写入cache,然后CPU就可以干其他的了,剩下的事情就交给cache这个跑腿的,cache在合适的时机可以慢慢的把数据写入内存,也就是相当于解了CPU的燃眉之急。