2.3 有限字长效应

2.3.1 字长效应的产生因素

数字信号处理的实质是一组数值运算,这些运算可以在通用数字计算机上用软件实现,

也可以用专门的硬件实现。无论采用哪种实现方式,数字信号处理系统的一些系数、信号

序列的各个数值及运算结果等都要以二进制形式存储在有限长的存储单元中。如果处理的

是模拟信号,例如常用的采样信号处理系统,输入的模拟量经过采样和模/数转换后,变成

有限字长的数字信号,有限字长的数就是有限精度的数。因此,具体实现中往往难以完全

保证原设计精度,从而产生误差,甚至导致错误的结果。在数字系统中主要有以下三种因

有限字长而引起误差的因素。

模/数(A/D)转换器把模拟输入信号转换成一组离散电平时产生的量化效应。

把系数用有限位二进制数表示时产生的量化效应。

在数字运算过程中,为限制字长进行的尾数处理和为防止溢出而压缩信号电平的有限字长效应。

引起这些误差的根本原因在于寄存器(存储单元)的字长有限。误差的特性与系统的类型、结构形式、数字的表示法、运算方式及字长有关。在通用计算机上,字长较长,量化步长很小,量化误差不大,因此用通用计算机实现数字系统时,一般可以不考虑有限字长的影响。但使用专用硬件,如 FPGA 实现数字系统时,其字长较短,就必须考虑有限字长效应了。

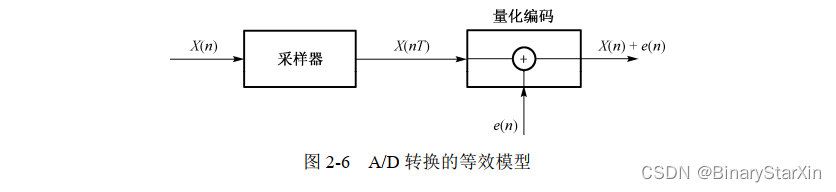

2.3.2 A/D 转换的字长效应

从功能上讲, A/D 转换器可简单分为采样和量化两部分。采样将模拟信号变成离散信号,量化将每个采样值用有限字长表示。采样频率的选取直接影响 A/D 转换的性能,根据奈奎斯特定理,采样频率至少需要大于等于信号最高频率的两倍,才能够从采样后的离散信号中恢复原始的模拟信号,且采样频率越高, A/D 性能越好。量化效应可以等效为输入信号为有限字长的数字信号,其统计意义上的等价结构如图 2-6 所示。

从式(2-11)可以看出,舍入后的字长每增加 1 位, SNR 约增加 6 dB。那么,在数字

信号处理系统中是否选取字长越长越好呢?其实选取 A/D 转换的字长主要考虑两个因素:输入信号本身的信噪比,以及系统实现的复杂度。由于输入信号本身有一定的信噪比,字长增加到一定长度时,当 A/D 转换器量化噪声比输入信号的噪声电平更低时,再增加字长就没有意义了;随着 A/D 字长的增加,数字系统实现的复杂程度也会急剧增加,特别是对于采用 FPGA 等硬件平台实现的数字系统,这一问题显得尤其突出。文献[16]、 [17]对量化噪声相关问题进行了详细的讨论, 文献[16]对 A/D 量化字长对不同系统的解调性能影响进行了详细分析及仿真。

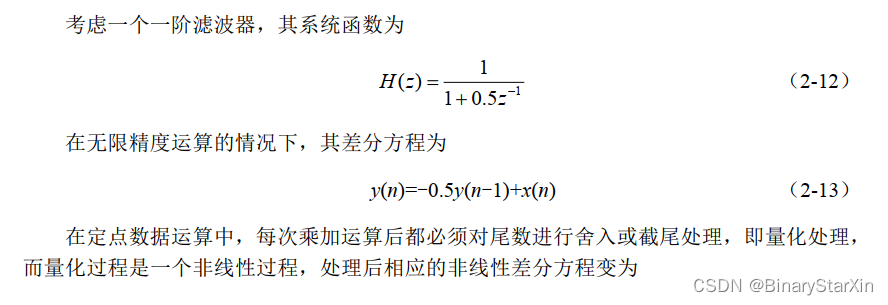

2.3.3 系统运算中的字长效应

对于二进制运算来讲,定点数的加法运算虽然不会改变字长,但存在数据溢出的可能,因此需要考虑数据的动态范围。定点数的乘法运算显然存在字长效应,因为 2 个 B 位字长的定点数据相乘,要保留所有有效位需要使用 2B 位字长的数据,数据截尾或舍入必定会引起字长效应。在浮点数运算中,乘法或加法运算均有可能引起尾数位的增加,因此也存在字长效应。一些读者可能会问:为什么不能增加字长来保证运算过程不产生截尾或舍入操作呢?这样虽然需要增加一些寄存器资源,但毕竟可以避免因截尾或舍入而带来的运算精度下降甚至运算错误吧!对于没有反馈的系统,这样理解也未尝不可。对于数字滤波器或较为复杂的电路系统来讲,通常会需要具有反馈网络的结构,这样每一次闭环运算均增加一部分字长,循环运算下去势必要求越来越多的寄存器资源,字长的增加是单调增加的,也就是说随着运算的持续,所需寄存器资源是无限增加的。采用这样的方法来实现一个系统,显然是不现实的。

| 例 2-2 MATLAB 仿真运算中的字长效应 |

用 MATLAB 软件仿真式( 2-14)所表示的一阶数字滤波器输入信号响应结果,输入信

号为冲激信号 7δ(n)/8。仿真原系统、 2 bit、 4 bit、 6 bit 量化情况下的输出响应结果,并画图

进行对比说明。该实例的 MATLAB 源程序的部分清单如下,完整的程序请参考本书配套网络光盘中的“Chapter_2\E2_2\QuantArith.m”文件。

% QuantArith.m 文件的程序清单

x=[7/8 zeros(1,15)];

y=zeros(1,length(x)); %存放原始运算结果

Qy=zeros(1,length(x)); %存放未量化运算结果

Qy2=zeros(1,length(x)); %存放 2 bit 量化运算结果

Qy4=zeros(1,length(x)); %存放 4 bit 量化运算结果

Qy6=zeros(1,length(x)); %存放 6 bit 量化运算结果

%滤波器系数

A=0.5;

b=[1];

a=[1,A];

%未经过量化处理的运算

for i=1:length(x);

if i==1

y(i)=x(i);

else

y(i)=−A*y(i-1)+x(i);

end

end

%经过量化处理的运算

B=2; %量化位数

for i=1:length(x);

if i==1

Qy(i)=x(i);

Qy(i)=round(Qy(i)*(2^(B-1)))/2^(B-1);

else

Qy(i)=-A*Qy(i-1)+x(i);

Qy(i)=round(Qy(i)*(2^(B-1)))/2^(B-1);

end

end

Qy2=Qy;

%4 比特量化运算结果存放在 Qy4 中

---

%6 比特量化运算结果存放在 Qy6 中

---

%绘图

xa=0:1:length(x)-1;

plot(xa,y,'-',xa,Qy2,'--',xa,Qy4,'O',xa,Qy6,'+');

legend( '原系统运算结果', '2bit 量化运算结果', '4bit 量化运算结果', '6bit 量化运算结果')

xlabel( '运算次数'); ylabel( '滤波结果');图 2-8 为程序仿真运算结果,从仿真结果可以看出,在无限精度运算时,输出响应逐渐趋近于 0;在运算过程经量化处理后,输出响应在几次运算后形成固定值的来回振荡过程;量化位数越少,振荡的值越大。

2.4 FPGA 中的常用处理模块

2.4.1 加法器模块

加/减法器是 FPGA 设计中使用最为频繁的运算单元之一。根据加/减法器的实现结构,可分为串行加法器和流水线加法器,两种运算结构的差别在于所需硬件资源及运算速度的区别。在 FPGA 设计过程中,虽然也可以利用真值表、最基本的门电路、寄存器等单元搭建所需位数的加/减法器,但这种方法的效率显然不能满足工程设计的要求。 FPGA 设计中最常用的是多位二进制加/减法运算。最简单、最常用的方法是在程序文件中直接使用运算符“+”、“-”来完成相应的运算。

除了使用运算符完成相应运算外,另一种简便、实用、高效的方法是使用 Quartus 环境提供的加法器 IP 核。 Quartus II 提供的可用 IP 种类与所选的目标器件有关,一般来讲,器件的规模越大,所提供的 IP 种类越多。

Quartus II 提供了两种加/减法器 IP 核( ALTFP_ADD_SUB、 LPM_ADD_SUB),其中ALTFP_ADD_SUB 为浮点加/减法器运算 IP 核。本文仅介绍 LPM_ADD_SUB 核的基本使用方法,读者可以参考 IP 核的数据手册了解 ALTFP_ADD_SUB 的使用方法。

Altera 提供的加减法 IP 核可以方便用户生成所需要的加法器。用户可指定输入数据位宽、选择加减法运算方式等参数。启动 MegaWizard Plug-In Manager 工具后,依次选中“Arithmetic→LPM_ADD_SUB”,并设置好目标器件簇、输出文件中的语言模型、 IP 存放路径及名称后,单击“Next”按钮后进入加法器 IP 核参数设置界面,如图 2-9 所示,图中可以选择运算模式:加法( Addition only)、减法( Subtraction only)、加/减法( Create an

‘add_sub’input port to allow me to do both)。我们选择加法模式,输入数据位宽保持默认值

8bit,单击“Next”按钮进入如图 2-10 所示的界面。

在图 2-10 所示的界面中,用户可以设置输入数据是否为常数(constant),且可以设置

具体的常数值;界面还提供了输入数据是否为有符号数的选项。我们选择输入数据为变量

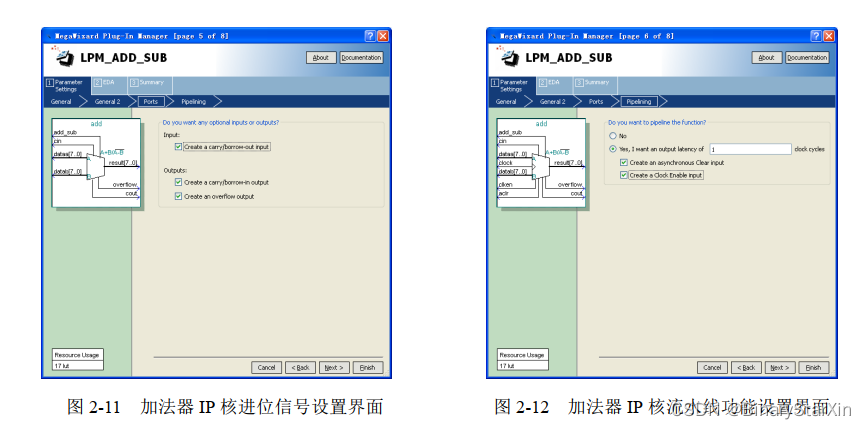

值(No, both values vary),同时选中“Signed”单选按钮,设置输入数据为有符号数。继续单击“Next”按钮进入加法器 IP 核参数设置的第 5 个页面,如图 2-11 所示。

在这个界面中,用户可以设置是否需要输入进位参与运算( Create a carry/borrow-out

input),是否需要提供溢出指示信号(Create a carry/borrow-out output)及进位信号(Create a

overflow output)。选种该页面的所有单选按钮,可以看到界面左侧的加法器 RTL 原理图中

增加了相应的信号接口。继续单击“Next”按钮进入加法器 IP 核参数设置的第 6 个页面,

如图 2-12 所示。

在这个页面中,用户可以设置加法器 IP 核的流水线运算模式。如果选择“No”单选按钮,则加法器是一个不带寄存器、时钟信号的纯粹逻辑功能运算单元;如果选择“Yes”单选按钮,则可以设置异步清零接口(aclr)、时钟允许接口(clken),以及流水线级数(output latency)。

至此,我们已完成了加法器 IP 核的主要参数设置,连续单击“Next”按钮直到完成所有设置界面。设置好 IP 核和各种参数后,双击“add.v”文件,打开生成的加法器 IP 核源代码,在文件编辑区中打开并查看 IP 核的对外接口信息。

module add (

aclr,

add_sub,

cin,

clken,

clock,

dataa,

datab,

cout,

overflow,

result);获取到 IP 核的模块声明后,直接在 Verilog HDL 文件中对模块进行实例化即可使用该IP 核。

2.4.2 乘法器模块

1.双输入乘法器运算核

乘法器是 FPGA 设计中大量使用的运算单元之一。 FPGA 设计中最简单、最常用的方法

是在程序文件中直接使用运算符“*”来完成相应的运算,但使用符号运算只能使用简单的乘法功能,不便于设置输入输出寄存器、流水线操作等功能。除了使用运算符完成相应运算外,另一种简便、实用、高效的方法是使用 Quartus II 环境提供的乘法器 IP 核。 Quartus II 提供了多种乘法器运算 IP 核,如 ALTFP_MULT(浮点数据 的 乘 法 运 算 )、 ALTMEM_MULT ( 基 于 存 储 器 结 构 的 常 系 数 乘 法 运 算 )、ALTMULT_ACCUM(乘法累加运算)、 ALTMULT_ADD(乘加运算)、 ALTMULT_COMPLEX(复数乘法运算),以及 LPM_MULT(常规乘法运算)。我们首先介绍 LPM_MULT 运算 IP 核的使用方法,而后介绍 ALTMULT_COMPLEX 的使用方法。

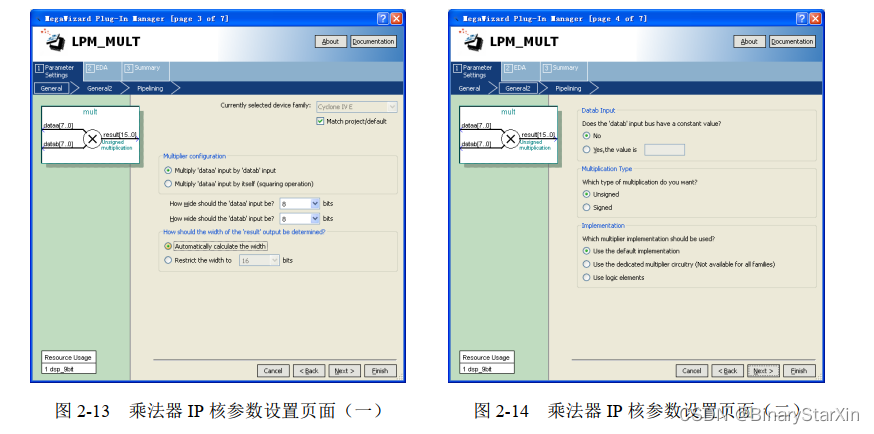

Altera 提供的乘法运算 IP 核可以方便用户生成所需要的乘法器,用户可指定输入数据位宽、运算流水线级数等参数。 LPM_MULT 运算 IP 核的数据位宽范围为 1~256 比特,支持有符号数及无符号数运算,支持流水线运算,提供异步清零及时钟允许信号等控制接口。启动 MegaWizard Plug-In Manager 工具后,依次选中“Arithmetic→LPM_MULT”,并设置好目标器件簇、输出文件中的语言模型、 IP 存放路径及名称后,单击“Next”按钮后进入乘法器 IP 核参数设置界面,如图 2-13 所示。

在 Multiply configuration 部分可以设置实现两个操作数的乘法(Multiply ‘dataa’ input by

‘datab’input) 或实现平方运算(Multiply ‘dataa’ input by itself); 可以设置输入数据的位宽(当

输入数据位宽均不大于 9 比特时, FPGA 采用 9 比特的乘法器 IP 核实现,否则采用 18 比特的乘法器 IP 核实现);可以设置输出数据位宽(通常保持默认值即可)。单击“Next”进入下一步数据参数设置界面,如图 2-14 所示。

在 Data Input 部分可以设置乘法操作数是否为常数;可以设置数据为有符号数(Signed)

或无符号数(Unsigned); 可以设置实现乘法运算的结构为专用乘法器 IP 核(Use the dedicated

Multiplier circuity)或逻辑单元(Use logic elements)。设置完后,继续单击“Next”按钮进

入第 5 个参数设置页面,如图 2-15 所示,在这一页面中,可以设置乘法运算的流水线级数

(output latency),以及 FPGA 实现时的优化策略是速度(Speed)还是面积(Area)。至此,

乘法器 IP 核的参数设置基本完成,持续单击“Next”按钮,进入第 7 步页面,如图 2-16 所

示,在这个页面中,用户可以选择 IP 核所需生成的文件种类,一般保持默认值即可,只生

成 Verilog HDL 语言的模块文件。

下面是乘法器 IP 核生成后的模块示例接口信息。

module mult (

clock,

dataa,

datab,

result);

2.复数乘法器运算核

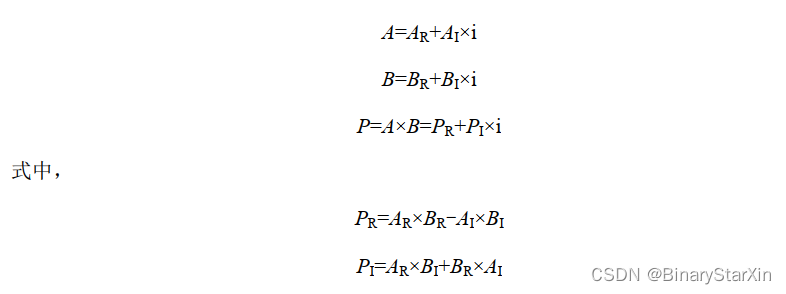

众所周知,两个复数的乘法运算,其实是四个定点数的相互运算结果,即

从上式可知,两个复数相乘,需要 4 个乘法器及两个加/减法器。 Quartus II 提供的复数乘法器 IP 核(LPM_COMPLEX)可根据用户的设置要求,设置输入数据的位宽及流水线等参数。

启动 MegaWizard Plug-In Manager 工具后,依次选中“Arithmetic→LPM_COMPLEX”,并设置好目标器件簇、输出文件中的语言模型、 IP 存放路径及名称后,单击“Next”按钮后即进入复数乘法器 IP 核参数设置界面,如图 2-17 所示。

如图 2-17 所示, 在 General 部分用户可以设置输入输出数据位宽, 在 Input Representation

部分,用户可以设置输入数据是否为有符号数;单击“Next”按钮进入第 4 个设置页面,如图 2-18 所示。在这个页面,用户可以设置运算的流水线级数,以及选择是否需要产生清零及时钟允许等接口信号。复数乘法器 IP 核的参数设置主要使用以上两个页面,从上述可知,其参数设置是比较简单的。

2.4.3 除法器模块

前面介绍加法器及乘法器运算时讲过, Verilog HDL 中实现相应操作可以使用运算符和IP 核两种方式。需要注意的是,这个规则在除法运算中是不成立的。在 Verilog HDL 中使用除法运算符“/”,综合工具会给出“错误”提示信息。Quartus II 提供了定点除法器运算 IP 核( LPM_DIVIDE)和浮点除法器运算 IP 核(ALTFP_DIV),接下来我们介绍 LPM_DIVIDE 运算 IP 核的使用方法。

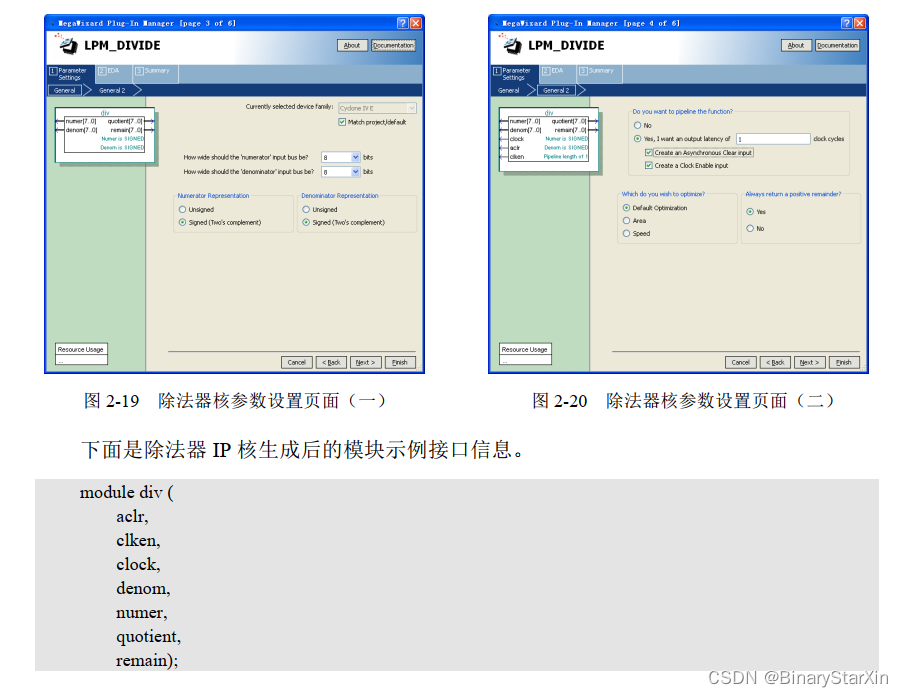

启动 MegaWizard Plug-In Manager 工具后,依次选中“Arithmetic→LPM_DIVIDE”,并设置好目标器件簇、输出文件中的语言模型、 IP 存放路径及名称后,单击“Next”按钮后即进入除法器 IP 核参数设置界面。

除法器 IP 核的参数设置界面主要有两个,如图 2-19 和图 2-20 所示。在图 2-19 所示的页面中用户可以设置输入数据的位宽,以及是否为有符号数;在图 2-20 所示的页面中用户可以设置运算的流水线级,以及选择是否需要产生清零及时钟允许等接口信号,同时还可以设置 FPGA 实现时的优化策略。如果选中 Always return a postive remanider 中的“Yes”单选按钮,则表示除法运算的余数始终保持为正数。从上述可知,除法器 IP 核的参数设置是比较简单的。

2.4.4 浮点运算模块

前面讲述加法器、乘法器、除法器模块时,均针对的是定点数运算。正如 2.1 节所讲的那样,浮点运算的复杂度及所需的逻辑资源,相比定点运算来讲要成倍地增加,也正因为如此, FPGA 设计时比较少使用浮点数据格式。当定点数据无法满足设计要求时,浮点数据格式依然是最好的,甚至是唯一的解决方式。使用浮点数据进行处理,难免会需要进行浮点格式的加、减、乘、除、开平方等基本的运算。前面所述的定点数据的乘、除、开平方等运算已经十分麻烦,所幸有 Quartus 提供的成熟 IP 核使用,否则真不知要耗费 FPGA 工程师多少汗水来实现这些基本的运算模块了!

Quartus II 提供了多种浮点运算 IP 核,如 ALTFP_ABS(浮点数据的取绝对值运算)、

ALTFP_ADD_SUB(浮点数据加减法运算)、 ALTFP_COMPARE(浮点数据比较运算)、

ALTFP_DIV(浮点除法运算)、 ALTFP_LOG(浮点取对数运算)、 ALTFP_MULT(浮点乘法

运算)等。

下面,我们以浮点加(减)法运算 IP 核为例,简要介绍浮点数据运算 IP 核的使用方法。启动 MegaWizard Plug-In Manager 工具后,依次选中“Arithmetic→ALTFP_ADD_SUB”,并设置好目标器件簇、输出文件中的语言模型、 IP 存放路径及名称后,单击“Next”按钮后即进入浮点加(减)器 IP 核参数设置界面,如图 2-21 所示。

在“What is the floating point format”部分,用户可以设置浮点数据的格式: 32 比特的

单精度数据(Single precision)、 64 比特的双精度数据(Double precision)或单精度扩展数

据(Single extended precision)。在“What is the output latency in clock cycles”部分可以设置

运算的流水线级数。在“Which operation mode do you want for the adder/subtractor”部分可

以设置 IP 核只完成加法运算(Additional only)、只完成减法运算(Subtraction only)或可根

据接口信号完成加(减)法运算(Create an ‘add_sub’ input port to do both)。

单击“Next”按钮进入下一步设置页面,如图 2-22 所示,这个页面仅用于设置用户所需的接口控制信号。继续单击“Next”按钮进入下一步设置页面,设置 FPGA 实现时的优化策略是速度优先(Speed)还是面积优先(Area)。