前言

为了帮助同学们完成痛苦的实验课程设计,本作者将其作出的实验结果及代码贴至CSDN中,供同学们学习参考。如有不足或描述不完善之处,敬请各位指出,欢迎各位的斧正!

很久没有写实验报告了,在这里非常感谢@m0_73880767同学提供的计算机组成原理实验指导书!你们的支持是我的最大动力!

请注意,该篇实验并非我在本科上该门课期间完成过的实验,而是于近期应同学要求补充的实验,由于时间较为久远,操作生疏,不一定保证实验结果一定正确,麻烦同学们自行甄辨,如操作不当或结果错误,还麻烦各位指正,以免误人子弟,谢谢!

一、实验目的

1、了解微程序控制器的组成原理及工作方式。

2、掌握微程序的编制及写入,观察微程序的运行。

二、实验内容

设计一个可自动运行的CPU电路,利用时序电路来产生指令执行所需的时间先后次序,通过微程序控制器来代替手动拨码开关的人工操作,在数据通路中完成程序的跳转重定向。

三、实验器件

1、存储器2764和计数器(74LS163、74LS192)。

2、D触发器(74LS74)、寄存器(74LS273)及移位寄存器(74LS194)。

四、实验原理

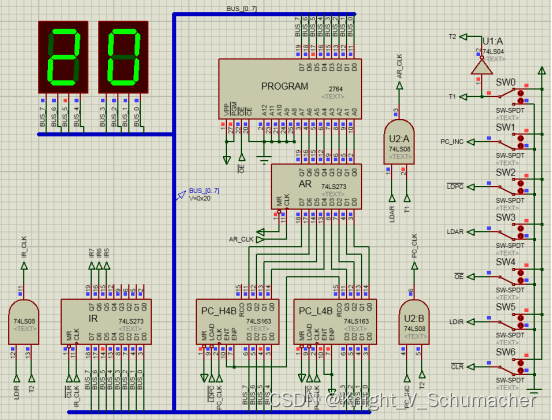

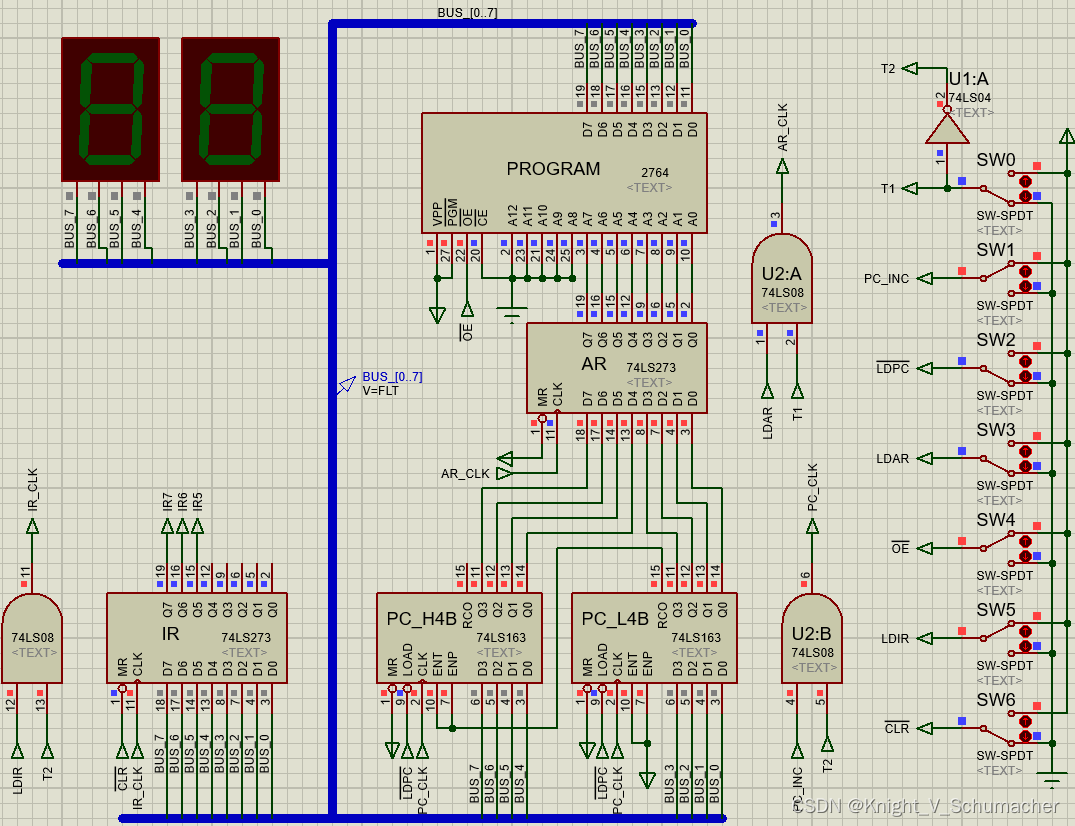

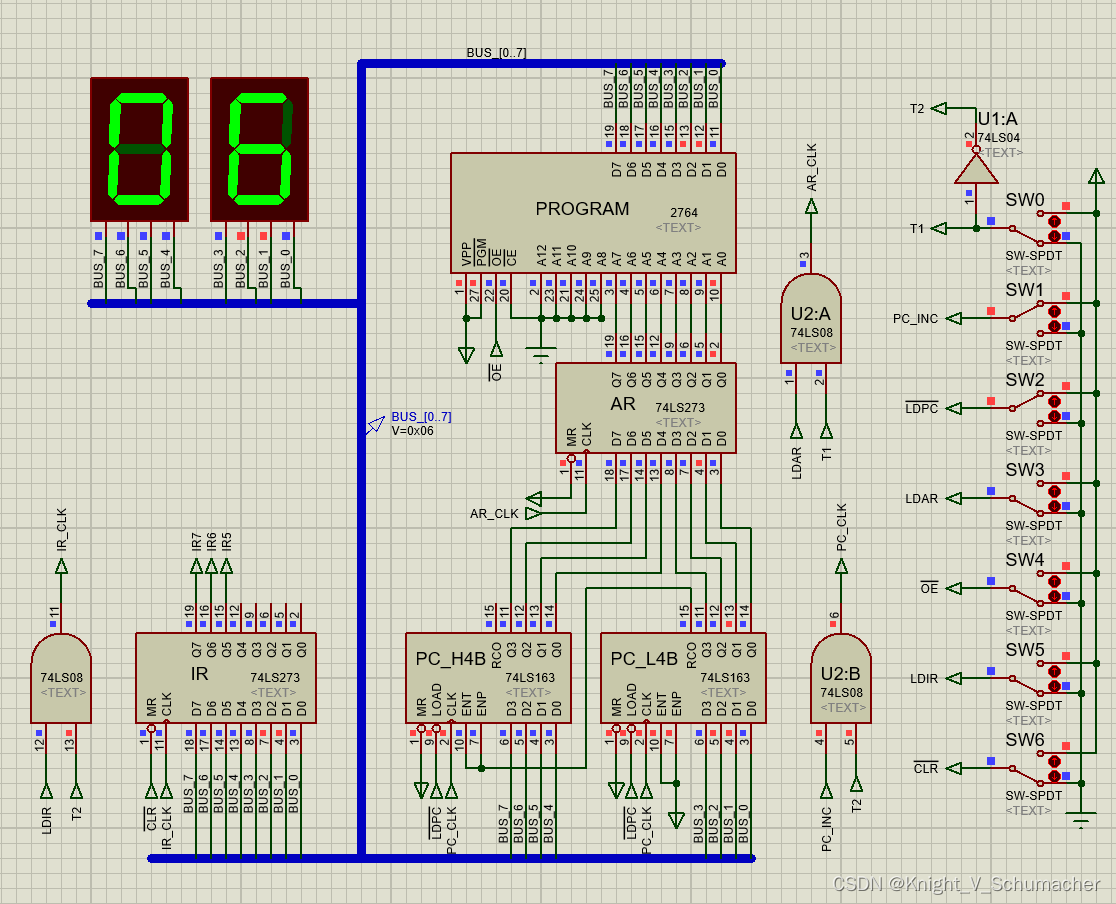

如图17所示,指令寄存器IR(74LS273)、程序计数器PC(74LS163)、存储器PROGRAM(2764)及其地址寄存器AR(74LS273)组成了一个“手动版”的数据通路。该通路是单总线结构(所有部件共用8位总线BUS,通过两个绿色数码管显示8位总线信息)和单存储器结构(即程序和数据共享存储器PROGRAM)。

在图17所示的数据通路中,程序计数器PC采用两个同步计数器74LSl63串联形成八位递增计数器,74LSl63的逻辑功能表如表9所示: D 0 D_0 D0、 D 1 D_1 D1、 D 2 D_2 D2、 D 3 D_3 D3为并行输入端; Q 0 Q_0 Q0、 Q 1 Q_1 Q1、 Q 2 Q_2 Q2、 Q 3 Q_3 Q3为并行输出端; E T E_T ET、 E P E_P EP为递增使能端;LOAD为置数端;MR为直接无条件清零端;CLK为时钟输入端;RCO为进位输出端(当 Q 3 − Q 0 Q_3-Q_0 Q3−Q0输出端递增溢出,则RCO=1)。值得注意的是:表9中所列74LS163全部功能都必须在CLK端上升沿跳变后才能实现。

| MR | L D L_D LD | E T E_T ET | E P E_P EP | 功能 | Q 0 Q 1 Q 2 Q 3 Q_0Q_1Q_2Q_3 Q0Q1Q2Q3 |

|---|---|---|---|---|---|

| 0 | × | × | × | 清除 | 0000 |

| 1 | 0 | × | × | 加载 | Q 0 Q 1 Q 2 Q 3 = D 0 D 1 D 2 D 3 Q_0Q_1Q_2Q_3=D_0D_1D_2D_3 Q0Q1Q2Q3=D0D1D2D3 |

| 1 | 1 | 0 | × | 保持 | Q 0 Q 1 Q 2 Q 3 Q_0Q_1Q_2Q_3 Q0Q1Q2Q3 |

| 1 | 1 | × | 0 | 保持 | Q 0 Q 1 Q 2 Q 3 Q_0Q_1Q_2Q_3 Q0Q1Q2Q3 |

| 1 | 1 | 1 | 1 | 自加1 | Q 0 Q 1 Q 2 Q 3 Q_0Q_1Q_2Q_3 Q0Q1Q2Q3状态码+1 |

数据通路的运行包括了两个阶段:取指周期(取出指令)和执行周期(执行取指周期取出的指令)。而总线BUS上的信息流动路径也相应分为指令流和数据流。指令流:取指周期,指令信息从存储器流向指令寄存器(即ROM->IR),实现指令译码;数据流:执行周期,数据信息从存储器流向唯一的指令执行部件PC(即ROM->PC),实现程序的重定向。值得注意的是,若有多个指令执行部件,则数据流还有不同的分支路径

因为数据通路只有PC作为唯一的执行部件,用以验证指令跳转的功能。所以如表10所示,本实验设计了空指令NOP、停机指令HLT和两条不同类型的跳转指令:相对寻址的JMP1指令和直接寻址的JMP2指令。

| 汇编助记符 | [OP码] I7 I6 I5 | 机器语言程序 | 指令说明 |

|---|---|---|---|

| JMP1,addr | 0 0 1 | 00100000; JMP1 xxxxxxxx; addr | 相对寻址:程序最终跳转到地址xxH执行 PC->xxH |

| JMP2,[addr] | 0 1 0 | 01000000; JMP2 xxxxxxxx;[addr] | 直接寻址:程序最终跳转到地址yyH执行 PC->yyH,yyH=[xxH] |

| HLT | 1 1 1 | 11100000; HLT | 硬件停机 |

| NOP | 0 0 0 | 00000000; NOP | “空”指令 ,不执行任何操作 |

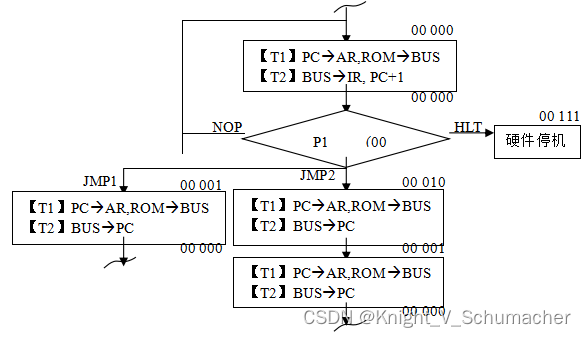

图18列出了上述四条指令的逻辑流程图,其中方框代表了从某个源部件经过总线BUS到达另一个目标部件的信息路径,菱形代表了指令译码结果(决定不同指令的跳转)。菱形之上的方框属于所有指令都必须经历的取指周期,而菱形之下各个分支代表了不同指令的执行周期。为了信息的稳定可靠传输,每一个方框都包含两个等长的节拍T1和T2。T1时刻,源部件的信息输出到总线BUS,所以AR_CLK上升沿有效,使得AR地址对应的ROM存储单元稳定输出信息到总线BUS;T2时刻,总线BUS上的信息输入到目标部件,所以PC_CLK和IR_CLK上升沿有效,使得总线BUS上的信息稳定打入到PC(重定向指令地址),或稳定打入到IR( 同时PC自加1)。

通过图18可以发现,所有跳转指令的逻辑流程图实际上仅需要由两种方框组成:在取指周期中出现的指令流{ROMIR}和在执行周期中出现的数据流{ROMPC}。JMP1和JMP2指令的区别仅仅在于JMP2指令做了递归操作,执行了两次相同的数据流{ROMPC}操作。而NOP指令和HLT指令比较特殊,只有取指周期,没有执行周期。指令译码后,NOP指令直接返回下一个取指周期,而HLT指令直接硬件停机。

为了完成指令流{ROMIR}和数据流{ROMPC},数据通路中需要根据一定的时序安排一系列的微操作信号来确保信息从某个部件输出到总线,再从总线输入到另一个部件。数据通路的操作信号说明如表11所示。值得注意的是:程序计数器PC、地址寄存器AR以及指令寄存器IR的各自锁存脉冲信号PC_CLK、AR_CLK及IR_CLK分别由PC_INC、LDAR及LDIR信号在T1或T2节拍形成的。所以,数据通路中实际需要的微操作信号只有:PC_INC、LDPC\、LDAR、OE\、LDIR和CLR\信号。

| 信号名称 | 作用 | 有效电平 |

|---|---|---|

| PC_CLK | 程序计数器PC的锁存脉冲信号 | 上升沿跳变有效 |

| PC_INC | T2节拍,PC_INC形成PC_CLK | 高电平有效 |

| LDPC\ | 程序计数器PC的加载信号 | 低电平有效 |

| AR_CLK | 地址寄存器AR的锁存脉冲信号 | 上升沿跳变有效 |

| LDAR | T1节拍,LDAR形成AR_CLK | 高电平有效 |

| OE\ | 存储器PROGRAM的读允许信号 | 低电平有效 |

| IR_CLK | 指令寄存器IR的锁存脉冲信号 | 上升沿跳变有效 |

| LDIR | T2节拍,LDIR形成IR_CLK | 高电平有效 |

| CLR\ | 指令寄存器IR的清零信号 | 低电平有效 |

指令流{ROMIR}和数据流{ROMPC}各自所需的微操作信号及其信息路径如表12所示,每个周期内微操作信号再与(T1,T2)节拍逻辑组合。如果把表11中的微操作信号用人工拨码开关来实现的话,实验者可以根据表12手动执行微操作信号,以T节拍为基准时钟,顺序依次实现指令逻辑流程图18中的各个方框,完成一条机器指令的执行。其中,实验者在菱形P1时刻,可以通过观测指令寄存器IR的{IR7,IR6,IR5}是否与某个指令的OP码相同,来判断不同指令所需的执行周期(即朝哪个分支继续执行)。

| 命令 | 微操作信号(工作节拍) | 功能 |

|---|---|---|

| 指令流ROM->IR | LDAR(T1), OE(T1&T2), LDIR(T2), PC_INC(T2) | 【T1】:PCAR,ROMBUS【T2】:BUSIR, PC+1 |

| 数据流ROM->PC | LDAR(T1), OE(T1&T2), LDPC(T1&T2),PC_INC(T2) | 【T1】:PCAR,ROMBUS【T2】:BUSPC |

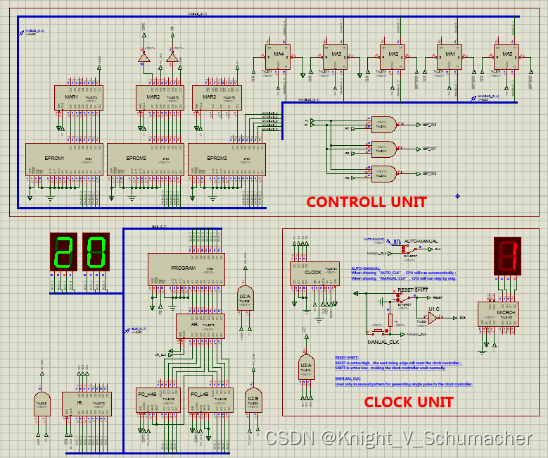

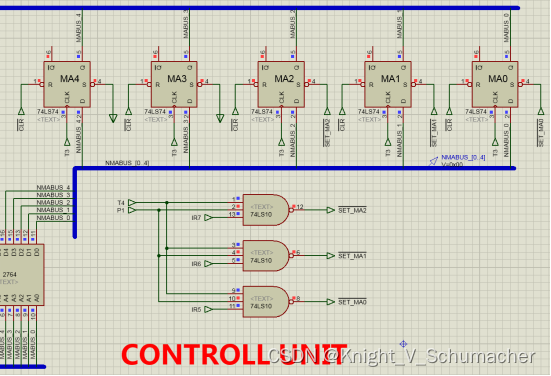

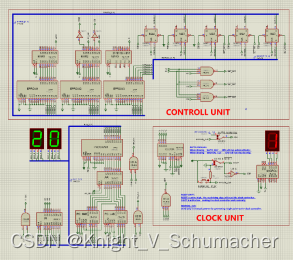

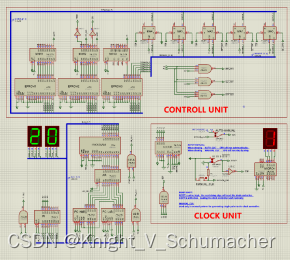

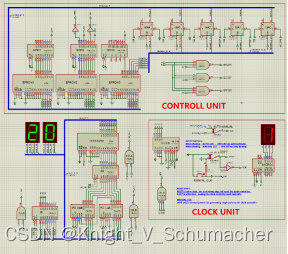

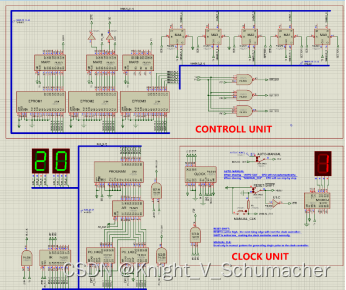

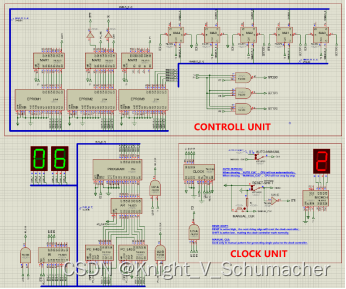

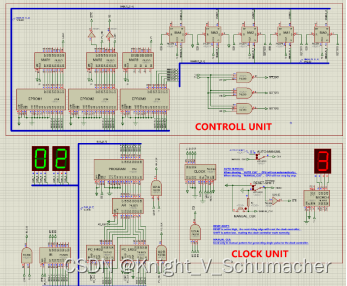

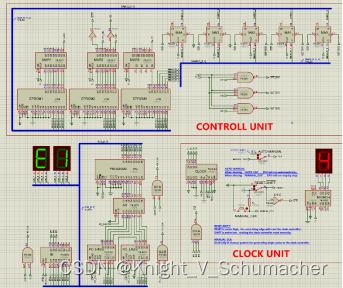

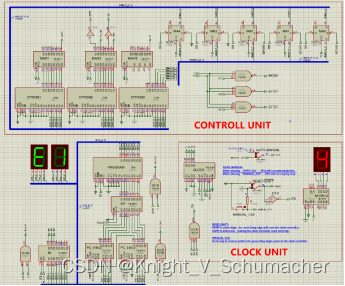

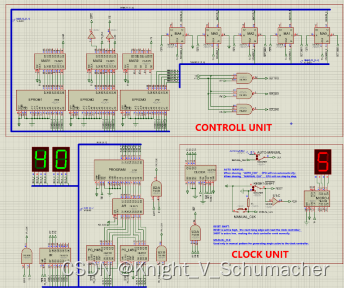

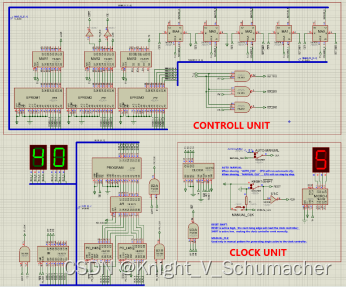

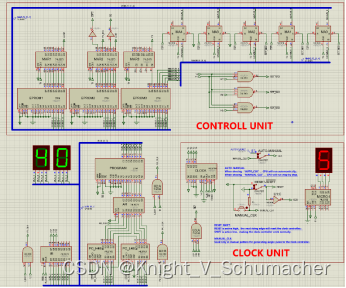

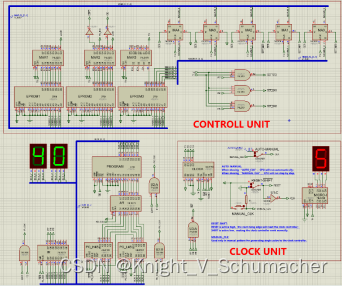

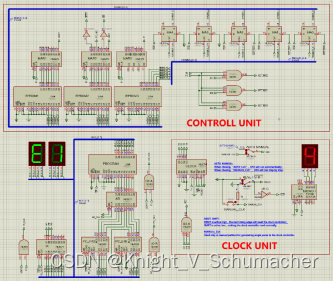

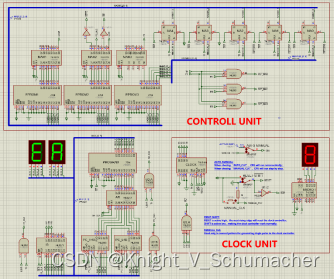

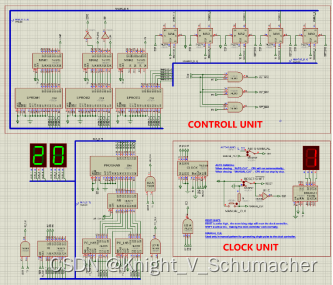

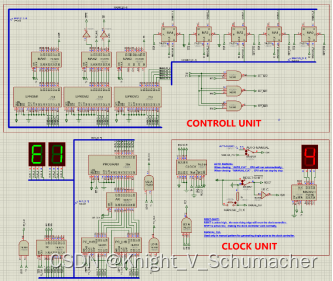

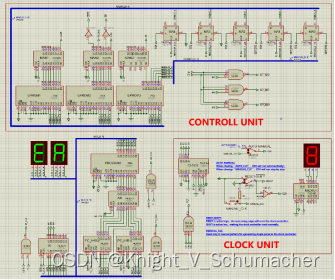

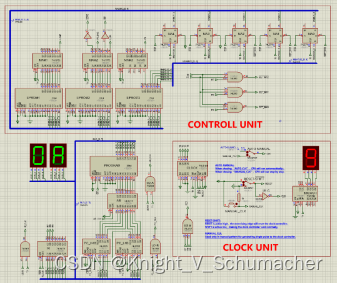

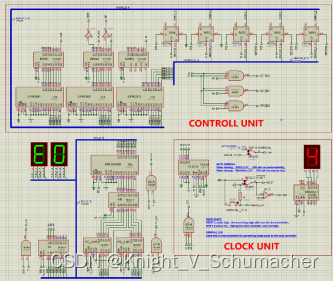

进而,我们可以将图17的“手动版”数据通路升级为“自动版”的CPU电路,如下图19所示。“自动版”CPU由数据通路、时序电路及微程序控制器三大部分组成:下方左边的数据通路保持不变,而上方红色框内的微程序控制器(CONTROL UNIT)取代了拨码开关及人工操作者;下方右边红色框内的时序电路(CLOCK UNIT) 则负责提供数据通路和微程序控制器依序运行所需的节拍序列{T1,T2,T3,T4}。

微程序控制器(CONTROL UNIT)的主要任务是完成当前指令的翻译和执行,即将当前存储器PROGRAM读出的指令转换成硬件逻辑部件工作的微操作信号序列,完成信息传送和各种处理操作。因此,微程序控制器将表11中的一条微操作信号视为一个微命令,而所有微命令的集合以并行二进制序列的形式构成微指令,如表13所示。

| 微代码 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 微命令 | LDAR | LDPC | \ | PC_INC | \ | \ | OE | \ | LDIR | \ | P1 | \ | uA4 | uA3 | uA2 | uA1 | uA0 |

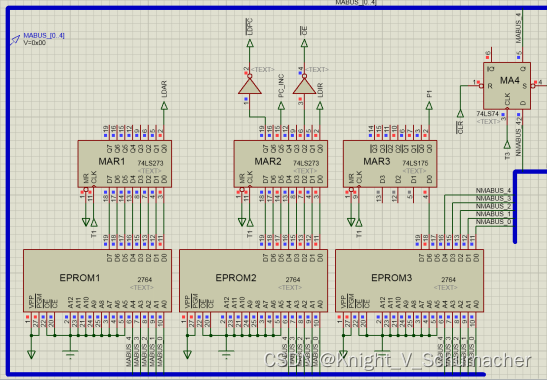

上表中的微指令字长24位,采用下址转移方式确定后续运行的微指令:微指令的1-5位表示顺序下一条微指令地址 [uA4-uA0];而 6-24位表示微命令集合(由于微指令18-24位没有对应的微命令,所以表13只显示了微指令1-17位)。所有微指令都存储在专用的控制存储器(CM)中,如图20所示:控制存储器24位,由3个ROM芯片2764组成。微命令寄存器18 位,由两个寄存器74LS273和一个4位触发器74LS175组成。

在指令逻辑流程图18中,一个方框对应一条特定的微指令,方框右上方是当前微指令在控制存储器CM中的地址,右下方是顺序下一条微指令地址[uA4-uA0]。若考虑方框右上方和右下方微指令地址的差异,在图18中总共有四种不同的方框,所以本实验的微指令代码表14所示。每条微指令的1-5位即下址字段[uA4-uA0],而6-24位是控制字段。

在T1节拍,上图20中的控制存储器把当前微指令打入微命令寄存器,微指令中所有标识为“1”的位表示执行了相应的微操作(且数据通路自动生成LDARAR_CLK),从而实现对应方框内的信息路径;反之,标识为“0”的位则代表没有执行对应的微操作。在T2节拍,数据通路自动生成了LDIRIR_CLK和PC_INCPC_CLK的后续操作。

| 微地址 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 00001 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 00010 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 00111 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

一条机器指令所经历的所有微指令(方框)组成的序列称为该机器指令的微程序,每条微指令包含了相同的取指周期微指令和各异的执行周期微指令序列。取指周期微指令地址必须是控制存储器CM首地址00000(因为系统启动时从首地址开始运行)。而菱形框 P1 (00 I7I6I5)是地址转移逻辑电路,当取指周期结束的时候,根据机器指令OP码的I7I6I5位进行译码,转入该机器指令对应的执行周期微指令序列的入口地址[00I7I6I5]。指令{NOP, HLT, JMP1, JMP2}的执行周期微指令序列的入口地址分别为{00000, 00111,00001,00010}。

在所有指令执行周期的微指令序列末尾,最后一条微指令的[uA4-uA0]都必须是取指微指令地址00000,即一条机器指令结束后必须返回公共的取指微指令,以便于取出下一条指令。而NOP指令因为取指后译码的执行指令入口地址仍为00000,直接指向下一条指令的取指周期微指令;所以NOP指令在取指后实际没有执行操作。

本实验微程序控制器的地址转移电路如图21所示,微指令地址寄存器五位(MA4-MA0),由触发器74LS74组成,均自带清“0”端和预置端。地址转移逻辑需要增加T3、T4节拍,T3时刻,当前微指令的后续微指令地址[uA4-uA0]打入微地址寄存器。T4时刻,若当前微指令不是取指周期微指令(即P1=0),则不执行任何操作,当前微地址转为顺序下一条微指令地址[uA4-uA0];若当前微指令是取指周期微指令(即P1=1),则图21中的地址转移逻辑电路根据指令寄存器IR的 I 7 I 6 I 5 I_7I_6I_5 I7I6I5位强制置位寄存器MA2-MA0,即修改当前微地址[uA2-uA0]位,转向该指令的执行周期微指令序列的入口地址[ 00 I 7 I 6 I 5 00I_7I_6I_5 00I7I6I5]。

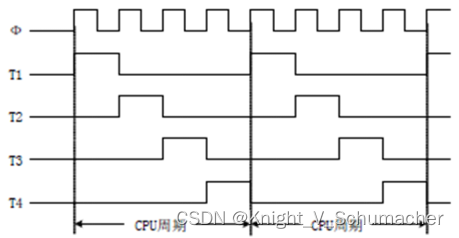

综上所述,一条微指令包括了4个节拍(T1、T2、T3、T4),其作用分别是:

T1:当前微指令的微操作信号使能;信息从源部件输出到总线BUS

T2:信息从总线BUS打入目的部件;程序计数器PC+1(取指周期微指令专用)

T3:微指令下址取址

T4:根据指令寄存器IR所存的指令OP码修改微指令下址 00 I 7 I 6 I 5 00I_7I_6I_5 00I7I6I5(取指周期微指令专用)

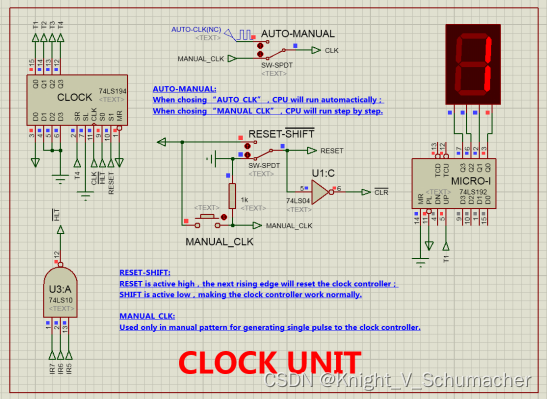

微程序控制器必须严格按照节拍时序来工作,所以时序电路的设计是非常重要的,本实验的时序电路如图23所示。CLK为全系统的基准时钟信号,可以由方波信号源AUTO_CLK提供(双击信号源可以自行选择方波信号频率),或者通过人工操作按键MANUAL_CLK手动步进;移位寄存器74LS194用来作为节拍生成器:当HLT=1且RESET=0,74LS194的状态{S0,S1}={1,0},74LS194的工作模式为右移。而 S R = T 4 S_R=T4 SR=T4使得 74LS194处于循环右移模式,以CLK为基准时钟,周而复始地发送4个基准时钟间隔的时序节拍T1-T4(T1->T4的一次循环即为一个微指令的运行周期,称为CPU周期),如图22所示:

为了便于观测微程序的运行,时序电路提供了微指令显示功能:一个由T1上升沿驱动的升序计数器74LS192,通过数码管显示当前运行第几条微指令。时序电路还提供了软件停机的“断点”功能(便于调试),即HLT指令:当指令寄存器IR的OP码 00 I 7 I 6 I 5 = 111 00I_7I_6I_5=111 00I7I6I5=111的时候,硬件逻辑生成HLT=0,此时74LS194的状态{S0,S1}={0,0},工作模式为保持,节拍时序状态静止在{T1,T2,T3,T4}={0,1,0,0},即停机在HLT指令的取指周期T2节拍上。

图23 微程序控制器实验的时序电路

此外,时序电路设置了RESET电路,用来初始化时序发生器74LS194,以及HLT指令停机后跳出“断点”。其“重启”的操作步骤如下:

1)RESET置1,则CLR=0,清零指令寄存器IR(指令OP码归零且HLT=1)和微地址寄存器MA4-MA0(微程序控制器从取指周期开始运行)。此时,74LS194的状态{S0,S1}={1,1},工作模式为送数。

2)手动按一次CLK,将{T1,T2,T3,T4}置位初始化值{1,0,0,0}。

3)RESET置0,74LS194恢复循环右移模式,进入第一条指令的取指周期节拍时序。

(注:若是HLT指令后操作,则进入HLT指令后续下一条指令的取指周期节拍时序)

五、 实验步骤

实验1:手动版程序通路运行

●在数据通路(手动版)的存储器PROGRAM中,烧写进去如下所示的机器语言程序文本(烧写ROM方法参见3.4存储器实验):

ORG 0000H

DB 00100000B; JMP1, 06H

DB 00000110B

DB 11101010B; HLT

DB 00001010B;

DB 00000000B

DB 00000000B

DB 00000010B; NOP/[ADDR]

DB 11100001B; HLT

DB 01000000B; JMP2, 06H->02H

DB 00000110B

END

● 在图17所示的数据通路(手动版)上,依据指令逻辑流程图18,手动拨码开关执行上述程序,观察每一步手工操作的结果(寄存器AR、IR、PC及总线BUS信息)。

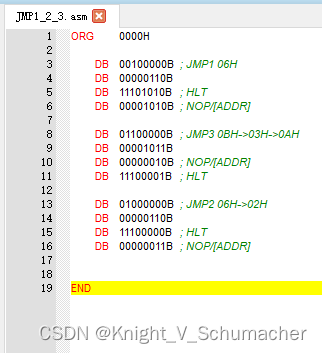

实验2:基于JMP1和JMP2指令的汇编程序

● 根据表14微指令代码表,将下列微程序分别烧写入5-20所示微程序控制器的控制存储器EPROM1、EPROM2及EPROM3(切记勿写错存储器!)。

EPROM1烧写内容

ORG 0000H

DB 00000001B

DB 00000001B

DB 00000001B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

EPROM2烧写内容

ORG 0000H

DB 00100101B

DB 10100100B

DB 10100100B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

EPROM3烧写内容

ORG 0000H

DB 01000000B

DB 00000000B

DB 00000001B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

● 启动仿真图19所示的微程序控制器实验电路,首先RESET=1,然后手动CLK一次,初始化74LS194节拍发生器{T1,T2,T3,T4}={1,0,0,0},最后RESET=0,恢复正常节拍时序。开始手动CLK单步执行上述实验1的机器语言程序。观察每一次单步执行的结果,例如寄存器AR、IR、PC及总线BUS信息。(注意程序进入HLT指令“断点”后需要重复上述初始化操作才能跳出“断点”)

● 依照上述启动初始化方法,在RESET=0恢复正常运行后,转为AUTO_CLK方波信号源自动CLK。当程序通路陷入“断点”时刻(HLT指令),查看寄存器AR、IR、PC、总线BUS信息及微指令周期数指示。

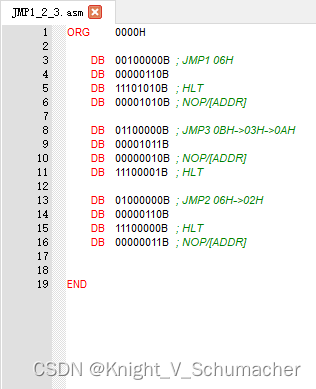

实验3:增加新指令JMP3

● 增加一条间接寻址的跳转指令JMP3,如下所示。请补充指令逻辑流程图18及微指令代码表14(新增的微指令地址定为00011),以实现JMP3指令。

| 汇编助记符 | OP码 | 机器语言程序 | 指令说明 |

|---|---|---|---|

| JMP3,[[addr]] | 01100000 | 01100000; JMP3 xxxxxxxx;[[addr]] | 间接寻址:程序最终跳转到地址 zzH, PC->zzH, zzH=[yyH], yyH=[xxH] |

●在图19所示微程序控制器实验电路的存储器PROGRAM中,烧写进去如下所示的机器语言程序文本(烧写ROM方法参见5.4存储器实验):

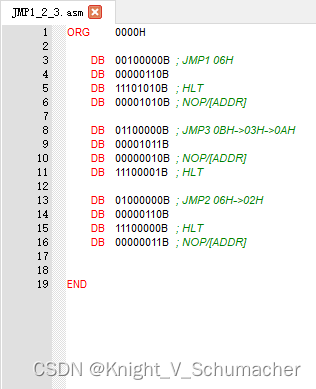

ORG 0000H

DB 00100000B; JMP1, 06H

DB 00000110B

DB 11101010B; HLT

DB 00001010B; NOP/[ADDR]

DB 01100000B; JMP3, 0BH->03H->0AH

DB 00001011B

DB 00000010B; NOP/[ADDR]

DB 11100001B ; HLT

DB 01000000B; JMP2, 06H->02H

DB 00000110B

DB 11100000B; HLT

DB 00000011B; NOP/[ADDR]

END

● 根据实验2所述方法,分别手动单步执行或AUTO_CLK自动执行实验3新的机器语言程序文本,观察单步执行或“断点”时刻的寄存器AR、IR、PC及总线BUS信息。

六、 实验结果

实验1:手动版程序通路运行

●在数据通路(手动版)的存储器PROGRAM中,烧写进去如下所示的机器语言程序文本(烧写ROM方法参见3.4存储器实验):

ORG 0000H

DB 00100000B; JMP1, 06H

DB 00000110B

DB 11101010B; HLT

DB 00001010B;

DB 00000000B

DB 00000000B

DB 00000010B; NOP/[ADDR]

DB 11100001B; HLT

DB 01000000B; JMP2, 06H->02H

DB 00000110B

END

● 在图17所示的数据通路(手动版)上,依据指令逻辑流程图18,手动拨码开关执行上述程序,观察每一步手工操作的结果(寄存器AR、IR、PC及总线BUS信息)。

电路启动:

首先,执行ROM->IR,可以发现其作用是将PC_H4B、PC_4BL的输出全置1:

此时由于AR输出依旧是0,所以如果关掉OE,其显示结果依旧是20

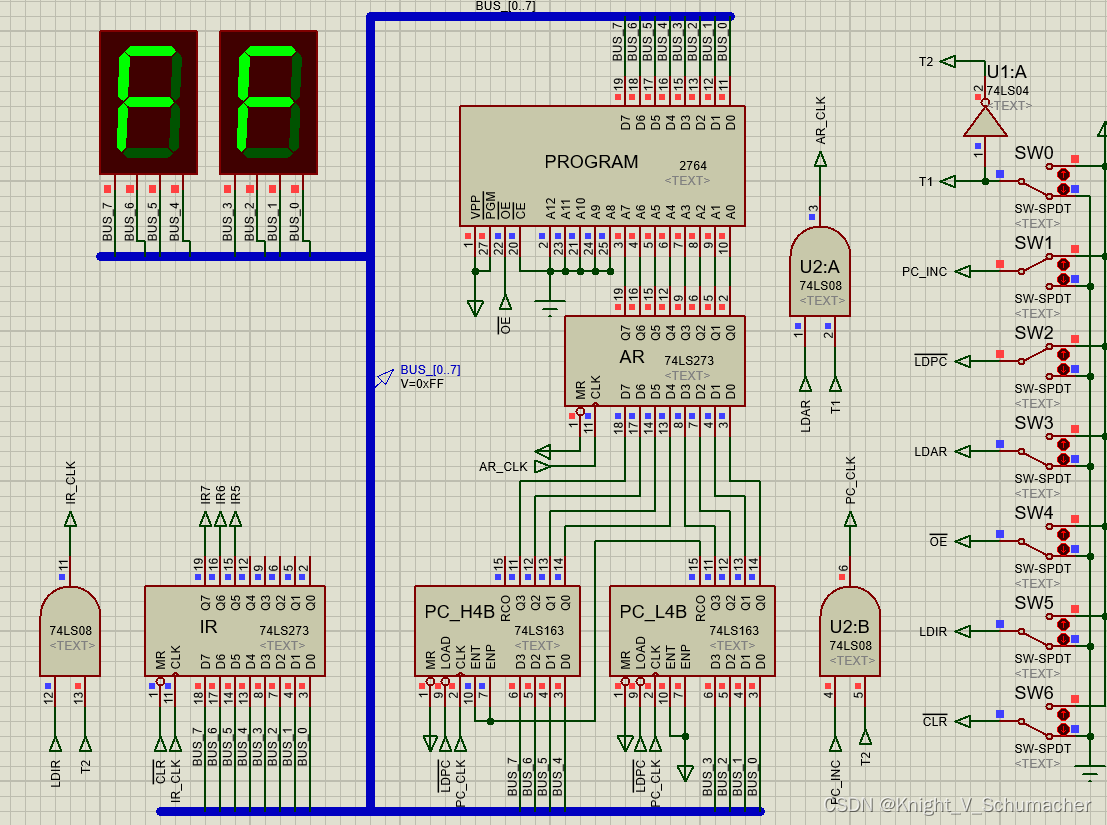

然后执行JMP1,也就是执行ROM->PC:

此时PC_H4B、PC_4BL的输出全置0,AR的输出全置1,导致PROGRAM的输入全置1,结果使PROGRAM的输出全置1:

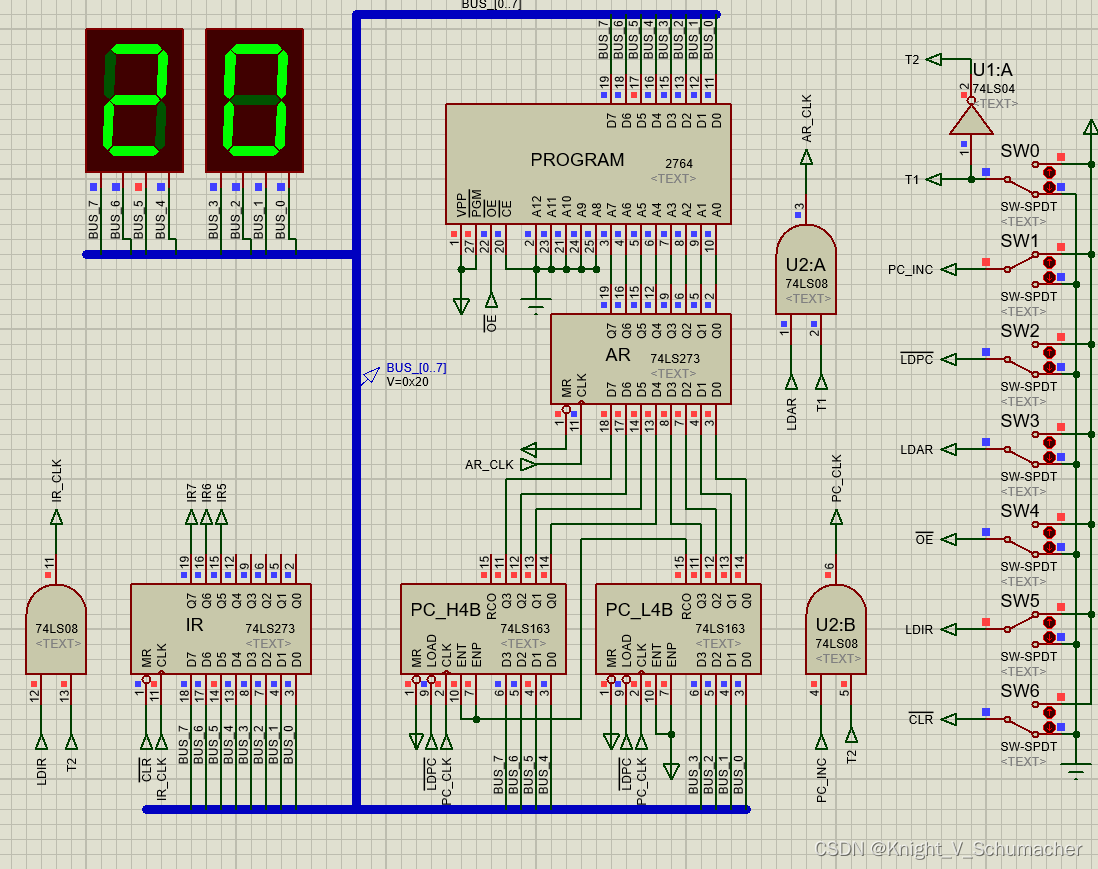

再度执行ROM->IR,将PC_H4B、PC_4BL的输出全置1,此时PROGRAM的输入、AR和PROGRAM的输出均置0,其显示结果回到20:

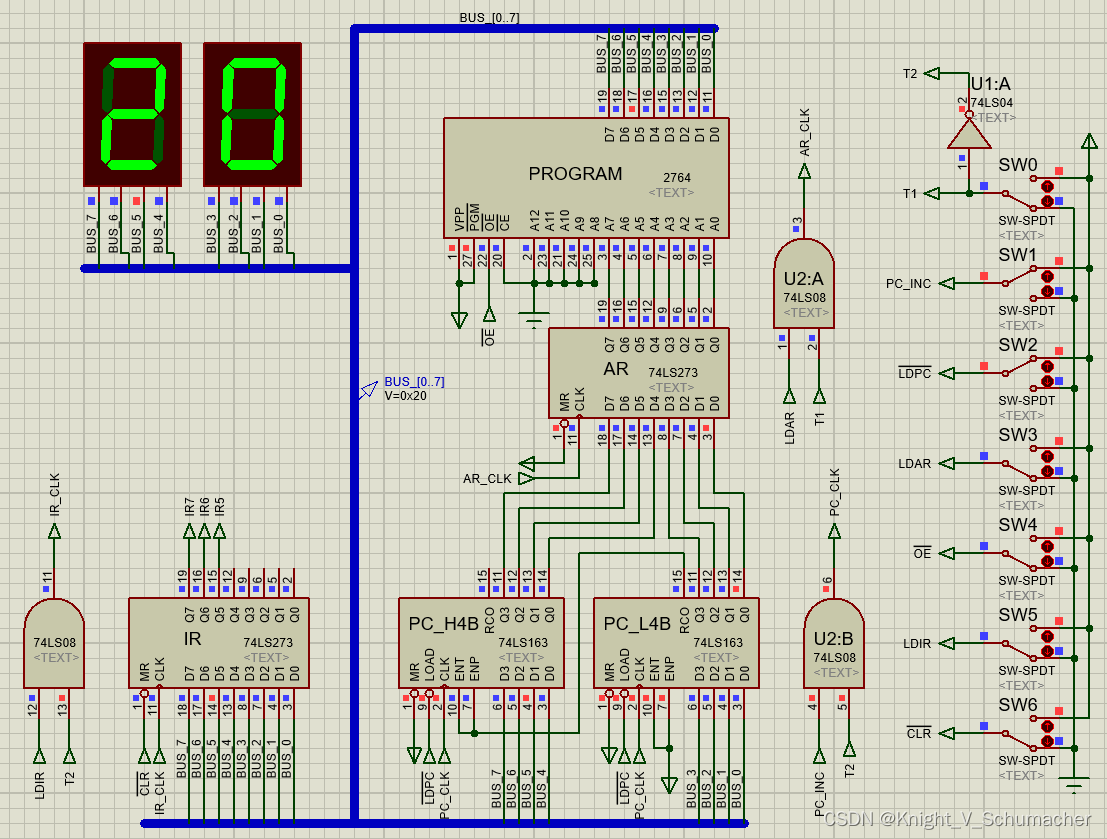

执行JMP2,也就是执行两次ROM->PC:

然后再执行一次ROM->IR:

综上所述,该实验的功能状态如下表所示:

综上所述,该实验的功能状态如下表所示:

| 指令流 | 任务 |

|---|---|

| ROM->IR | 将PC_H4B、PC_4BL的输出全置1 |

| ROM->PC | 将PC_H4B、PC_4BL的输出+1(首次执行时因溢出变为全0) |

| 指令 | 状态 |

|---|---|

| 开机 | 20 |

| JMP1 | FF |

| JMP2 | 06 |

每一步手工操作的结果(寄存器AR、IR、PC及总线BUS信息)如下表所示:

| - | - | AR | IR | PC | BUS |

|---|---|---|---|---|---|

| 取指周期 | T1 | 00H | 00H | 00H | 20H |

| 取值周期 | T2 | 00H | 20H | 01H | 20H |

| 执行周期 | T1 | 01H | 20H | 01H | 06H |

| 执行周期 | T2 | 01H | 20H | 06H | 06H |

实验2:基于JMP1和JMP2指令的汇编程序

● 根据表14微指令代码表,将下列微程序分别烧写入5-20所示微程序控制器的控制存储器EPROM1、EPROM2及EPROM3(切记勿写错存储器!)。

EPROM1烧写内容

ORG 0000H

DB 00000001B

DB 00000001B

DB 00000001B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

EPROM2烧写内容

ORG 0000H

DB 00100101B

DB 10100100B

DB 10100100B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

EPROM3烧写内容

ORG 0000H

DB 01000000B

DB 00000000B

DB 00000001B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

DB 00000000B

END

● 启动仿真图19所示的微程序控制器实验电路,首先RESET=1,然后手动CLK一次,初始化74LS194节拍发生器{T1,T2,T3,T4}={1,0,0,0},最后RESET=0,恢复正常节拍时序。开始手动CLK单步执行上述实验1的机器语言程序。观察每一次单步执行的结果,例如寄存器AR、IR、PC及总线BUS信息。(注意程序进入HLT指令“断点”后需要重复上述初始化操作才能跳出“断点”)

-

RESET=1,手动CLK一次,初始化74LS194节拍发生器{T1,T2,T3,T4}={1,0,0,0}

-

RESET=0,恢复正常节拍时序。开始手动CLK单步执行上述实验1的机器语言程序。观察每一次单步执行的结果,例如寄存器AR、IR、PC及总线BUS信息

下表为每一步执行后的寄存器AR、IR、PC及总线BUS信息:

| AR | IR | PC | BUS |

|---|---|---|---|

| 0x00 | 0x00 | 0x00 | 0x20 |

| 0x00 | 0x20 | 0x01 | 0x20 |

| 0x01 | 0x20 | 0x01 | 0x06 |

| 0x01 | 0x20 | 0x06 | 0x06 |

| 0x06 | 0x20 | 0x06 | 0x02 |

| 0x06 | 0x02 | 0x07 | 0x02 |

| 0x07 | 0x02 | 0x07 | 0xE1 |

| 0x07 | 0xE1 | 0x08 | 0xE1 |

● 依照上述启动初始化方法,在RESET=0恢复正常运行后,转为AUTO_CLK方波信号源自动CLK。当程序通路陷入“断点”时刻(HLT指令),查看寄存器AR、IR、PC、总线BUS信息及微指令周期数指示。

| AR | IR | PC | BUS | 微指令周期数 |

|---|---|---|---|---|

| 0x07 | 0xE1 | 0x08 | 0xE1 | 4 |

| 0x02 | 0xEA | 0x03 | 0xEA | 8 |

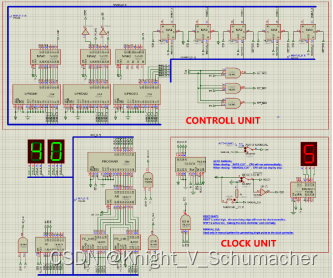

实验3:增加新指令JMP3

● 增加一条间接寻址的跳转指令JMP3,如下所示。请补充指令逻辑流程图18及微指令代码表14(新增的微指令地址定为00011),以实现JMP3指令。

| 汇编助记符 | OP码 | 机器语言程序 | 指令说明 |

|---|---|---|---|

| JMP3,[[addr]] | 01100000 | 01100000; JMP3 xxxxxxxx;[[addr]] | 间接寻址:程序最终跳转到地址 zzH, PC->zzH, zzH=[yyH], yyH=[xxH] |

●在图19所示微程序控制器实验电路的存储器PROGRAM中,烧写进去如下所示的机器语言程序文本(烧写ROM方法参见5.4存储器实验):

ORG 0000H

DB 00100000B; JMP1, 06H

DB 00000110B

DB 11101010B; HLT

DB 00001010B; NOP/[ADDR]

DB 01100000B; JMP3, 0BH->03H->0AH

DB 00001011B

DB 00000010B; NOP/[ADDR]

DB 11100001B ; HLT

DB 01000000B; JMP2, 06H->02H

DB 00000110B

DB 11100000B; HLT

DB 00000011B; NOP/[ADDR]

END

● 根据实验2所述方法,分别手动单步执行或AUTO_CLK自动执行实验3新的机器语言程序文本,观察单步执行或“断点”时刻的寄存器AR、IR、PC及总线BUS信息。

下表为“断点”时刻(HLT指令),寄存器AR、IR、PC、总线BUS信息及微指令周期数:

| AR | IR | PC | BUS | 微指令周期数 |

|---|---|---|---|---|

| 0x0A | 0xE0 | 0x0B | 0xE0 | 4 |

| 0x02 | 0xEA | 0x03 | 0xEA | 8 |

| 0x03 | 0x00 | 0x03 | 0x0A | 9 |

七、思考题

- 如图19所示的微程序控制器实验电路中,如果采用微命令来实现HLT指令(例如安排控制存储器中一位作为HLT\信号)是否可行?请修改电路试验。

- 在实验2和实验3的机器语言文本中,有部分地址标示“NOP/[ADDR]”,为何相同位置会有不同的执行效果?在什么情况下执行到该处是NOP指令(顺序滑过)?什么情况下执行到该处是打入PC的地址(跳转)?

- 本实验的控制存储器CM最多可容纳多少条微指令?而指令体系最多可容纳多少条机器指令?微指令容量和指令容量各自是由于什么因素限定的?

- 假设只用两个2764芯片作为控制存储器,节拍脉冲精简到三个脉冲(T1-T3),请问微程序怎么改?机器语言程序需要改么?请修改电路试验。