概述

本篇主要是一些关于PCIe的一些问题的汇总,这篇文章想到哪写到哪,可能在顺序上不太友好,本人接触PCIe的时间也不长,有很多东西还不清楚,还在持续的学习中,希望和大家一起进步,不好的地方请见谅。有问题也欢迎在评论留言一起讨论。

这篇文章也会持续的添加问题。

问题汇总

1.Bar0一定是第一个使用的Bar吗

通过之前的学习我们知道枚举驱动对BAR的操作必须是顺序执行的,即先BAR0,然后BAR1,……,直到BAR5。当软件检测到那些被硬件设置为全0的BAR,则认为这个BAR没有被使用。无论是PCI还是PCIe,都没有明确规定,第一个使用的BAR必须是BAR0。事实上,只要设计者原意,完全可以将BAR4作为第一个BAR,并将BAR0~BAR3都设置为不使用。

2. 有哪些PCIe设备是多功能设备

每个PCIe device最多存在8个Function,当Function数量大于1时就称为多功能设备,具有多功能的PCIe设备并非是所有设备的通用特性,大部分的PCIe设备都是单功能设备;

常见的多功能设备有:

- 网络适配器:某些高性能网络适配器可以提供多个虚拟网络接口功能,每个功能都可以独立运行,实现多个网络连接。

- RAID控制器:某些RAID控制器可以具有多个独立的功能,每个功能可以控制一个独立的RAID阵列。这意味着单个RAID控制器可以管理多个独立的硬盘阵列。

- 显卡:一些高性能显卡可能具有多个显示输出功能。每个功能可以驱动一个独立的显示器,实现多显示器配置。

- 多端口串行卡:某些串行接口卡可以具有多个独立的串口功能。每个功能可以与不同的设备进行通信。

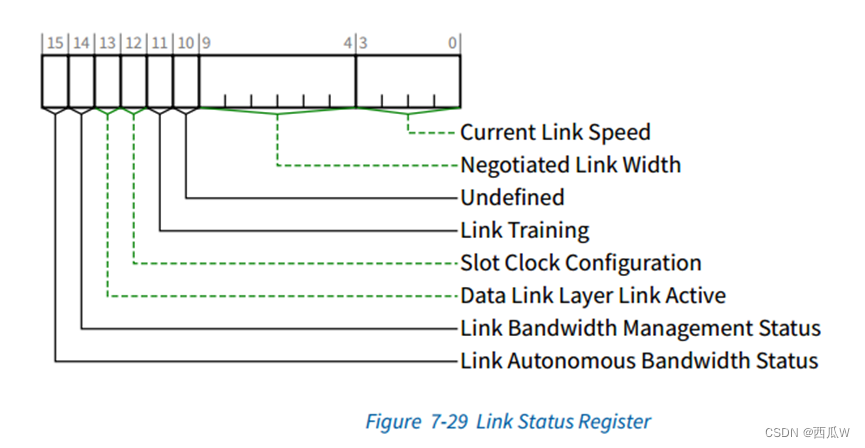

4.如何知道当前设备的训练状态

如何能知道当前设备的Link速率、line num呢

可以通过读取PCI Express Capability Structure,PCI capability ID为0x10,通过查询手册可知道当前的速率和line。

5.关于PCI域地址和存储器域地址的关系

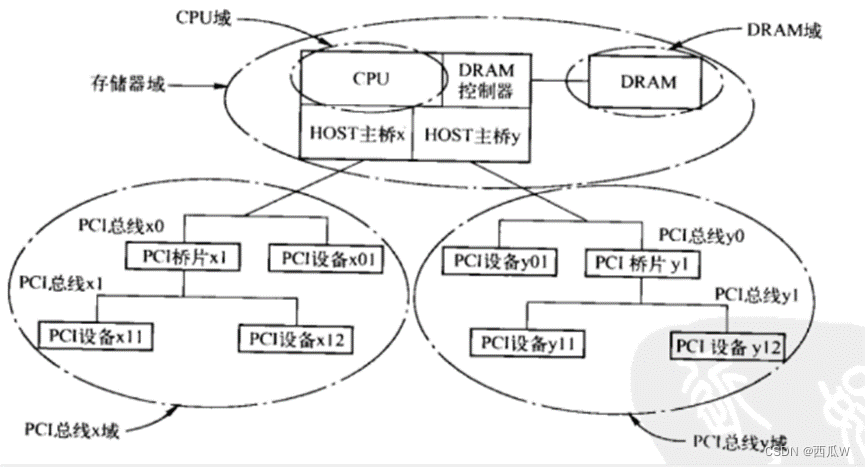

上图所示的处理器系统由一个CPU,一个DRAM控制器和两个HOST主桥组成。在这个处理器系统中,包含CPU域、DRAM域、存储器域和PCI总线域地址空间。其中HOST主桥x和HOST主桥y分别管理PCI总线x域与PCI总线y域。PCI设备访问存储器域时,也需要通过HOST主桥,并由HOST主桥进行PCI总线域到存储器域的地址转换;CPU访问PCI设备时,同样需要通过HOST主桥进行存储器域到PCI总线域的地址转换。

在一个处理器系统中,CPU所能访问的PCI总线地址一定在存储器域中具有地址映射;而PCI设备能访问的存储器域的地址也一定在PCI总线域中具有地址映射。有些处理器提供了寄存器进行这种地址映射,如PowerPC的inbound和outbound寄存器组,(PowerPC的RapidIO总线域地址映射也是通过inbound和outbound寄存器组来管理)。有些处理器没有提供类似寄存器,但存储器域与PCI总线域的转换始终存在。

后续会持续更新该文章,欢迎补充。