行为仿真Behavioral_Simulation

行为仿真:应该在设计流程的每个阶段进行行为模拟,以避免在设计周期的早期出现错误。

文章目录

前言

目标:

1、确定行为模拟的好处

2、对设计进行行为模拟

3、验证设计的功能

仿真是在软件环境中模拟真实设计行为的过程。仿真有助于通过注入刺激和观察设计输出来验证设计的功能Vivado支持不同类型的仿真,例如行为仿真、结构仿真和时序仿真。其中,行为模拟是最常用的。行为模拟对设计建模具有最高级别的抽象。与其他仿真方法相比,它的运行速度更快,但提供的设计信息最少。它不需要计时信息来验证设计的语法和功能。行为模拟证实了设计是按要求运行的。它必须在设计流程的早期阶段进行。它通常在源文件或预合成设计上执行。预合成设计可以包括HDL测试台或仅用于仿真的HDL源文件。行为模拟还有助于在系统实际执行之前确定设计的效率。

提示:以下是本篇文章正文内容,下面案例可供参考

一、寄存器传输层的行为模拟

通常执行RTL模拟是为了验证代码语法并确认代码是否按预期运行。在这一步中,设计主要用RTL描述,因此不需要时序信息。除非设计包含实例化的设备库组件,否则RTL模拟不是特定于体系结构的。为了支持实例化,Xilinx提供了UNISIM库。

将最初的设计创作限制在行为代码中可以:(1)更具可读性的代码(2)更快更简单的仿真(3)代码可移植性(迁移到不同设备系列的能力),(4)以及代码重用(使用相同代码的能力)

测试台是一个虚拟环境,用于检查设计的功能正确性。测试台架通常是不可合成的,因为它包含定时信息,比如不能合成到硬件中的延迟。测试台可能很复杂,因为它可能包括子例程调用、从外部文件读取的刺激和条件刺激。测试台架有几个组件,如(1)内部信号、(2)UUT实例化、(3)输入刺激(包括时钟信号)和(4)输出监控部分,输出监控部分以可读和用户友好的格式报告输出。测试台的主要用途是(1)初始化设计,(2)实例化被测单元(即UUT),并将一系列测试值应用于输入;也就是说,为UUT生成刺激。您还可以通过检查其输出来检查设计的功能。该测试台可用于测试同一电路的多种实现。它是作为HDL文件编写的,通常是用于设计验证的仿真模型。

二、Vivado Simulator

1.Vivado Simulator支持VHDL, Verilog, SystemVerilog和混合VHDL/Verilog或VHDL/SV设计的功能和时序模拟

拥有的功能:

- 源代码调试(例如,步骤、断点和当前值显示)

- 用于时序模拟的标准

- 延迟文件注释

- 值变化转储转储

- 用于功率分析和优化的交换活动交换格式转储

- 本机支持硬IP块(如串行收发器和PCle®块)

- 多线程编译混合语言(例如,VHDL、Verilog或SystemVerilog设计构造)

- 一键模拟重新编译

- 重新启动一键编译

- 仿真对模拟库的内置

- 支持实时波形更新

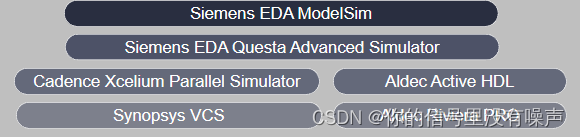

2.支持第三方来仿真

Vivado Design Suite与第三方仿真工具兼容。使用第三方工具的仿真可以直接在Vivado IDE中运行,也可以使用自定义的外部仿真环境运行。这里显示了Vivado Design Suite支持的不同第三方模拟器。

在使用第三方仿真工具模拟设计之前,必须编译库并将逻辑库名称映射到物理库位置。

要使用Vivado IDE编译库,您需要转到Tools并选择compile Simulation libraries。然后选择所需的选项,如目标模拟器、语言、库类型和设备系列。编译simlib Tcl命令可用于自动执行此任务。compile_simlib这个Tcl命令提供了许多选项,包括目标模拟工具、语言、体系结构等等。

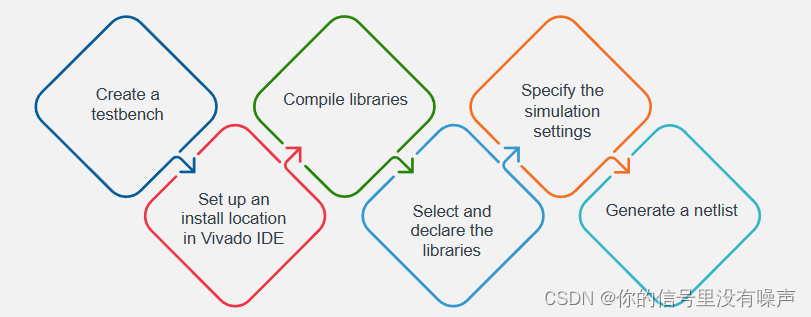

3.仿真前准备工作

创建一个反映您想要运行的模拟操作的测试台架。在Vivado IDE中设置一个安装位置(如果不使用Vivado模拟器)。编译您的库(如果没有使用Vivado模拟器)。选择并声明需要使用的库。指定仿真设置(如目标模拟器、仿真顶层模块名称、顶层模块[待测设计]),显示仿真集,定义编译、细化、仿真、网表、高级选项。生成一个网表(如果执行合成后或实现后模拟)。

4.仿真设置

Vivado设计套件支持第三方模拟器。这些第三方模拟器包括Mentor Graphics、Synopsys和Cadence模拟器。Vivado模拟器支持VHDL、Verilog等语言,或者这两种语言的混合。您还可以设置模拟默认运行时。要使用Vivado模拟器启动模拟,可以使用launch_simulation Tcl命令。导出仿真Tcl命令export_simulation创建第三方工具的仿真脚本。

使用Vivado模拟器中的波形,您可以分析设计并调试代码。模拟器将填充其他工作空间窗口,例如Objects和Scope窗口。通常,仿真是在定义了要模拟的HDL对象的测试台中进行的。“源”窗口将仿真源显示在具有“层次”的层次树中。IP源,库和编译顺序viHDL作用域是分层分区。每当您实例化一个设计单元或声明一个进程、块、包或子程序时,您就创建了一个作用域。“对象”窗口显示与“范围”窗口所选范围关联的HDL仿真对象。在调用时,模拟器默认打开一个波窗口。波窗口显示由仿真停止模块中可跟踪的HDL对象组成的新波配置。

总结

1、行为模拟可以用来验证设计的功能

2、一个testbench是验证设计正确性的重要组件

3、模拟设置可以配置为使用第三方模拟器(使用TCL也可以调用:launch_simulation/export_simulation;记得提前编译仿真库:complie_simlib)