前言

最近所作课题需要将工程中所有寄存器提取出进行后处理,这里记录一下提取工程寄存器的流程。

一、工程Hierarchy树状图

首先需要明白一点,直接从RTL代码提取reg信号作为寄存器是不对的,因为在代码中存在各种例化,所以提取的寄存器数量是不正确的。

为了能够正确提取中实际综合后的寄存器,我们需要得到工程综合后的Hierarchy层级。这一步可以在VCS综合后,在Verdi中进行导出。

右键其中一个模块,点击Export Hierarchy,即可导出。

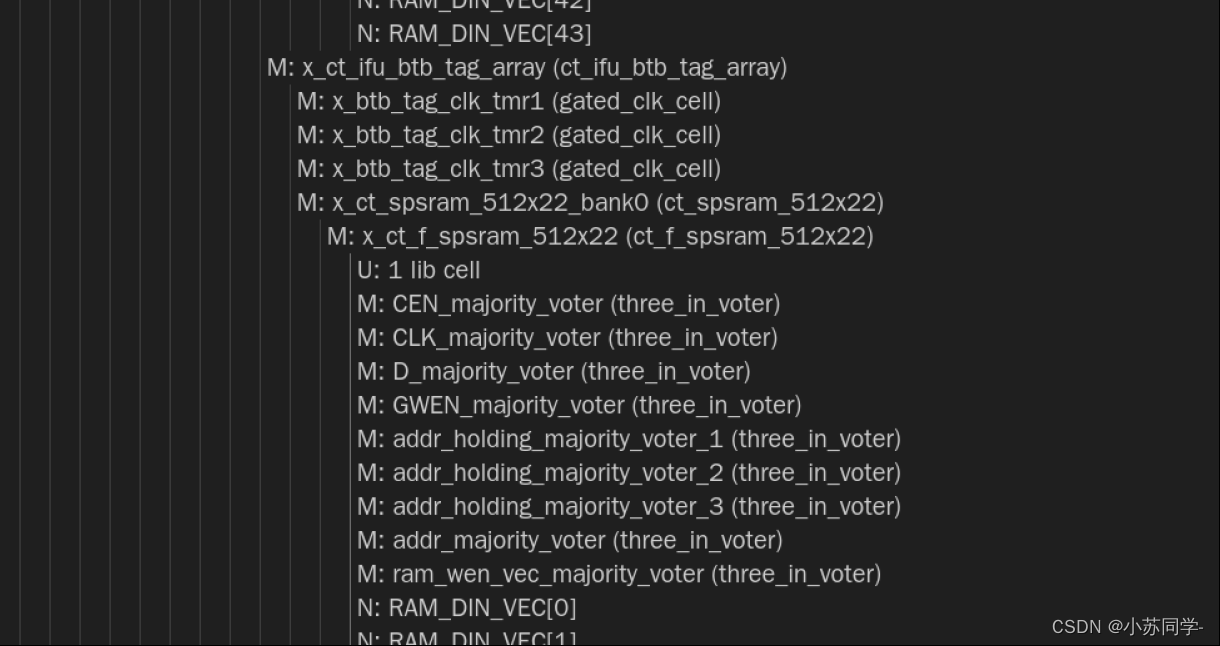

可以看到生成的Hierarchy层级图如下:

二、重构工程

1.重构Hierarchy树状图

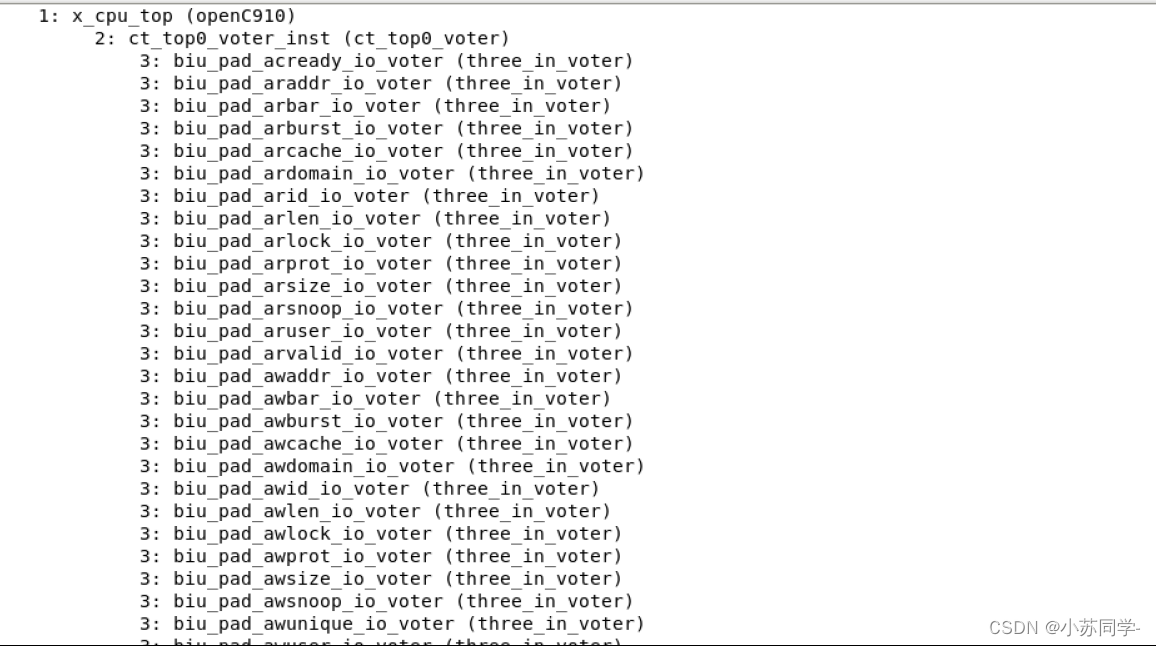

得到上述树状图,使用脚本提取的时候还有些困难,所以重新构建一下树状图。

具体原理是按照层级结构,使用脚本将M或N替换为1-9。

python3 replace.py如下图进行转化:

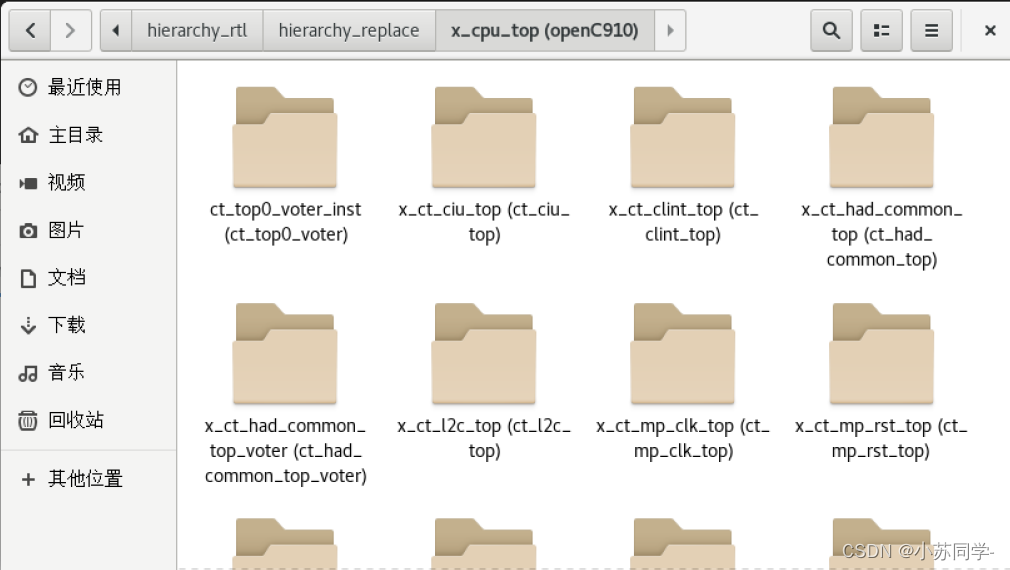

2.重构文件夹

根据重构后的树状图,生成带有Hierarchy层次结构的文件夹结构。

python3 mkdir.py如下图,可以看到文件名由例化名字和源module名字所组成:

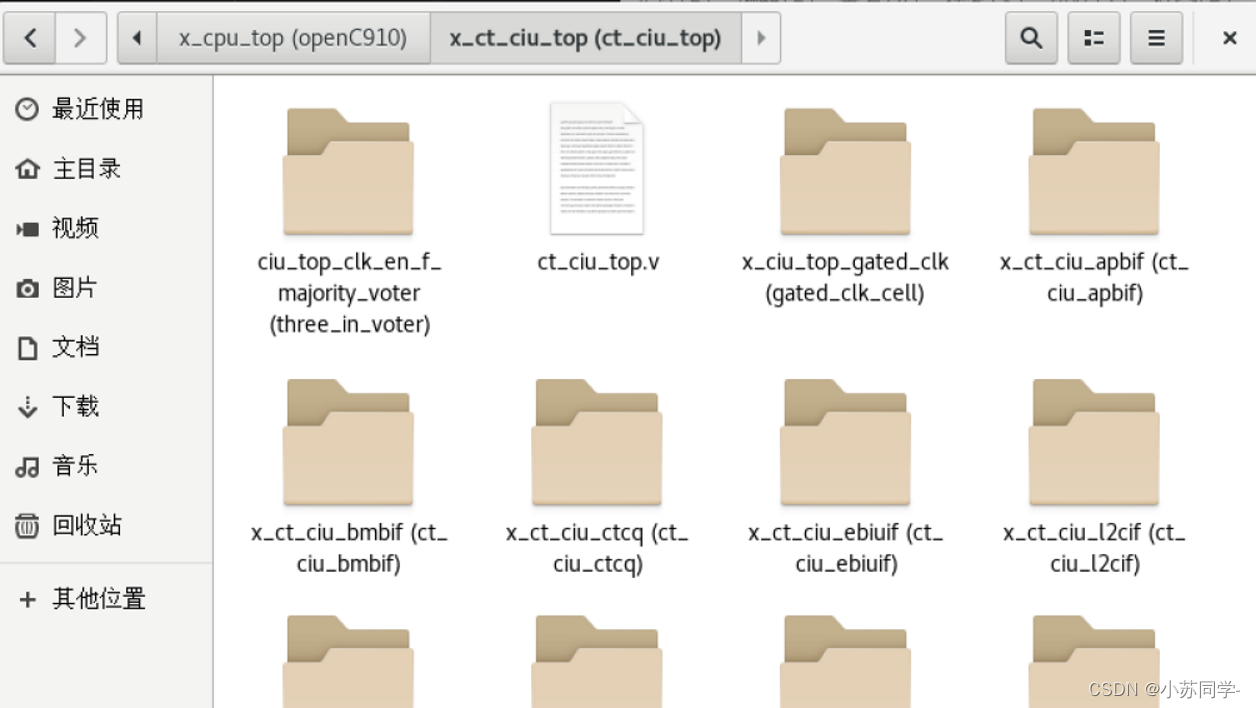

3.mv RTL代码

将工程中的RTL代码进行提取,匹配module名与括号内名字,将相对应的RTL代码放入指定文件夹中。

python3 mv_rtl2folder.py可以看到,脚本将对应的RTL代码放入了与其Module相对应的文件夹中。

三、提取寄存器

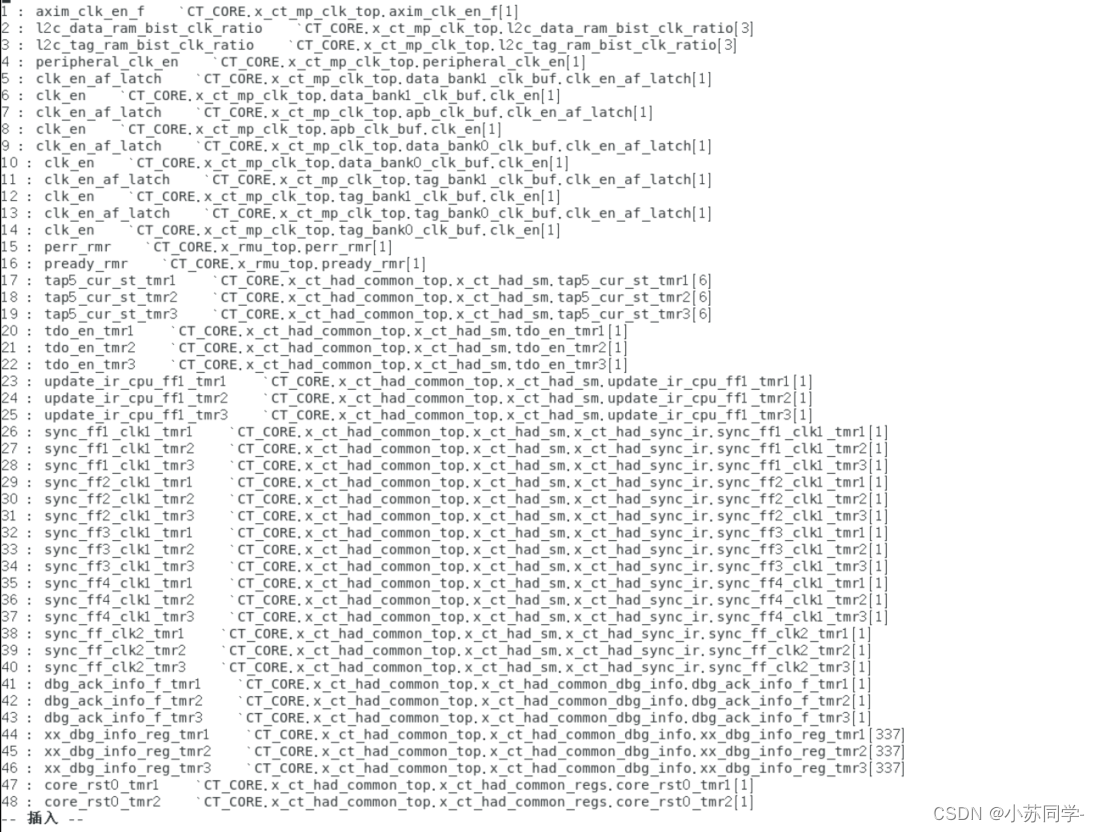

根据自己需求,将寄存器提取出,我的目的是在顶层将其作为信号引出,以及统计寄存器的数量,所以生成如下:

这里需要注意寄存器名字可能会重复,为了解决重复性问题,在脚本中加入自检模块,会将重复信号检测到,并按照顺序末尾补count,已解决重复性的问题。